ゲート接地増幅回路のゲイン

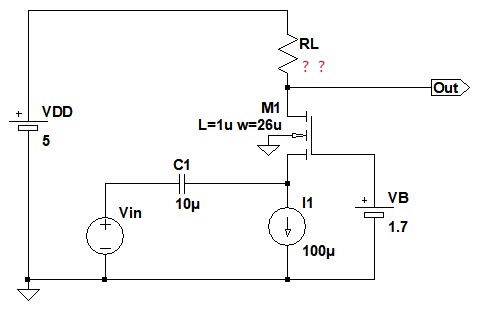

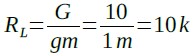

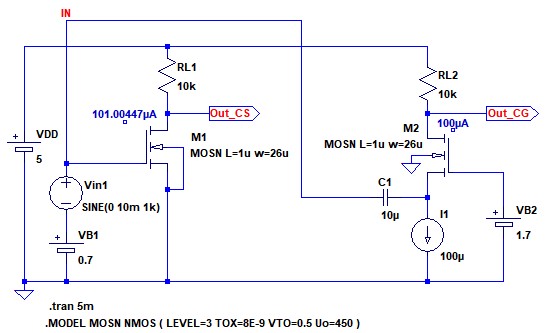

図1は,NchMOSトランジスタを使用したゲート接地増幅回路です.電源(VDD)電圧は5Vで,ソースに100μAの定電流源が接続されています.また,ゲートは,1.7Vのバイアス電圧源(VB)に接続されています.そして,コンデンサ(C1)を介して入力信号源(VIN)が接続されています.使用しているMOSトランジスタのゲート長(L)は1μmで,ゲート幅(W)は26μmとなっています.このゲート接地増幅回路に1kHzの信号を入力し,ゲインが20dBとなる負荷抵抗(RL)の値は,次の(A)~(D)のどれでしょうか.

ただし,入力信号源の出力抵抗は十分小さいものとし,また,MOSトランジスタの特性は,スレッショルド電圧(VTH)が0.5V,キャリア移動度(μ)が450cm2/(V*s),単位面積あたりのゲート容量(COX)が430nF/cm2とします.

ゲインが20dBとなる負荷抵抗(RL)の値は?

ゲインが20dBとなる負荷抵抗の値を求めるためには,まずMOSトランジスタのgmの値を計算する必要があります.MOSトランジスタのgmは,L,W,ID,μ,COXから計算することができます.gmが求まれば,あとは簡単な計算でゲインが20dBとなる負荷抵抗の値が求まります.

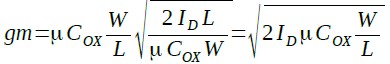

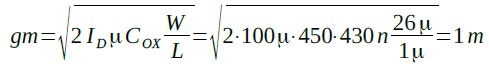

ゲート接地増幅回路のMOSトランジスタのgmは,gm=√(2IDμCOXW/L)で計算することができます.これは図1の定数では約1mSになります.そしてゲインが20dB(10倍)となる負荷抵抗の値は,ゲインをgmで割ったものになり,10/1m=10kΩとなります.したがって正解は(B)の10kΩということになります.

●ゲート接地増幅回路のgmを求める

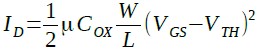

ゲート増幅回路は,図1のようにゲートの電圧が固定されており,ソースに入力信号を加えます.入力信号によりソースの電圧が変化すると,ゲート・ソース間電圧が変化し,ドレイン電流が変化します.このゲート・ソース間電圧の変化による,ドレイン電流変化の割合がgmです.ゲート・ソース間電圧(VGS)とドレイン電流(ID)の関係は式1のようになっています.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

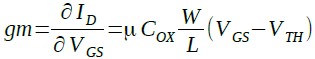

「IoT時代のLTspiceアナログ回路入門 010 ソース接地増幅回路のゲイン」で解説したように,この式1を,式2のようにVGSで微分したものがgmです.

・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・(2)

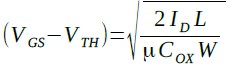

ソース接地増幅回路の場合,ゲート・ソース間電圧の値が与えられていましたが,ゲート接地増幅回路の場合,条件として与えられているのは,ソース電流(ドレイン電流)の値です.そこで,式1を式3のように,ドレイン電流に対するゲート・ソース電圧の式に変形します.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

そして,式2の(VGS-VTH)に,式3の右辺を代入したものが式4になります.

・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・(4)

式4を使用することで,ドレイン電流からMOSトランジスタのgmを計算することができます.図1の定数でのgmは,式5のように1mSになります.

・・・・・・・・・(5)

・・・・・・・・・(5)

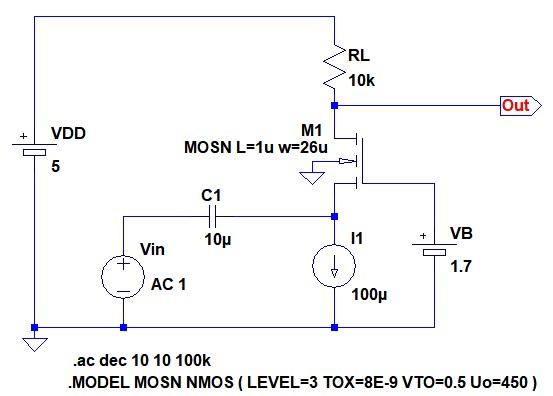

●gmから負荷抵抗を求める

増幅回路のゲイン(G)は,gmに負荷抵抗の値を掛けたものです.したがって,ゲインから負荷抵抗の値を求める式は式6のようになります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

図1のgmの値は,式5のように1mSなので,ゲインを20dB(10倍)とするためには,式7のようにRLを10kΩにすればよいことが分かります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

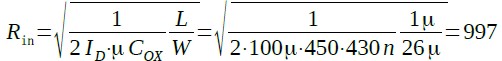

図2は,RLの値を10kΩとしてゲインをシミュレーションするための回路図です.トランジスタ・モデルは,VTHが0.5V,キャリア移動度(μ)が450cm2/(V*s),単位面積あたりのゲート容量(COX)が430n F/cm2となるよう,パラメータを設定しています.

ゲインが20dBとなるよう,負荷抵抗の値は10kΩとしている.

図3は,図2のシミュレーション結果です.1kHzでのゲインは,設計値の20dBとなっていることが分かります.

1kHzでのゲインは,設計値の20dBとなっている.

●ゲート接地増幅回路の入力抵抗

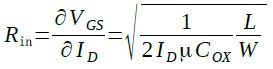

ゲート接地増幅回路は,ソース端子に入力を加えるため,入力抵抗が小さくなります.この入力抵抗は,入力に微小電流ΔIを加えたときの電圧変化ΔVから「Rin=ΔV/ΔI」として求めることができます.入力に微小電流ΔIを加えたときのドレイン電流の変化をΔIDとすると,入力端子の電圧変化はゲート・ソース電圧の微小変化ΔVGSとなり,入力抵抗(Rin)は式8のように求めることができます.

・・・・・・・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・・・・・・・(8)

この入力抵抗(Rin)は,式4のgmの逆数となっています.また,この入力抵抗は「IoT時代のLTspiceアナログ回路入門 012 ドレイン接地増幅回路のゲイン」で計算した,ドレイン接地回路の出力抵抗と同じものです.図1の定数を代入すると,式9のように約1kΩになります.

・・・・・・・・・(9)

・・・・・・・・・(9)

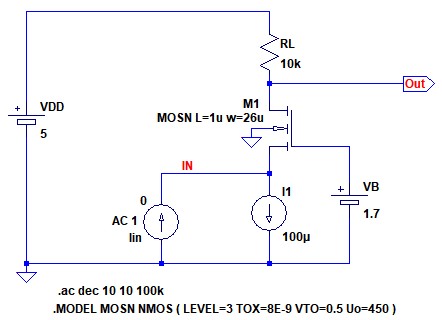

図4は,ゲート接地増幅回路の入力抵抗をシミュレーションするための回路です.入力となる小信号電流源(Iin)をソースに接続しています.

入力となる小信号電流源(Iin)をソースに接続している.

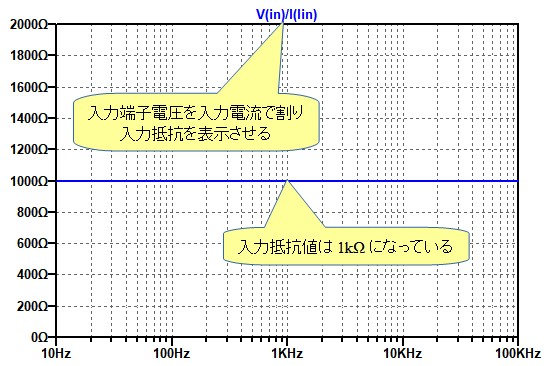

図5は,図4のシミュレーション結果です.入力抵抗を表示するために,入力端子の電圧(VIN)を入力電流I(Iin)で割っています.図5より入力抵抗は計算値と同じ1kΩとなっていることが分かります.このように,ゲート接地増幅回路は入力抵抗が小さいため,入力として出力抵抗の大きな信号源を使用すると,入力端子で信号が減衰し,所望のゲインが得られないことがあります.

入力抵抗は計算値と同じ1kΩになっている.

●ソース接地増幅回路とゲート接地増幅回路の入出力の位相

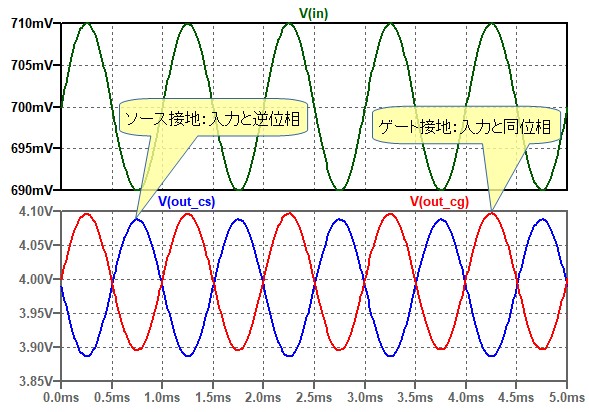

図6は,ソース接地増幅回路とゲート接地増幅回路の,入出力の位相関係を比較するための回路図です.入力信号としてピーク電圧10mVの正弦波信号を加えます.また,それぞれのMOSトランジスタのドレイン電流を回路図上に表示しています.ソース接地増幅回路は入力信号が+側に振れるとドレイン電流が増加し,負荷抵抗の電圧降下が増加します.そのため,出力振幅は-側に振れ,入力信号と出力信号の位相は反転したものになります.一方,ゲート接地増幅回路では,入力信号が+側に振れるとドレイン電流が減少し,負荷抵抗の電圧降下は減少します.そのため,出力振幅は+側に振れ,入力信号と出力信号の位相は同位相となります.

入力信号としてピーク電圧10mVの正弦波信号を加えている.

図7が図6のシミュレーション結果です.上段が入力信号で下段が出力信号となっています.どちらも出力振幅はほぼ同じで,ピーク電圧100mV程度となっており,ゲインは約10倍(20dB)であることが分かります.また,ソース接地増幅回路の出力は入力信号とは逆位相となっており,ゲート接地増幅回路は同位相となっています.

以上,ゲート接地増幅回路について解説しました.ゲート接地増幅回路は入力抵抗が小さいため,通常の増幅回路としては使用上の制約が多いのですが,ソース接地増幅回路と組み合わせ,カスコード増幅回路として広く使用されています.カスコード増幅回路は,出力抵抗の増加による高ゲイン化や高周波特性の改善などの特徴があります.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice4_014.zip

●データ・ファイル内容

CG_amp.asc:図2の回路

CG_amp_RIN.asc:図4の回路

CS_CG_amp.asc:図6の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs