ドレイン接地増幅回路のゲイン

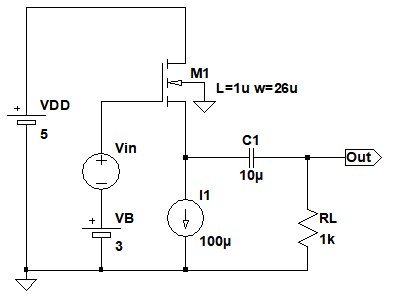

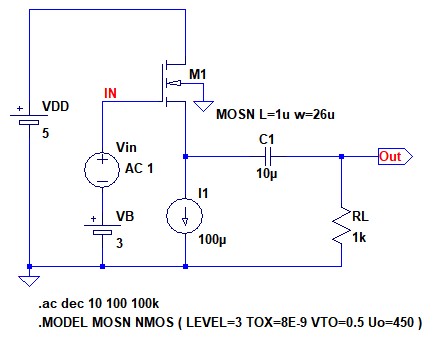

図1は,NchMOSトランジスタを使用したドレイン接地増幅回路です.電源(VDD)電圧は,5Vでソースに100μAの定電流源が接続され.さらに,コンデンサ(C1)を介して1kΩの負荷抵抗(RL)が接続されています.使用しているMOSトランジスタのゲート長(L)は,1μmでゲート幅(W)が26μmとなっています.また,ゲート・バイアス電圧(VB)は3Vです.このドレイン接地増幅回路のゲートに1kHzの微小信号を加えたとき,Out端子までのゲインは,次の(A)~(D)のどれでしょうか.

ただし,このMOSトランジスタの特性は,スレッショルド電圧(VTH)が0.5V,キャリア移動度(μ)が450cm2/(V*s),単位面積あたりのゲート容量(COX)が430nF/cm2とします.

負荷抵抗の接続されたドレイン接地増幅回路のゲインを求めるためには,出力インピーダンスがいくつになっているかを考える必要があります.ドレイン接地増幅回路の出力インピーダンスは,MOSトランジスタのドレイン電流から計算することができます.ドレイン電流とソース電流は等しいため,ドレイン電流の値は,定電流源I1の値と同じです.

図1のドレイン接地増幅回路で,負荷抵抗が接続されていない場合,ソース端子の電圧はゲート端子の電圧に応じて変化するため,ゲインは0dBとなります.負荷抵抗が接続された場合は,ドレイン接地増幅回路の出力抵抗と,負荷抵抗で入力信号を分圧したものが出力となります.図1の定数の場合,出力抵抗は1kΩとなります.負荷抵抗の値が1kΩなので,分圧比は0.5となりゲインは-6dBになります.つまり,正解は(D)になります.

●負荷抵抗を接続しないドレイン接地増幅回路のゲイン

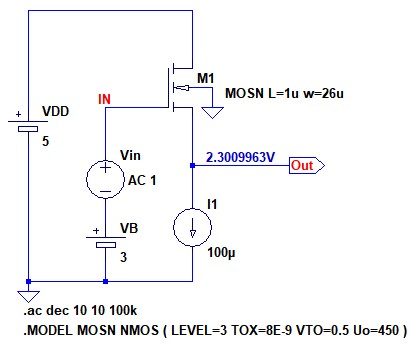

図2は,図1の負荷抵抗(RL)が接続されていないドレイン接地増幅回路です.最初にこの回路のゲインについて考えます.

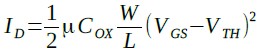

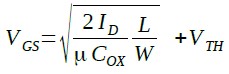

バイアス電圧(VB)が3Vなので,IN端子の直流電圧も3Vになります.そして,Out端子の直流電圧は,IN端子の電圧から,MOSトランジスタ(M1)のゲート・ソース電圧(VGS)だけ低くなります.MOSトランジスタのゲート・ソース電圧(VGS)とドレイン電流(ID)の関係は式1になります.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

この式を変形して,ゲート・ソース電圧(VGS)を求めると,式2になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

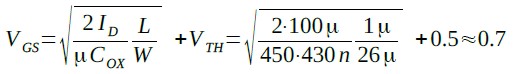

図2では,ソースに100μAの定電流源が接続されています.ソース電流とドレイン電流が等しいため,IDは100μAになります.式2に問題にあるMOSトランジスタの特性を代入すると,式3のように,約0.7Vになります.

・・・・・・・・(3)

・・・・・・・・(3)

出力端子電圧(VOUT)は式4のように,2.3Vになります.

・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・(4)

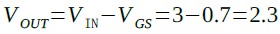

IN端子に信号を加えて電圧が変化しても,M1のソース電流が変化しないため,VGSは常に一定の値です.したがって,出力端子の直流電圧は異なりますが,IN端子に加えた信号がそのままの大きさで出力されます.つまり,ゲインは0dBということになります.

図3は,図2の回路のシミュレーション結果です.ゲインが0dBとなっていることが分かります.なお,図3のトランジスタ・モデルは,VTHが0.5V,キャリア移動度(μ)が450cm2/(V*s),単位面積あたりのゲート容量(COX)が430n F/cm2となるよう,パラメータを設定しています.

ゲインは0dBとなっている

●負荷抵抗を接続したドレイン接地増幅回路のゲイン

次に図2の回路に負荷抵抗が接続された,図1の回路のゲインについて考えます.負荷抵抗を接続すると,負荷抵抗に電流が流れるため,図2の回路とは異なり,M1のソース電流が変化します.ソース電流が変化するとドレイン電流も変化し,式2から分かるようにVGSが変化します.その結果IN端子に加えた信号とOUT端子に現れる信号の大きさは異なったものとなります.

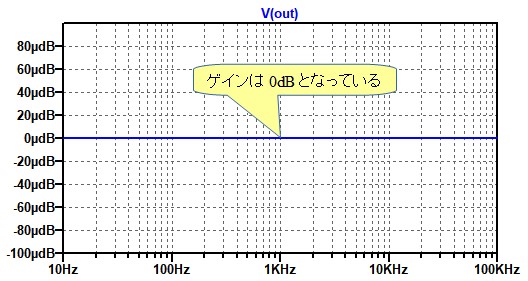

負荷抵抗を接続したときのOUT端子までのゲインを計算するためには,ドレイン接地増幅回路の出力抵抗を知る必要があります.ドレイン電流がΔIDだけ微小変化したときのゲート・ソース電圧の微小変化をΔVGSとすると,出力抵抗(RO)は「RO=ΔVGS/ΔID」で求めることができます.つまり,ドレイン電流とゲート・ソース電圧の関係を表した式2をドレイン電流で微分すれば,式5のように出力抵抗が求まります.

・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・(5)

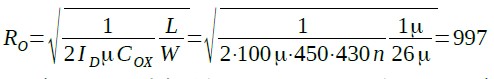

式5に今回の問題の定数を代入すると,出力抵抗(RO)は式6のように約1kΩとなることが分かります.

・・・・・・・・・(6)

・・・・・・・・・(6)

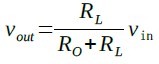

Out端子に出力される信号(VOUT)は,入力信号(VIN)が,ドレイン接地増幅回路の出力抵抗(RO)と負荷抵抗(RL)によって分圧されるため,式7のようになります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

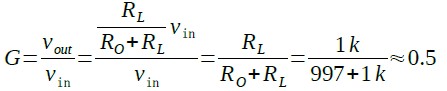

ゲイン(G)は式8のように0.5(-6dB)となります.

・・・・・・・・・・・・(8)

・・・・・・・・・・・・(8)

●負荷抵抗を接続したドレイン接地増幅回路をLTspiceで確認する

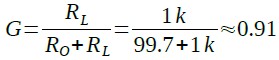

図4が負荷抵抗を接続したドレイン接地増幅回路のゲインをシミュレーションするための回路です.図2の回路にC1とRLを追加したものです.

図2の回路にC1とRLを追加している

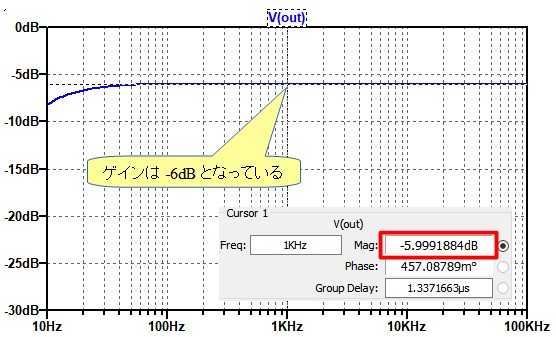

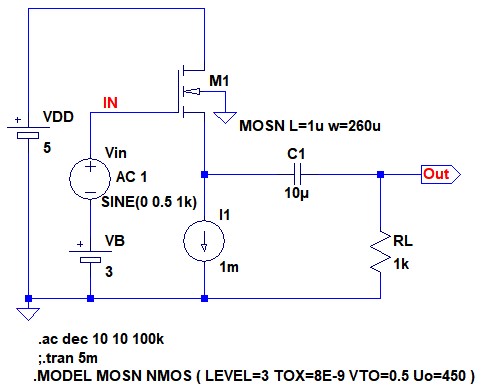

図5が図4のシミュレーション結果です.式8で計算したように,1kHzのゲインは-6dBとなっていることが分かります.

ゲインは-6dBとなっている.

●ドレイン接地増幅回路の出力抵抗を小さくする

ドレイン接地増幅回路は,直流レベルシフトやバッファとして使用されます.バッファとして使用する場合,出力抵抗が大きいために信号が減衰してしまうのは望ましくありません.そこで,ドレイン接地増幅回路の出力抵抗を小さくする方法を考えます.

式5から出力抵抗を小さくするためには,ドレイン電流(ID)を大きくするか,ゲート幅(W)を大きくします.そこで,Wを図1の回路の10倍にします.これで出力抵抗は約1/3.2になります.さらにIDも10倍にすると出力抵抗はさらに約1/3.2になるため,両者の効果を合わせると,出力抵抗を1/10にすることができます.IDを10倍にするためにはソースに接続されている電流源I1の値を10倍にします.WとIDを変更して出力抵抗を小さくしたときのゲインは,式9のように0.91(-0.8dB)になります.

・・・・・・・・・・・・・・・・・・・・・・・(9)

・・・・・・・・・・・・・・・・・・・・・・・(9)

また,式2から分かるように,WとIDを同時に10倍にすることで,ゲート・ソース電圧(VGS)は図1と同じ値になります.図6がWとIDを10倍にしたシミュレーション用の回路です.

ゲート幅(W)とドレイン電流(ID)を10倍にした.

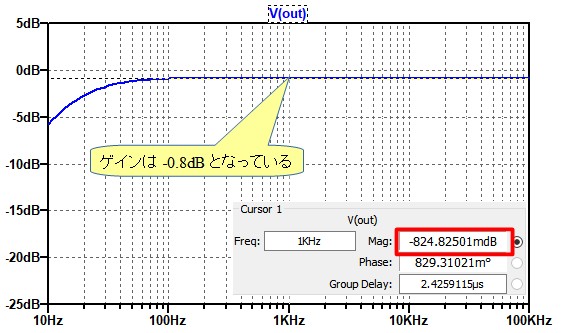

図7が出力抵抗を小さくしたドレイン接地増幅回路の,ゲインのシミュレーション結果です.ゲインは計算結果と同じ,-0.8dBになっています.

ゲインは計算結果と同じ-0.8dBになっている.

以上,MOSトランジスタを使用したドレイン接地増幅回路(ソース・フォロア)について解説しました.一般的に集積回路の中のNchMOSトランジスタのバック・ゲートは,図1の回路のようにGNDに接続されています.このような接続の場合,ソースの電位が変動すると,バック・ゲート効果により,閾値電圧(VTH)の大きさが変化し,波形ひずみが発生します.PchMOSトランジスタのようにバック・ゲートを任意の場所に接続できる場合は,バック・ゲートをソース端子に接続することでVTHの変動を防ぎ,波形ひずみを小さくすることができます.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice4_012.zip

●データ・ファイル内容

CD_amp.asc:図2の回路

CD_amp_RL.asc:図4の回路

CD_amp_W_ID_RL.asc:図6の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs