ソース接地増幅回路のゲイン

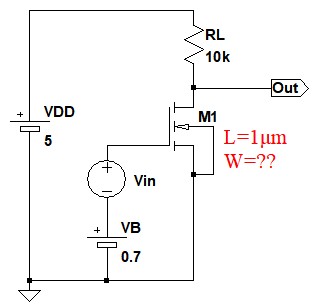

図1は,NchMOSトランジスタを使用したソース接地増幅回路です.電源(VDD)電圧が5Vで,負荷抵抗(RL)が10kΩとなっています.使用しているMOSトランジスタのゲート長(L)は,1μmです.ゲート・バイアス電圧を0.7Vとしたとき,このソース接地増幅回路のゲインが20dBとなるMOSトランジスタのゲート幅(W)は,(A)~(D)のどれでしょうか.ただし,このMOSトランジスタの特性は,スレッショルド電圧(VTH)が0.5V,キャリア移動度(μ)が450cm2/(V*s),単位面積あたりのゲート容量(COX)が430n F/cm2で,出力抵抗は十分大きいものとします.

ゲインが20dBとなる,MOSトランジスタのゲート幅(W)はいくつ?

Wを計算するためには,まずゲインが20dBとなるMOSトランジスタのgm(相互コンダクタンス)を求めます.そして,MOSトランジスタのgmがμ,COX,Wおよび「ゲート・ソース電圧からVTHを引いたもの」に比例し,Lに反比例することを利用して,Wの値を計算します.

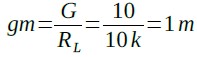

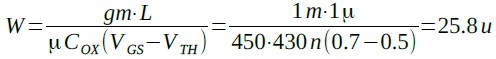

ゲインを20dBとするためのMOSトランジスタのgmの値は,ゲインを負荷抵抗値で割ったもので,10/10k=1mSになります.そして,MOSトランジスタのgmが1mSになるゲート幅は「W=gm*L/(μ*COX*W(VGS-VTH))=25.8μ」と計算することができます.つまり,正解は(C)ということになります.

●MOSトランジスタのgm

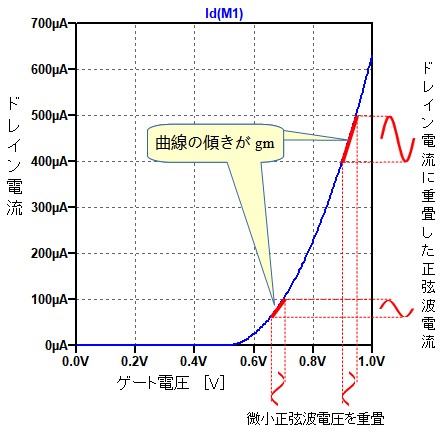

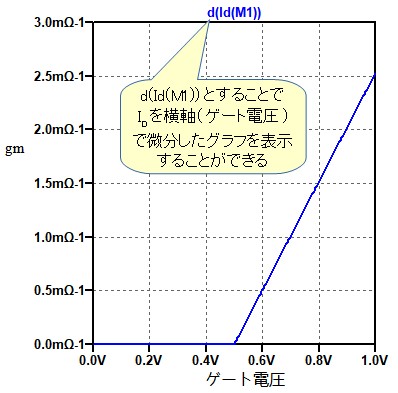

gmは,MOSトランジスタを使用して増幅回路を設計するための,最も重要なパラメータです.gmは,MOSトランジスタのゲート電圧とドレイン電流の関係式から求めることができます.図2は,MOSトランジスタのゲート電圧とドレイン電流のグラフです.そしてgmは,入力電圧の微小変化に対する出力電流変化の度合いを表す係数です.図2のようにゲートに直流電圧と微小振幅の正弦波電圧を重畳して加えると,ドレイン電流波形は,直流電流に正弦波電流が重畳したものになります.その正弦波電流の振幅は,図2のようにゲート電圧が低いときは小さく,ゲート電圧が高くなると大きくなります.つまり,MOSトランジスタのgmは,ゲート電圧が高いほど大きくなります.特定のゲート電圧を加えたときのgmの値は,そのゲート電圧での,ドレイン電流グラフの曲線の傾きになります.曲線の傾きは,ドレイン電流とゲート電圧の関係式をゲート電圧で微分することで求めることができます.

ドレイン電流グラフの曲線の傾きがgm

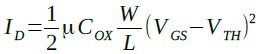

ゲート・ソース電圧(VGS)とドレイン電流(ID)の関係は式1のようになります.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

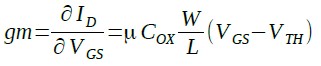

そのため,gmは式1をゲート・ソース電圧で微分して,式2のように求められます.

・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・(2)

図3は,図2のドレイン電流のグラフを横軸(ゲート電圧)で微分したもので,縦軸がgmになっています.gmは,ゲート電圧に比例して増加することが分かります.

gmはゲート電圧に比例して増加する.

●ソース接地増幅回路のゲインの計算

図1の回路において,入力信号(VIN)に対するドレイン電流の変化分(ΔID)はgmを使用し,式3のように求められます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

また,入力信号(VIN)によって負荷抵抗(RL)に発生する出力電圧の変化分(VOUT)は,ΔIDを使用して式4で計算できます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

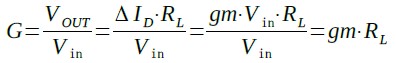

ゲイン(G)は,出力電圧の変化分を入力電圧で割ったものなので,式5のように計算できます.

・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・(5)

式5を変形すると,図1の回路でゲインを20dB(10倍)にするために必要なgmの値は,式6のように求めることができます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

式2と式6を使用して,ゲインを20dBとするためのWの値を計算すると,式7のように約26μmとなります.

・・・・・・・・・(7)

・・・・・・・・・(7)

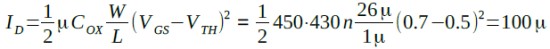

また,このときのドレイン電流の大きさは,式8から100μAとなることが分かります.

・・・・・(8)

・・・・・(8)

●ソース接地増幅回路のゲインのシュミレーション

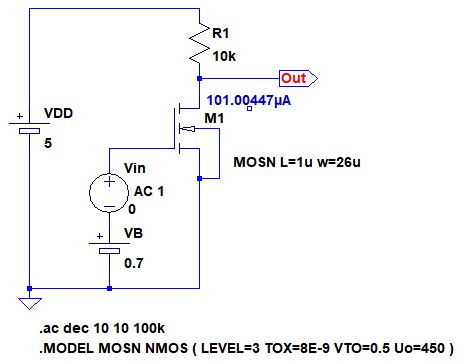

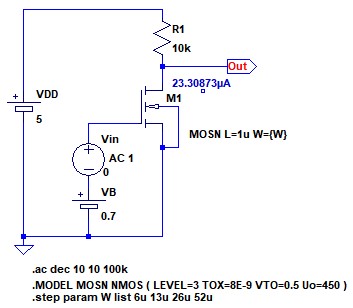

図4は,ソース接地増幅回路のゲインをシミュレーションするための回路です.MOSトランジスタのサイズは「L=1μm,W=26μm」と設定しています.またトランジスタ・モデルは,VTHが0.5V,キャリア移動度(μ)が450 cm2/(V*s),単位面積あたりのゲート容量(COX)が430n F/cm2となるよう,パラメータを設定しています.また,ドレイン電流の大きさを回路図上に表示できるよう,データ・ラベルを配置してあります.

MOSトランジスタのサイズは「L=1μm,W=26μm」と設定している.

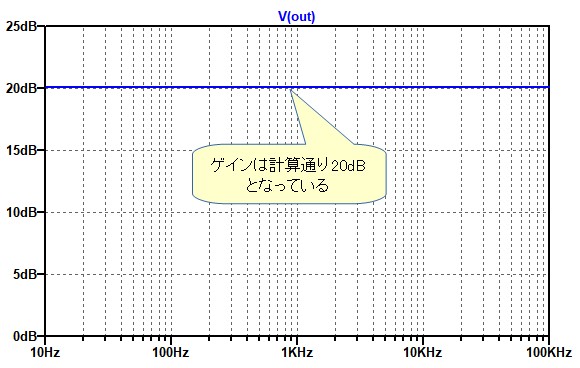

図5がゲインのシミュレーション結果です.式7で求めたようにWを26μmとすることで,ゲインが20dBとなることが分かります.

Wを26μmとすることで,ゲインが20dBとなることが確認できる.

●ゲート幅を変えたソース接地増幅回路のシュミレーション

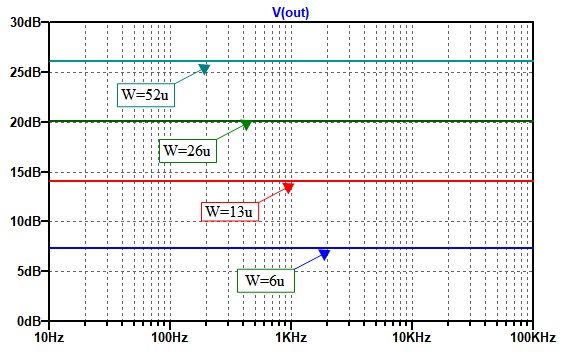

図6は,Wの値を変えてソース接地増幅回路のゲインをシミュレーションするための回路です.MOSトランジスタのWの値をWという名前の変数に置き換え「.stepコマンド」でWを6u,13u,26u,52uの4種類に変えてゲインをシミュレーションします.

Wを6u,13u,26u,52uの4種類に変えてゲインをシミュレーションする.

図7がそのシミュレーション結果です.Wの値によってゲインが変わり,Wが大きいほどゲインが大きくなることが分かります.

Wが大きいほどゲインが大きくなることが分かる.

以上,ソース接地増幅回路のゲインについて解説しました.ここでは,MOSトランジスタの出力抵抗は,無視できるほど十分大きいものとしてゲインを計算しました.またシミュレーション用のMOSトランジスタのモデルも,出力抵抗の大きいものとなっています.ただし,実際のMOSトランジスタの出力抵抗は有限の値を持っており,特にLの値が小さい場合は,無視できない値となって,計算よりもゲインが小さくなります.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice4_010.zip

●データ・ファイル内容

MOS_VG_ID_W26.asc:図3をシミュレーションするための回路

CS_amp.asc:図4の回路

CS_amp_W.asc:図6の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs