OPアンプの雑音を低く見せる複合アンプ

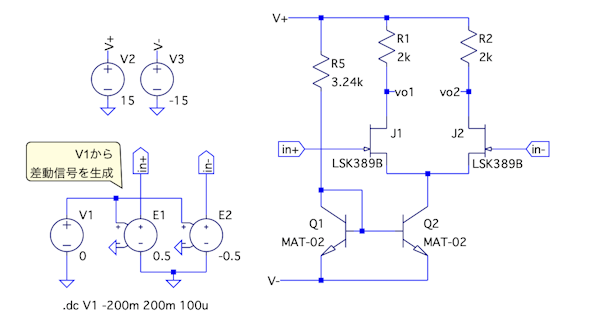

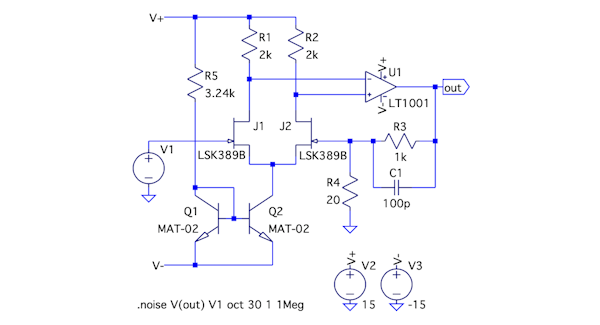

図1は,入力雑音を低くするため,JFETを使った前置アンプ(LSK389)とOPアンプ(LT1001)で構成した複合アンプ回路です.この回路全体の入力雑音として近いのは(a)~(d)のどれでしょうか.

ただし,前置アンプの雑音は,シミュレーションで調べると1.05nV/√Hz,OPアンプの雑音が9.8nV/√Hzです.そして前置アンプの相互コンダクタンス(Gm)は21.6mA/Vです.

入力端子(in+とin-の間)に見える入力雑音として近いのは(a)~(d)のどれ?

(a) 1nV/√Hz (b) 2nV/√Hz (c) 4nV/√Hz (d) 6nV/√Hz

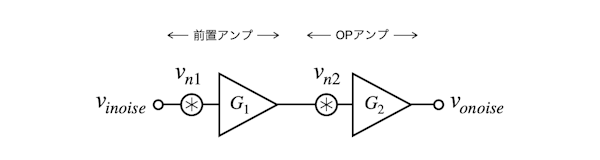

複合アンプの入力雑音は, 前置アンプの雑音(vn1)と,OPアンプの雑音(vn2)に関係します.この2つの雑音が複合アンプの入力端子(in+とin-の間)からどのように見えるのかを検討すると分かります.

最初に,入力雑音の検討には,前置アンプのゲインが必要になります.図1の前置アンプのゲインをG1とすると,前置アンプの相互コンダクタンスが21.6mA/Vと,抵抗R1とR2が2kΩより,ゲインは「G1=21.6mA/V×2kΩ」より43倍になります.

次に,図1の複合アンプの入力雑音は,前置アンプの雑音とOPアンプの雑音に関係します.具体的には,前置アンプの雑音は「vn1=1.05nV/√Hz」です.一方,OPアンプの雑音(vn2)は、複合アンプの入力からみると,前置アンプのゲイン(G1)で割った値に見えるので,「vn2/G1=9.8nV/√Hz÷43=0.2nV/√Hz」になります.回路全体の入力雑音は,vn1とvn2/G1の両方を合わせた雑音です.合わせた雑音は3倍以上高い方の雑音が支配的になります.vn1は,vn2/G1より約5倍高い雑音なので,図1の雑音はvn1が支配的になり,解答は,(a) 1nV/√Hzなります.

●複合アンプは低雑音アンプにできる

複合アンプとは,2つのアンプを使った増幅回路のことです.図1では前置アンプとOPアンプの2つになります.2つのアンプを使うのは,互いの良い性能を使って,アンプ回路の性能を良くします.

図1の前置アンプは,LSK389を使ったアンプになります.LSK389は,低雑音で整合のとれたペアのJFET(接合形電界効果トランジスタ)で,前置アンプの雑音をシミュレーションで調べると1.05nV/√Hzの性能です(データシートでは1.6nV/√Hz).JFETは,利点として入力バイアス電流が非常に低く,バイポーラ・トランジスタより高い入力インピーダンスになります.欠点としては,一般的にJFETの相互コンダクタンスは低いので,ゲインを高くできません.

図1の2段目のOPアンプは,LT1001になります.LT1001の雑音はデータシートより9.8nV/√Hzの性能です.このOPアンプの雑音を前置アンプで低く見せて,複合アンプの入力雑音は,前置アンプの雑音が支配的になるようにしています.OPアンプのゲインは高いので,前置アンプの低いゲインを補います.

ここでは複合アンプの入力雑音を検討するので,前置アンプの雑音とOPアンプの雑音をシミュレーションで調べます.複合アンプの雑音計算は,前置アンプのゲインが必要になるので,前置アンプの相互コンダクタンスをシミュレーションで調べてゲインを求めます.これらの値を使って解答を導き出します.

●OPアンプの雑音

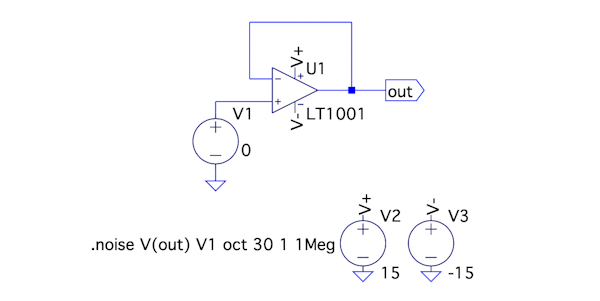

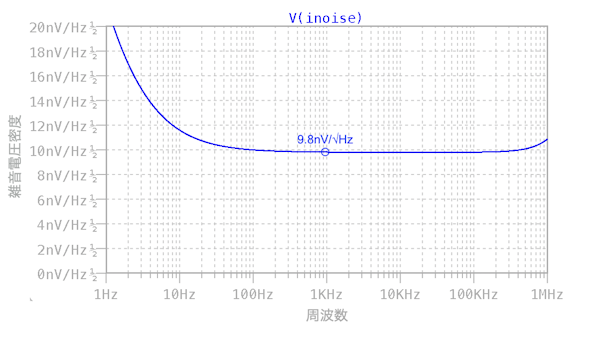

図2は,OPアンプ(LT1001)を使ったユニティ・ゲイン・バッファで,OPアンプの雑音を調べる回路になります.雑音を調べるときは「.noise解析」を用います.図2は「.noise V(out) V1 oct 30 1 1Meg」のドット・コマンドより,1Hz~1MHz間を周波数が2倍あたり30ポイントで,雑音の周波数特性をシミュレーションします.

図3は,図2のシミュレーション結果になります.図3より,OPアンプの雑音は,周波数が1kHzのとき9.8nV/√Hzになります.この値はデータシートにあるOPアンプの雑音と一致しています.

OPアンプの雑音は1kHzで9.8nV/√Hzになる.

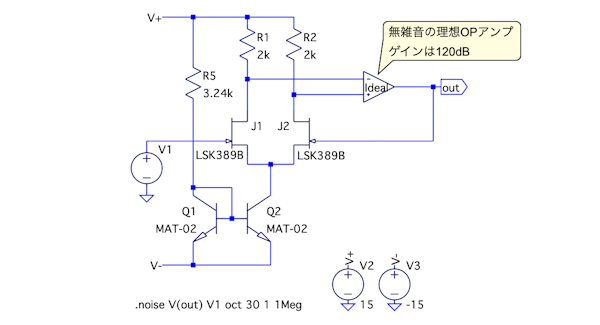

●前置アンプの雑音

図4は,前置アンプと理想OPアンプを使ったユニティ・ゲイン・バッファで,前置アンプの雑音を調べる回路になります.理想OPアンプは,無雑音なので,図4の回路で前置アンプの雑音を調べることができます.シミュレーションは,図2と同様にドット・コマンドより,1Hz~1MHz間を周波数が2倍あたり30ポイントで,雑音の周波数特性をシミュレーションします.

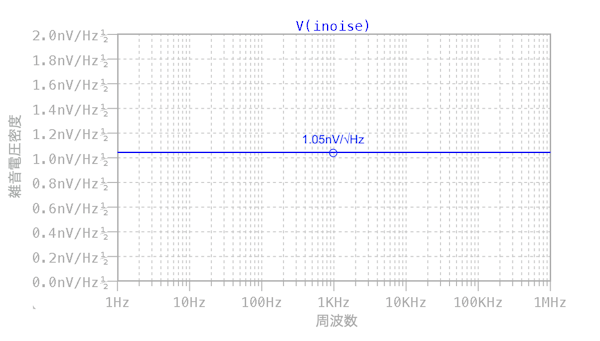

図5は,図4のシミュレーション結果になります.図5より,前置アンプの雑音は,周波数が1kHzのとき1.05nV/√Hzになります.

前置アンプの雑音は1kHzで1.05nV/√Hzになる.

●前置アンプの相互コンダクタンスを調べる回路

次に,図1の入力雑音を検討するため,図6の前置アンプの回路で相互コンダクタンスを調べます.図1では雑音計算の条件として,相互コンダクタンスが「Gm=21.6mA/V」と表しました.その確認になります.

ここでは図6のシミュレーション回路で相互コンダクタンスを調べます.

J1とJ2のゲートに差動信号を入力して調べる.

相互コンダクタンスは,差動入力電圧の変化によるJ1とJ2のドレイン電流の変化になり,式1になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)図6では,差動入力信号として,V1の電圧変化を,E1,E2を介して前置アンプのin+とin-に加わるようにしています.

●相互コンダクタンスのシミュレーションとゲインの計算

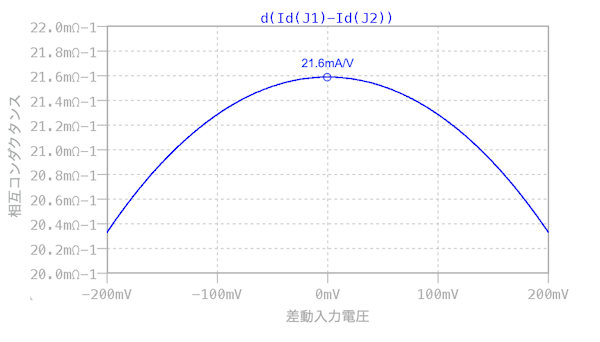

図7は図6のシミュレーション結果で相互コンダクタンスのプロットになります.相互コンダクタンスは式1なので,LTspiceの導関数「d()」を用い,「d(Id(J1)-Id(j2))」で求めたプロットになります.

相互コンダクタンスは21.6mA/V.

複合アンプは負帰還をかけて使います.負帰還が成り立つとき,in+とin-はバーチャル・ショートになるので,差動入力電圧はゼロになります.図6の差動入力電圧がゼロのときの相互コンダクタンスは「Gm=21.6mA/V」になります.「Gm=21.6mA/V」の相互コンダクタンスを使い,前置アンプのゲインを計算すると,式2の43倍になります.

・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・(2)式2中のRはR1とR2の抵抗であり,「R=2kΩ」です.

●2つの複合アンプで構成したときの入力雑音を机上計算する

図1の入力雑音を机上計算して解答を確認します.机上計算は,図8の前置アンプとOPアンプの2つのアンプを接続したブロック図を用います.

後段のアンプの雑音vn2は前段のゲインG1で割った値になる.

vn1は前置アンプの雑音で「vn1=1.07nV/√Hz」です.また,vn2はOPアンプの雑音で「vn2=9.8nV/√Hz」です.G1は前置アンプのゲインで,式2より「G1=43」になります.

図8の出力雑音(vonoise)は,「vn1をG1とG2で増幅した雑音」と,「vn2をG2で増幅した雑音」を加えたものになり,具体的には式3になります.

・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・(3)図8の出力雑音(vonoise)から入力雑音(vinoise)を求めます.入力雑音(vinoise)は,式3の出力雑音(vonoise)を全体のゲインG1G2で割ったものなので,式4になります.

・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・(4)式4より,OPアンプの雑音は前置アンプのゲインで割った値に見えるので低くなります.式4のvn1とvn2/G1の大きさを検討します.vn1は前置アンプの雑音なので,「vn1=1.05nV/√Hz」です.vn2/G1は式2で調べた「G1=43」とOPアンプの入力雑音は「vn2=9.8nV/√Hz」なので「vn2/G1=0.2nV/√Hz」になります.

この結果より,vn1はvn2/G1より約5倍高い雑音になります.式4の二乗和平方根は,3倍以上大きな項が支配的になる特徴があるので,入力雑音(vinoise)は前置アンプ入力雑音が支配的になり,複合アンプの入力雑音は,解答(a)の1nV/√Hzになります.詳細な計算として,式4の各項に値を入れると式5になり,1.07nV/√Hzになるのが分かります.

・・・・・(5)

・・・・・(5)

●複合アンプの入力雑音をシミュレーションで確かめる

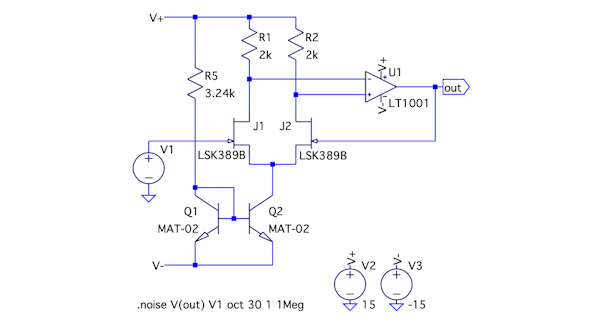

図9は,前置アンプとOPアンプ(LT1001)を使ったユニティ・ゲイン・バッファで,複合アンプの入力雑音を調べる回路になります.シミュレーションは,図2と同様にドット・コマンドより,1Hz~1MHz間を周波数が2倍あたり30ポイントで,雑音の周波数特性をシミュレーションします.

図10は図9のシミュレーション結果になります.図10より,複合アンプの雑音は,周波数が1kHzのとき1.07nV/√Hzになります.この雑音は式5の机上計算と一致します.

前置アンプの雑音は1kHzで1.07nV/√Hzになり机上計算と一致している.

●複合アンプの応用例

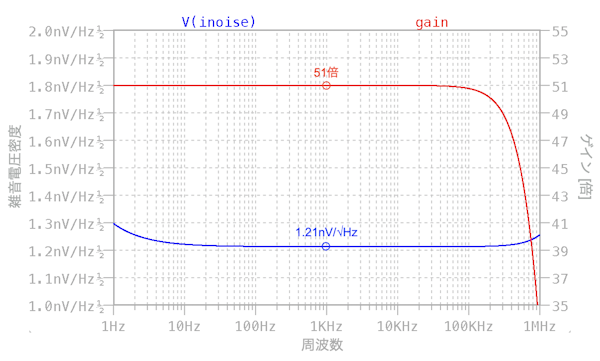

図11は,複合アンプを使った負帰還アンプで,ゲインは「G=1+R3/R4」で51倍です.C1は負帰還を安定にする補償コンデンサになります.このようなアプリケーションのとき,図11の負帰還アンプはどれくらい低雑音なのかを検討します.

図11の回路の雑音を計算します.式5で求めた複合アンプの雑音をvnとします.そして,R3とR4の並列抵抗を「Req=20Ω」とします.Reqの熱雑音は「vReq=(4kT×20Ω)1/2=0.58nV/√Hz」です.ここでkはボルツマン定数,Tは絶対温度です.複合アンプの雑音vnとReqの熱雑音vReqより,図11の負帰還アンプの入力雑音は式6になると見積もれます.

・・・・・(6)

・・・・・(6)この計算の詳細は「負帰還アンプの雑音が小さい抵抗値の決め方」を参考にしてください.

図12は,図11のシミュレーション結果になります.

入力雑音は1kHzの周波数で1.21nV/√Hzになる.

プロットはV(inoise)が入力雑音を表し,gainは入力のv1から出力outまでのゲイン周波数特性になります.図12より,ゲインは51倍で,入力雑音は周波数が1kHzのとき1.21nV/√Hzになり,雑音は式6と等しいことが分かります.このように図11の複合アンプを使った負帰還アンプは,入力雑音を低く抑えることができます.

以上,複合アンプは,OPアンプの雑音を前置アンプで低く見せて,入力雑音を低くできます.今回の前置アンプはJFETです.JFETを使うとき注意が必要なのは入力オフセット電圧です.JFETのLSK389のデータシートで「Matching Characteristics」を参照すると,入力オフセット電圧を示す「VGS1-VGS2」の絶対値は標準で6mV,最大で15mVです.また,ドレイン電流の整合を示す「IDSS1/IDSS2」は±10%あります.このため,図1の回路でオフセット電圧調整する回路が必要になるときがあります.

◆参考・引用*文献

リニア・システムズ:LSK389のデータシート

アナログ・デバイセズ:LT1001のデータシート

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice10_016.zip

●データ・ファイル内容

OPAmp NOISE.asc:図2の回路

OPAmp NOISE.plt:図2のプロットを指定するファイル

Pre-Amplifier NOISE.asc:図4の回路

Pre-Amplifier NOISE.plt:図4のプロットを指定するファイル

Gm.asc:図6の回路

Gm.plt:図6のプロットを指定するファイル

Hybrid JFET Amplifier NOISE.asc:図9の回路

Hybrid JFET Amplifier NOISE:図9のプロットを指定するファイル

Hybrid JFET Amplifier 2 NOISE.asc:図11の回路

Hybrid JFET Amplifier 2 NOISE.plt:図11のプロットを指定するファイル

Ideal_OP.asc:理想OPアンプの回路

Ideal_OP.asy:理想OPアンプのシンボル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs