ハートレー発振回路

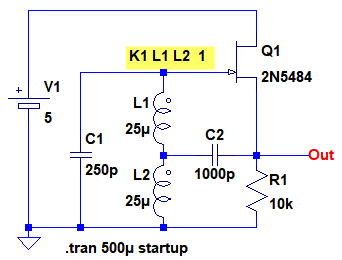

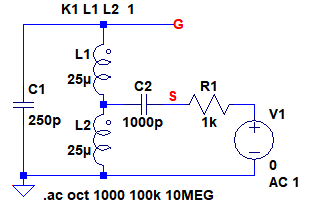

図1は,NチャネルJFETを使用したハートレー発振回路をシミュレーションするための回路です.センタータップ付きのコイルを使用した場合をシミュレーションするため,L1とL2を相互コンダクタンス(K1)を使用して結合しています.このK1の係数を1から0に変えた場合の,発振周波数の説明として正しいのは(a)~(d)のどれでしょうか.

K1の係数を1から0に変えた場合,発振周波数はどうなる?

(a) K1の係数を0にした場合は発振しないため,比較できない

(b) K1の係数を0にしても発振周波数は変わらない

(c) K1の係数を0にすると,発振周波数は低くなる

(d) K1の係数を0にすると,発振周波数は高くなる

ハートレー発振回路は,ラルフ・ハートレー(Ralph Vinton Lyon Hartley)によって発明された回路です.ハートレー発振回路はクラップ発振回路と同様に無線通信機器の局部発振回路として使用されます.

ハートレー発振回路の発振周波数は,コンデンサの容量とそこに並列接続されたコイルのインダクタンスによって決まります.K1の係数を変えたときのインダクタンスの変化を考えれば答えが分かります.

図1でK1の係数を1とした場合,L1とL2を直列にしたコイルの合成インダクタンスは,L1のインダクタンスの4倍の100μHとなります.一方,K1の係数を0とした場合,L1とL2はそれぞれ独立したコイルとして扱われます.そのため,L1とL2を直列にしたコイルの合成インダクタンスは,2つのインダクタンスを足し合わせた50μHになります.このように,係数を0にしたほうが,インダクタンスが小さくなります.インダクタンスが小さい方が発振周波数が高いため,(d)の「K1の係数を0にすると,発振周波数は高くなる」が正解です.

●コルピッツ発振回路とハートレー発振回路の違い

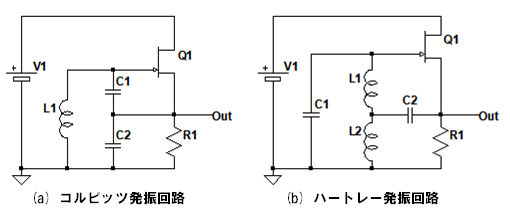

図2の(a)がコルピッツ発振回路で,(b)がハートレー発振回路です.ハートレー発振回路のC2は,カップリング・コンデンサです.それ以外の部分を見ると,ハートレー発振回路はコルピッツ発振回路のコイルとコンデンサを入れ替えたものと言えます.ハートレー発振回路のL1とL2は独立した2つのコイルとしてもよいのですが,コイルの個数を減らすため,タップ付きの1つのコイルを使用するのが一般的です.ハートレー発振回路は,C1の容量値を変えることで,発振周波数を変えることができるため,ラジオ受信機等に使用されます.

ハートレー発振回路はコルピッツ発振回路のコイルとコンデンサを入れ替えたもの.

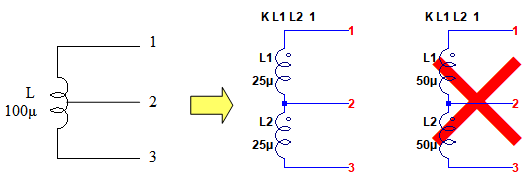

●LTspiceでタップ付きコイルを使用するときの注意点

LTspiceで,センター・タップ付きのコイルを使用する場合,相互インダクタンス(K)を使用して2つのコイルを結合します.このとき,インダクタンスの値の設定に注意が必要です.

図3のように1~3間のインダクタンスが100μHのセンター・タップ付きコイルをシミュレーションする場合,2つのコイル・インダクタンスは50μHではなく,25μHとする必要があります.

100μHのセンター・タップ付きコイルの場合,2つのコイルのインダクタンスは25μHとする.

Kの係数を1とした場合,L1IとL2を直列にしたコイルの合成インダクタンスは,L1のインダクタンスの4倍になるためです.なぜL1の4倍になるのかは,コイルのインダクタンスが巻き数の2乗に比例することを考えると理解しやすいと思います.

L1とL2のインダクタンスの値が同じLだった場合,その巻き数は同じです.L1とL2が独立したコイルの場合はL1とL2を直列にしたコイルの合成インダクタンスは,L1とL2のインダクタンスを足した,2Lになります.

一方,相互インダクタンス(K)を使用して2つのコイルを結合した場合,L1とL2を直列にしたものは,L1の2倍の巻き数のコイルとして扱われます.コイルのインダクタンスは巻き数の2乗に比例するので,L1とL2を結合したもののインダクタンスはL1の4倍の4Lになります.

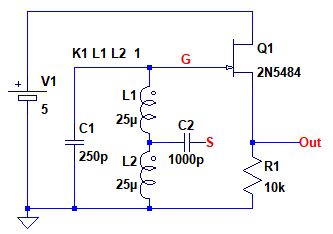

●ハートレー発振回路の発振条件と発振周波数

図1のハートレー発振回路は,JETによるドレイン接地増幅回路を使用しています.図4は,図1の回路の帰還ループを切断したものです.ドレイン接地増幅回路のG端子からOut端子までのゲインは0dBよりも小さく,-0.6dB程度になります(LTspiceエデュケーショナル・ファイルで学ぶアナログ回路 013 コルピッツ発振回路 参照).そのため,この回路が発振するためにはS端子からG端子までのゲインが0.6dB以上となっている必要があります.

Out端子とS端子を接続すると発振回路となる.

図5は,図4のS端子からG端子までのゲインをシミュレーションするための回路です.R1はドレイン接地増幅回路の出力抵抗にあたるものです.

R1はドレイン接地増幅回路の出力抵抗.

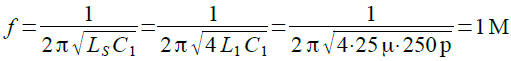

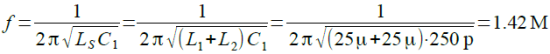

この回路はC1およびL1とL2の合成インダクタンスが並列になっています.L1とL2の合成インダクタンスの値をLSとすると,並列共振周波数は式1で表されます.

・・・・・・・・(1)

・・・・・・・・(1)

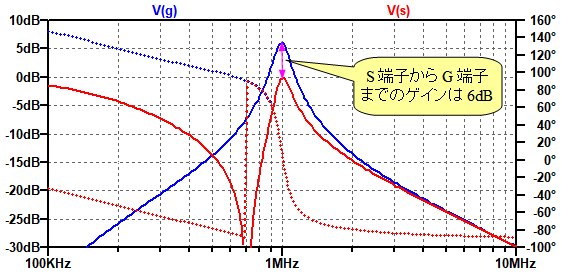

図6は,図5のシミュレーション結果です.ゲインが最大となる周波数は1MHzでS端子からG端子までのゲインは6dBとなっており,発振条件を満たしていることが分かります.

ゲインが最大となる周波数は1MHzでS端子からG端子までのゲインは6dB.

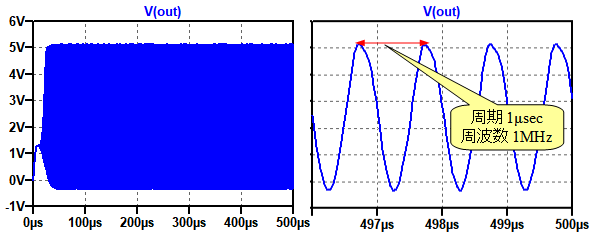

図7は,図1でK1の係数を1とした場合のシミュレーション結果です.右側は横軸を拡大したものですが,発振波形の1周期が1μsecで周波数は1MHzとなっています.これは式1の計算結果と一致しています.

発振波形の1周期が1μsecで周波数は1MHz.

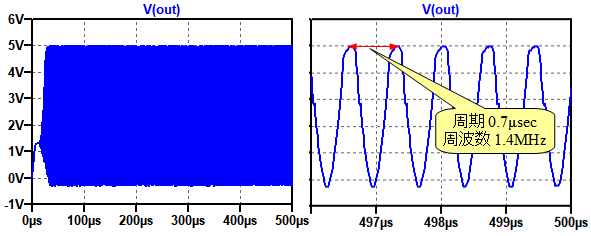

図8は,図1でK1の係数を0とした場合のシミュレーション結果です.

発振波形の1周期が0.7μsecで周波数は1.4MHz.

この場合の発振周波数は式2で計算できます.シミュレーションによる発振波形の1周期は約0.7μsecで周波数は1.4MHzと式2の結果と一致しています.

・・・・・(2)

・・・・・(2)

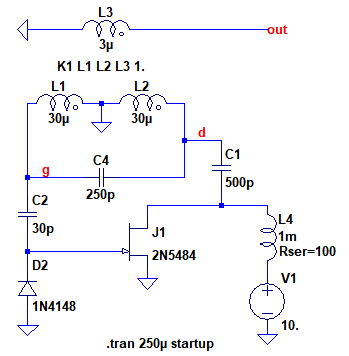

図9は,エデュケーショナルフォルダにあるハートレー発振回路(ドキュメント\LTspiceXVII\examples\Educational\Hartly.asc)です.JETのJ1はコイルのL4を負荷としたソース接地増幅として動作します.そして,L1,L2がセンター・タップ付きのコイルで,さらに二次巻線のL3を出力としています.D2はリーク電流によってJ1のゲート電圧を設定するとともに,振幅リミッタとして働きます.

ソース接地増幅回路のドレインの出力波形は,入力とは逆位相になります.そのドレイン出力がC1を介してd端子に加えられます.センター・タップがGNDに接続されているため,g端子の波形はd端子とは逆位相になります.その信号をC2を介してJ1のゲートに加えることで正帰還となり,発振することになります.

JETのJ1はコイルのL4を負荷とした,ソース接地増幅として動作する.

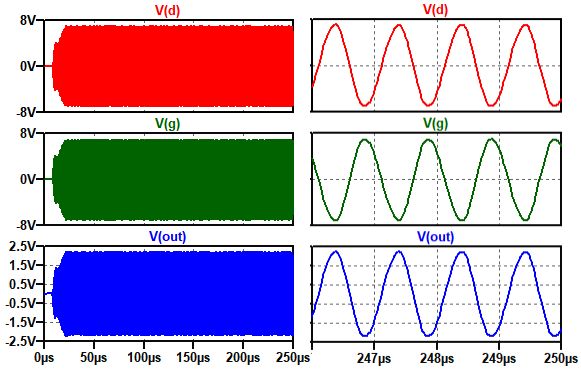

図10は,図9のシミュレーション結果です.一番上がd端子の波形で真ん中がg端子の波形ですが,位相が反転していることが分かります.

d端子とg端子の波形の位相が反転している.

以上,今回は,ハートレー発振回路について解説しました.これまでコイルを使用した3種類の発振回路を紹介してきました.基本的な発振の原理は共通しています.使い分け方としては,周波数固定の場合,コルピッツ発振回路が使用され,周波数を可変する場合,クラップ発振回路やハートレー発振回路がよく使用されています.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice6_017.zip

●データ・ファイル内容

Hartly_JFET.asc:図1の回路

Hartly_LCgain.asc:図5の回路

Hartly_JFET_K0.asc:図8をシミュレーションする回路

Hartly.asc:図9の回路

Hartly.plt:図10のグラフを描画するためのPlot settinngsファイル

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs

(8) オームの法則から学ぶLTspiceアナログ回路入門アーカイブs