コルピッツ発振回路

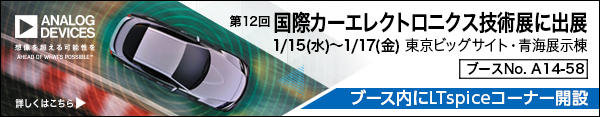

図1の(a)~(d)は,Q1(2N5484)のNチャネルJFET(ジャンクションFET)を使用し,発振回路を製作したものです.コルピッツ発振回路として正常に発振するのは(a)~(d)のどれでしょうか.

コルピッツ発振回路として正常に発振するのはどれ?

(a)の回路 (b)の回路 (c)の回路 (d)の回路

コルピッツ発振回路は,Edwin Henry Colpitts氏によって発明された回路で,コイルとコンデンサの共振を利用した発振回路です.抵抗とコンデンサによる発振回路に比べ,高い周波数で発振させることができるため,ラジオ受信機などに使用されます.

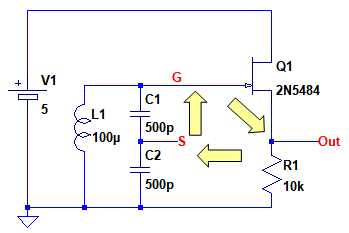

図1の(a)~(d)の回路はいずれもドレイン接地回路となっています.JFETをドレイン接地として動作させる場合のバイアス電圧の与え方と発振回路が発振するための条件を考えれば,答えが分かります.

JFETをドレイン接地増幅回路として動作させる場合,ゲート電圧は,ソース電圧よりも低くする必要があります.(a)と(b)はゲートと電源がコイルで接続されているため,ゲート電圧は電源と同じになってしまい,この条件を満たしません.

(c)と(d)のゲート電圧は,ソース電圧よりも低くなります.また,(c)はソースからゲートに帰還するゲインが発振条件を満たしています.そのため,コルピッツ発振回路として動作するのは,(c)ということになります.

●JFETの性質

JFETは,MOSFETと同様にゲートに印加する電圧でドレイン電流をコントロールできます.ただし,ゲートに印加する電圧はソースに対して負の電圧を与える必要があります.

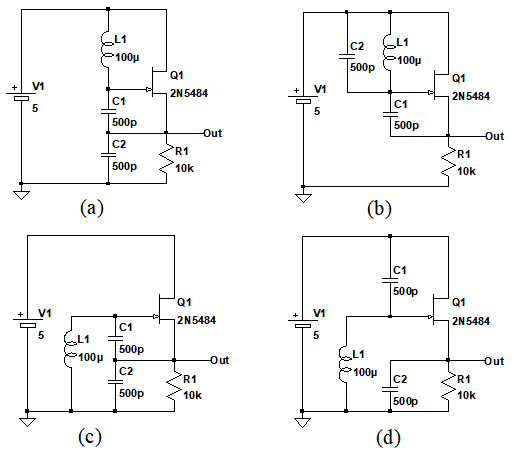

図2は,JFETのゲート電圧とドレイン電流の関係を調べるための回路です.ゲート電圧を-2Vから1Vまで変化させたときのドレイン電流の変化を調べます.

ゲート電圧を-2Vから1Vまで変化させたときのドレイン電流を調べる.

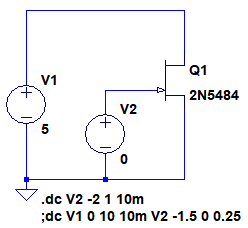

図3は,図2のJFETのゲート電圧とドレイン電流のシミュレーション結果です.ゲート電圧が-1.5V以上でドレイン電流が流れ始め,ゲート電圧が大きくなるほど電流が大きくなります.しかし,ゲート電圧が0.7Vを越えると電流の傾きが変化しています.これは,ゲート・ソースのPN接合が順バイアスとなってしまうためで,ゲート電圧が0.7Vを越えると大きなゲート電流が流れます.そのため,一般的にはJFETのゲート電圧はソース電圧に対して負の電圧で使用します.

ゲート電圧が-1.5V以上でドレイン電流が流れ始める.

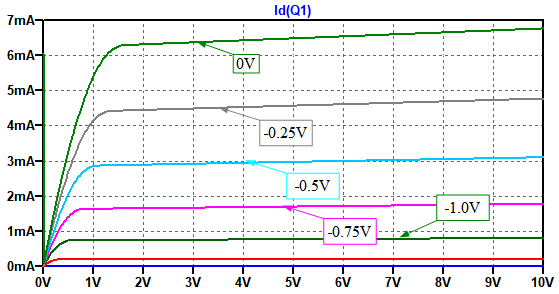

図4は,図2の回路でゲート電圧をパラメータとして-1.5Vから0Vまで0.25Vステップで変化させたときの,ドレイン電圧とドレイン電流のグラフです.これは,JETの静特性と呼ばれるものです.ゲート電圧が負電圧となっている他はMOSFETと同等の特性となっています.

ゲート電圧が負電圧となっている他はMOSFETと同等の特性.

●JFETを使用したドレイン接地回路のゲイン

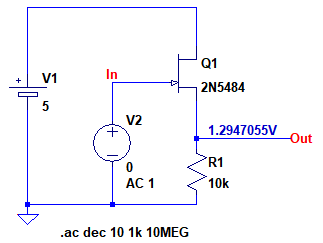

図5は,図1(c)で使用しているドレイン接地回路(ソース・フォロア回路)のゲインをシミュレーションするための回路です.この回路ではゲート電圧は0Vとなっていますが,JFETに流れる電流によりR1に電圧が発生するため,ソース端子の電圧は約1.3Vとなっています.そのため,この回路のゲート端子の電圧は,ソース端子の電圧に対して負電圧で動作していることになります.

ゲート端子の電圧は,ソース端子の電圧に対して負電圧で動作している.

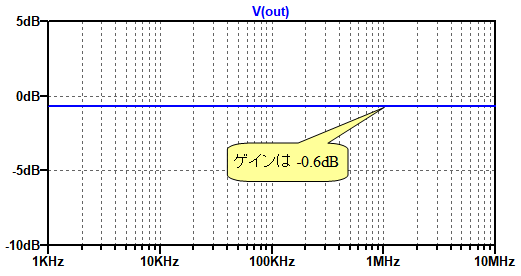

図6は,図5の回路のシミュレーション結果です.ゲインは-0.6dB程度となっており,ソース端子の信号レベルは入力信号よりも若干小さくなることが分かります.

ゲインは-0.6dB程度となっており,1倍よりも小さい.

●ドレイン接地型コルピッツ発振回路が発振する理由

回路が発振するためには,ループ・ゲインが0dB以上となっている必要があります.しかし,図6から分かるように,ドレイン接地回路のゲートからソースまでのゲインは-0.6dBとなっています.そのため,コルピッツ発振回路が発振するためには図7のS端子からG端子までのゲインが0.6dB以上になっている必要があります.

発振するためにはS端子からG端子までのゲインが0.6dB以上必要.

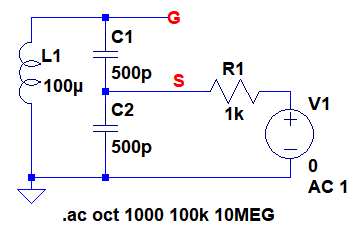

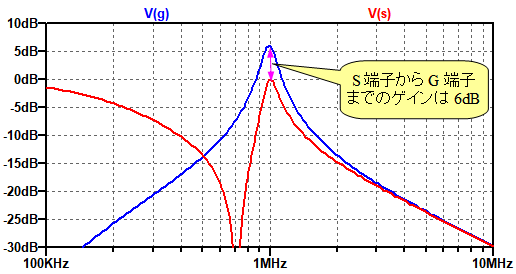

図8は,図7のS端子からG端子までのゲインをシミュレーションするための回路です.ここでR1はドレイン接地回路の出力抵抗にあたるものです.

R1はドレイン接地回路の出力抵抗相当の抵抗.

図9は,S端子からG端子までのゲインのシミュレーション結果です.S端子からG端子までのゲインは約6dBとなっており,図7の回路のループ・ゲインは発振条件を満足することが分かります.

S端子からG端子までのゲインは6dB.

●ドレイン接地型コルピッツ発振回路の発振シミュレーション

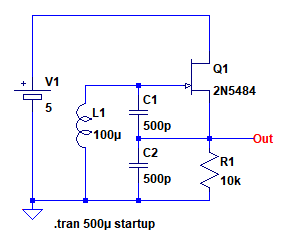

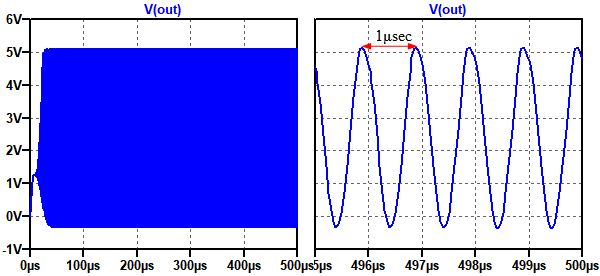

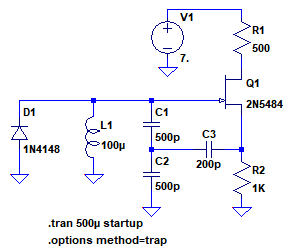

図10は,ドレイン接地型コルピッツ発振回路の発振をシミュレーションするための回路です.500μsecのトランジェント解析を行い,実際に発振するかを確認します.

500μsecのトランジェント解析を行う.

図11は,図10のシミュレーション結果です.右側は495μsec以降を拡大したものです.波形の1周期の時間が約1μsecなので,1MHz程度の周波数で発振していることが分かります.

1MHz程度の周波数で発振していることが分かる.

図12は,エデュケーショナル・フォルダにあるコルピッツ発振回路(ドキュメント\LTspiceXVII\examples\Educational\colpits.asc)です.ダイオードのD1はコイルの振幅を制限するためのものです.

D1はコイルの振幅を制限するためのもの.

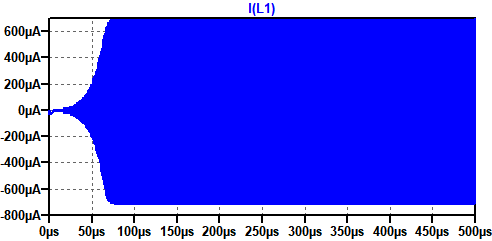

図13は,図12のシミュレーション結果です.コイルに流れる電流を表示していますが,きちんと発振していることが分かります.

コイルの電流を表示しているが,きちんと発振している.

以上,コルピッツ発振回路について解説しました.コルピッツ発振回路にはいろいろ回路形式があります.バイポーラ・トランジスタを使用したものに関しては,「LTspiceアナログ電子回路入門:029 コルピッツ発振回路の発振周波数を表す式は?」を参照してください.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice6_013.zip

●データ・ファイル内容

JFET_DC.asc:図2の回路

JFET_CD_AC.asc:図5の回路

colpits_LCgain.asc:図8の回路

colpits_JFET.asc:図10の回路

colpits.asc:図12の回路

colpits.plt:図12のグラフを描画するためのPlot settinngsファイル

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs

(8) オームの法則から学ぶLTspiceアナログ回路入門アーカイブs