移相型発振回路の発振の条件

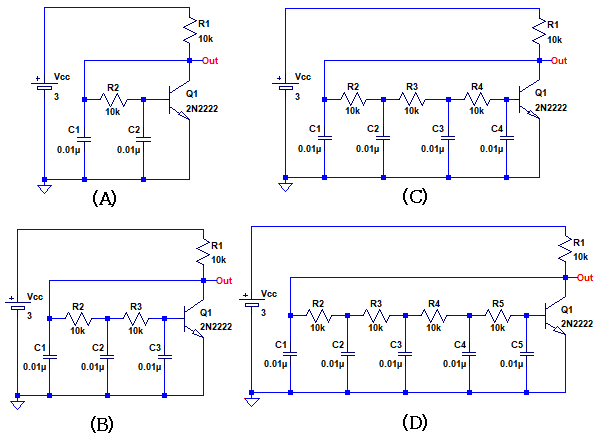

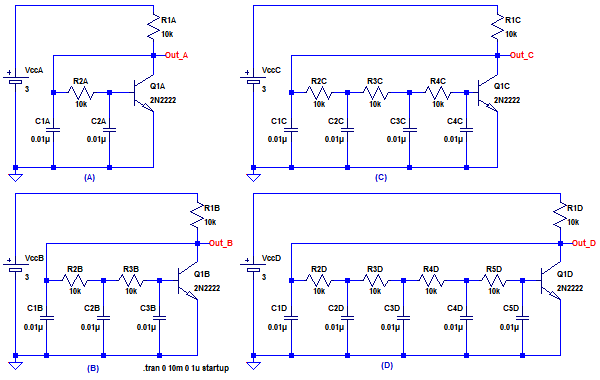

図1の(A)~(D)の回路は,1つのトランジスタと抵抗およびコンデンサを使用して,移相型発振回路を設計したものです.(A)~(D)の回路の中で,実際に発振するものはどれでしょうか.複数ある場合,すべて挙げてください.

(A)~(D)の回路の中で,実際に発振するものはどれ?

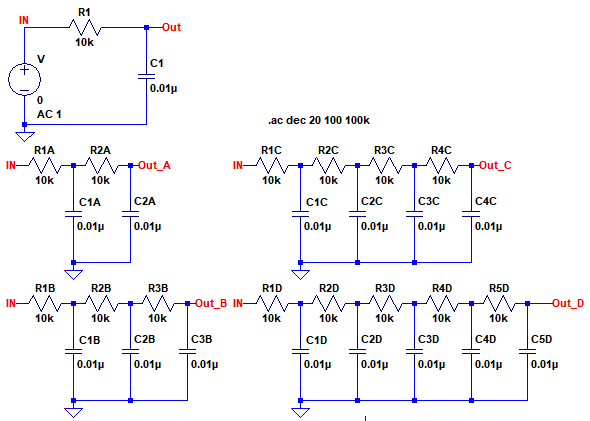

図1の(A)~(D)でトランジスタは,反転増幅回路として動作します.コレクタ出力は,抵抗とコンデンサによるフィードバック回路を介してベースに帰還されています.回路が発振するためには,帰還された信号の位相が180度回転し,ループ利得が1以上となっている必要があります.この条件を満たすものを考えれば解答が分かります.

図1の(A)~(D)の帰還回路は,いずれも,抵抗とコンデンサによる1次ローパス・フィルタが縦続接続されたものです.この帰還回路でループ利得が1以上で,位相が180度回転するのは,3段以上縦続接続されたものです.そのため,(A)は2段しか縦続接続されていないので,発振条件を満たしていません.発振する回路は,(B),(C),(D)ということになります.

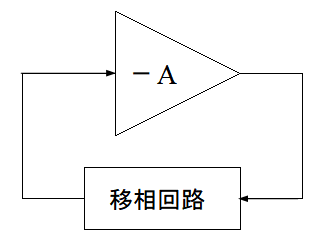

●移相型発振回路の原理

図2は,移相発振回路のブロック図です.ゲインがA倍の反転増幅回路の出力を移相回路に入力し,その移相回路出力を反転増幅回路の入力に加えるように構成します.この回路が発振するためには,次の2つの条件を満たす必要があります.1つ目は,移相回路で位相が180度回転することです.2つ目は,位相が180度回転した周波数で移相回路の減衰量よりも,反転増幅回路のゲインが大きいことです.2つ目の条件は,移相回路の減衰量と反転増幅回路のゲインを掛け合わせたループ利得が1以上であること,と言い換えることができます.

この回路が発振するためには位相とゲインの2つの条件を満たす必要がある.

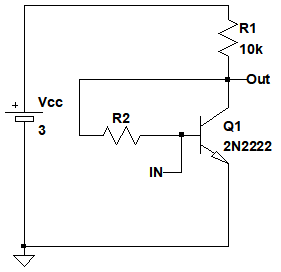

●自己バイアス型エミッタ接地増幅回路

図1の回路でトランジスタは,自己バイアス型エミッタ接地増幅回路として動作しています.帰還回路の部分を1本の抵抗に簡略化したものが図3になります.

自己バイアス型エミッタ接地増幅回路となっている.

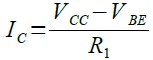

エミッタ接地増幅回路なので,出力(OUT)は入力(IN)と逆位相となり,反転増幅回路として働きます.この回路は,R2によりコレクタからベースに帰還がかかっており,Out端子の電圧はQ1のベース・エミッタ間電圧(VBE)とほぼ同じになります.そのため,トランジスタQ1のコレクタ電流(IC)は式1で計算することができます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

さらにQ1のgmは,式2で計算することができます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

k:ボルツマン定数,T:絶対温度,q:電子電荷

k:ボルツマン定数,T:絶対温度,q:電子電荷

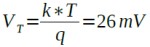

計算を簡単にするため,R2がR1よりも十分大きいものとすると,IN端子からOUT端子までのゲイン(G)は式3で計算することができます.式3より自己バイアス型エミッタ接地増幅回路のゲインは負荷抵抗(R1)の電圧降下をVTで割ったもので,図1の場合は88倍(39dB)になります.

・・・・・・・(3)

・・・・・・・(3)

実際のゲインは,R2の影響を受けるため,この値よりも若干小さくなります.

●抵抗とコンデンサによる移相回路

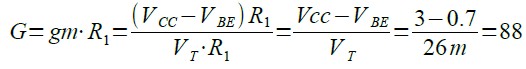

図1では,抵抗とコンデンサによるローパス・フィルタで移相回路を構成しています.図1のR1とC1の部分は,トランジスタを電流源と考えると図4の(A)のようになります.R1の一端は,実際に電源に接続されています.しかし,交流的には,GNDに接続されているとみなせます.また,図4の(A)の回路の電流源を電圧源に置き換えると図4の(B)のようになり(IoT時代のLTspiceアナログ回路入門 002電圧源回路と等価な電流源回路図 参照),一般的なローパス・フィルタとなることが分かります.

一般的なローパスフィルタとなっていることが分かる.

図1の(A)の移相回路は,このローパス・フィルタを2段縦続接続したものです.また,図1の(B),(C),(D)の移相回路は,それぞれ,このローパス・フィルタを3段,4段,5段縦続接続したものとなっています.

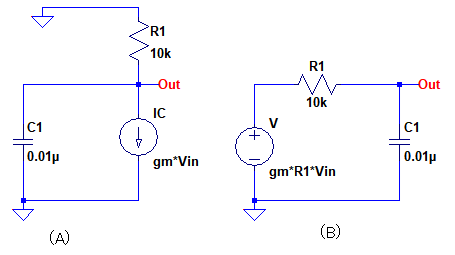

図5は,この移相回路の特性をシミュレーションするための回路です.図1の4種類と図4の回路を1つの回路図にまとめ,周波数特性をシュミレーションします.

図1の4種類と図4の回路をまとめて周波数特性をシュミレーションする.

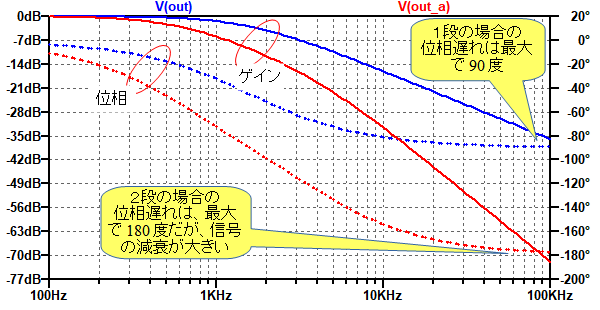

図6は,図5のローパス・フィルタ1段(Out)と2段(Out_A)のシミュレーション結果です.ローパス・フィルタ1段の場合は,出力信号の位相は最大で90度遅れます.ローパス・フィルタを2段縦続接続した場合は,最大で180度位相が遅れますが,その時は信号が大きく減衰しています.

2段縦続接続した場合は,最大で180度位相が遅れるが減衰が大きい.

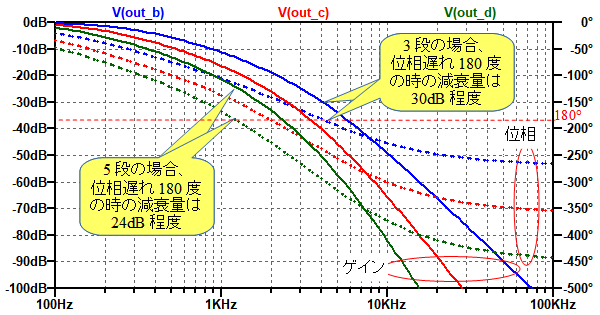

図7は,図5のローパス・フィルタ3段(Out_B),4段(Out_C),5段(Out_D)を縦続接続した場合の周波数特性のシュミレーション結果です.

3段縦続接続の場合,位相遅れ180度になる周波数での減衰量は30dB程度.

ローパス・フィルタ3段縦続接続した場合は,位相遅れが180度になる周波数での減衰量は30dB程度です.4段,5段の場合は位相遅れが180度になる周波数での減衰量はそれぞれ,25dB,24dBとなっています.移相発振回路に使用した場合,反転増幅回路のゲインがこの減衰量よりも大きければ,発振することになります.式3で計算した自己バイアス型エミッタ接地増幅回路のゲインは39dBだったため,ローパス・フィルタを3段以上縦続接続すれば,発振条件を満足することになります.

●移相型発振回路の発振確認

図8は,図1の(A)~(D)の移相型発振回路が実際に発振するかどうかを確認するための回路です.トランジェント解析を行いますが,startupオプションを付けて解析開始時に電源を0Vから3Vに立ち上げるようにしています.

startupオプションを付けて解析開始時に電源を0Vから3Vに立ち上げる.

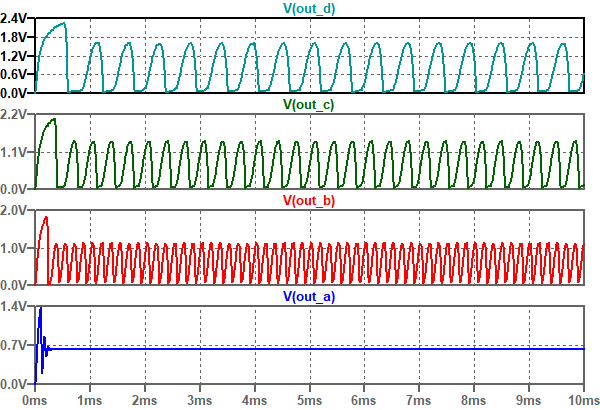

図9は,図8の解析結果です.回路(A)は発振していません.(B)~(D)は,それぞれ異なる周波数で発振していることが分かります.発振周波数は,図7のシュミレーション結果のように,それぞれの移相回路で位相が180度遅れる周波数です.

(A)は発振してないが,(B)~(D)はそれぞれ異なる周波数で発振している.

以上,移相型発振回路について解説しました.今回は,ローパス・フィルタによる移相回路を使用しましたが,移相回路にハイパス・フィルタを使用しても移相型発振回路を構成することができます.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice4_043.zip

●データ・ファイル内容

RC_LPF.asc:図5の回路

PS_LP_OSC.asc:図8の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs