高速データ伝送が可能なLVDS

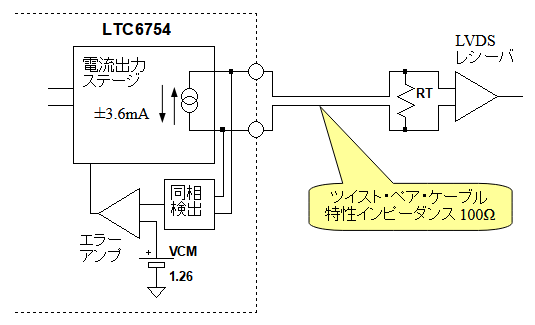

図1は,高速コンパレータ(LTC6754)の低電圧差動信号伝送(Low Voltage Differential Signaling:LVDS)出力を使用した,高速信号伝送回路です.

LT6754の出力は,特性インピーダンス100Ωのツイスト・ペア・ケーブルを介して,LVDSレシーバ回路に入力されます.

図1のLVDSレシーバの入力端にある抵抗(RT)の値は(a)~(d)のどれが適切でしょうか.

LT6754の内部ブロック図(1)は,出力段のみを取り出したものとなっている.

(a) 50Ω (b) 100Ω (c) 200Ω (d) ∞(オープン)

LVDSは,2本の信号線を使用した,差動データ伝送の規格で,出力は電流出力となっています.また,ツイスト・ペア・ケーブルで高速に信号を伝送する場合は,終端に適切な抵抗を接続する必要があります.

特性インピーダンスが100Ωのツイスト・ペア・ケーブルを使用する場合,特性インピーダンスと同じ値の終端抵抗を接続します.また,LVDSの規格でも,電流出力を電圧に変換するための終端抵抗は,100Ωとすることが定められています.

●LVDSとは何か

LVDSは,低振幅(350mV)な差動信号を使用して,高速にデータ伝送を行う規格です.信号振幅を小さくすることで,ロー・レベルから,ハイ・レベルに遷移する時間が短くなり,高速なデータ伝送が可能になります.

また,差動信号は,コモン・モード・ノイズの影響を受けにくく,外来ノイズに強くなります.

さらに,差動信号とすることで,2本の信号線から放射される電磁ノイズが打ち消し合い,外部へのノイズ放出が少なくなります.

これらの特長から,LVDSは液晶ディスプレイとのインターフェースや,その他のデータ通信に広く使われています.

●LVDSの信号波形

LVDSの信号レベルは350mVですが,信号を出力するドライバ回路は,電圧出力ではなく,3.5mAの電流出力になっています.この電流出力を,レシーバ側の100Ωの抵抗で,350mVの電圧に変換します.

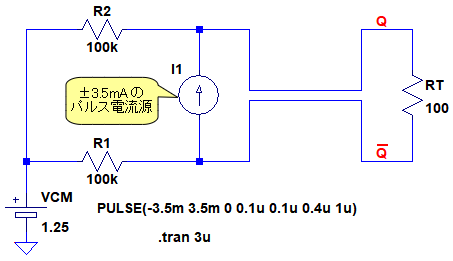

図2は,LVDSの信号波形をシミュレーションするための回路です.

I1は±3.5mAのパルス電流源で,RTが電流を電圧に変換するための100Ωの抵抗.

I1は±3.5mAのパルス電流源で,RTが電流を電圧に変換するための100Ωの抵抗です.また,VCMは同相電圧を設定するための電源で,R1,R2を介して出力信号の同相電圧を1.25Vにバイアスします.なお,LVDSの規格では,この同相電圧は1.125V~1.375Vの範囲とすることが定められています.

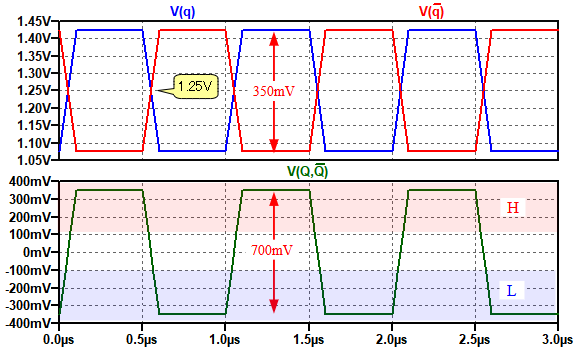

図3は,LVDSの信号波形で,図2のシミュレーション結果です.

上段:QとQをそれぞれ単独でプロットした波形.

下段:QとQの差電圧をプロットした波形.

上段は,QとQをそれぞれ単独でプロットしたものです.QとQは,それぞれ逆位相となっており,その振幅が350mVとなっています.また,同相電圧は1.25Vとなっていることが分かります.

下段は,QとQの差電圧です.差電圧の振幅は,単独振幅の2倍の700mVとなっています.レシーバ側では,+100mV以上を“H”(High)と認識し,-100mV以下を“L”(Low)と認識することになっています.

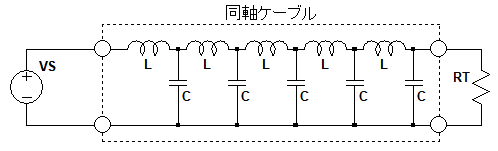

●伝送線路と特性インピーダンス

同軸ケーブルやツイスト・ペア・ケーブルのような伝送線路は,図4のように,無数のコイルとコンデンサから構成れた,分布定数回路として扱う必要があります.この等価回路の,インダクタンス(L)と容量(C)の比の平方根を,特性インピーダンス(Z0)といい,式1で表されます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

一般的な同軸ケーブルの特性インピーダンスは,50Ωとなるように設計されています.そして,同軸ケーブルの終端に,特性インピーダンスと同じ値の抵抗(RT)を接続した場合に,最も信号の劣化が少なくなります.

無数のコイルとコンデンサから構成れている.

●LTspiceの伝送線路

LTspiceには,伝送線路をシミュレーションするための素子として,損失の無い(ロスレス)伝送線路の「TLINE」と,損失のある「LTLINE」の2種類が用意されています.

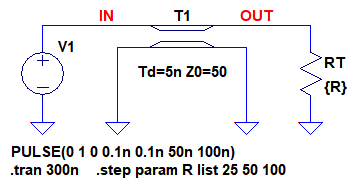

図5は,損失の無い伝送線路のTLINEを使った伝送線路をシミュレーションするための回路図です.TLINEのパラメータとして遅延時間(Td=5n)と特性インピーダンス(Z0=50)を設定しています.

特性インピーダンス50Ωで,長さ1m程度の同軸ケーブルと等価な回路となっています.この回路で,終端抵抗(RT)の値を25Ω,50Ω,100Ωと変化させたシミュレーションを行います.

終端抵抗(RT)の値を25Ω,50Ω,100Ωと変化させたシミュレーションを行う.

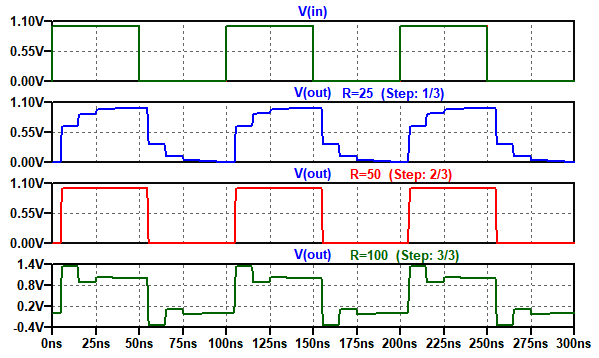

図6が図5のシミュレーション結果です.上段が入力信号の波形で,2段目が「RT=25Ω」,3段目が「RT=50Ω」,4段目が「RT=100Ω」の時のOUT端子の波形です.

3段目のRT=50Ω以外は,出力波形が変形している.

3段目のRT=50Ω以外は,出力波形が変形していることが分かります.このように,伝送線路では,終端抵抗の値を特性インピーダンスと同じになるようにする必要があります.

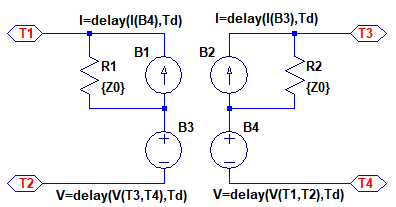

●TLINEは同相電圧を伝達できない

SPICEのロスレス伝送線路(TLINE)の等価回路は,図7(2)のような等価回路となっています.T1,T2とT3,T4は回路的には分離されており,B1~B4のビヘイビア電源によって,遅延した電圧と電流を相互にやりとりするような回路となっています.B2はB3に流れる電流と同じ値でTdだけ遅延した電流を流し,B4はT1とT2の差電圧をTdだけ遅延させた電圧を出力します.

T1,T2とT3,T4は回路的には分離されており,ビヘイビア電源によって信号を伝達している

このように,T1,T2からT3,T4に伝達されるのは,T1,T2の差電圧です.そのため.T1,T2の電圧がGNDに対していくつになっているかという,同相電圧の情報は伝達することができません.TLINEをツイスト・ペア・ケーブルのような差動信号の伝送線路として使用する場合は,この点に注意が必要です.

●LVDS信号伝送を検証する

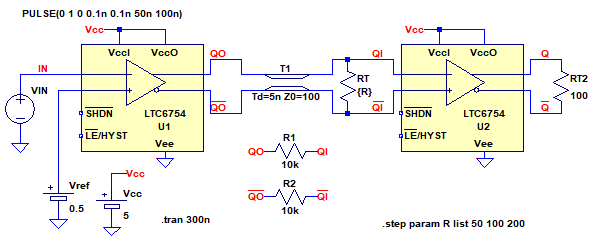

図8は2つのLTC6754を使用して,LVDS信号伝送を検証するための回路図です.

伝送線路(T1)は遅延時間5nsで特性インピーダンスは100Ωに設定している.

左側のLTC6754(U1)のLVDS出力を,ツイスト・ペア・ケーブル相当の伝送線路(T1)に接続しています.T1は遅延時間5nsで特性インピーダンスは100Ωに設定しています.T1の終端抵抗(RT)の値を,「.step」コマンドで50Ω,100Ω,200Ωと変化させます.T1の出力(QIとQI)は右側のLTC6754(U2)の入力に加えられています.なお,T1は同相電圧を伝えることができないため,抵抗(R1,R2)を使用して,QOとQOの同相電圧をQIとQIに伝えています.

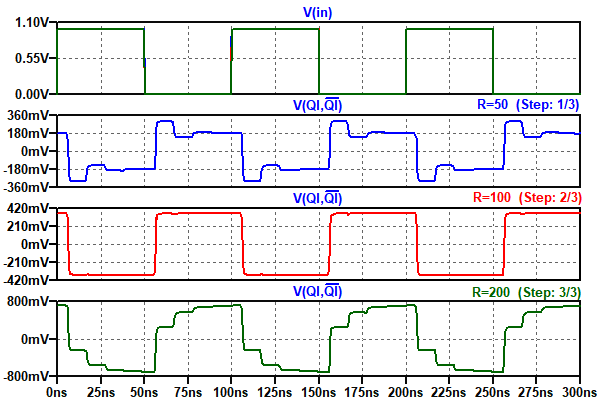

図9は,図8のシミュレーション結果です.1段目が入力信号で,2段目~4段目がQIとQIの差電圧です.

終端抵抗を100Ωとした3段目以外は,波形が乱れている.

終端抵抗を100Ωとした3段目以外は,波形が乱れていることが分かります.

以上,LVDSについて解説しました.LVDSを使用した製品の実装方法に関しては,AN-1177:LVDS/M-LVDS回路の実装ガイド(3)を参照してください.

◆参考・引用*文献

(1)LTC6754データシート:アナログデバイセズ

(2)SPICEの伝送線路モデルを使って遅延信号を作ってみる(図9:ロスレス伝送線路の基本モデル):アナログデバイセズ

(3)LVDS/M-LVDS回路の実装ガイド:アナログデバイセズ

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice11_039.zip

●データ・ファイル内容

LVDS.asc:図2の回路

LVDS.plt:図3のグラフを描画するためのPlot settinngsファイル

TLINE.asc:図5の回路

TLINE.plt:図6のグラフを描画するためのPlot settinngsファイル

LTC6754.asc:図8の回路

LTC6754.plt:図9のグラフを描画するためのPlot settinngsファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs