フォト・ダイオードを入力にしたTIAの出力雑音電圧の実効値

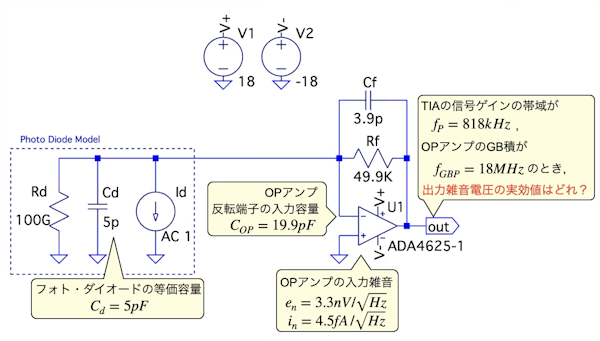

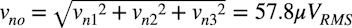

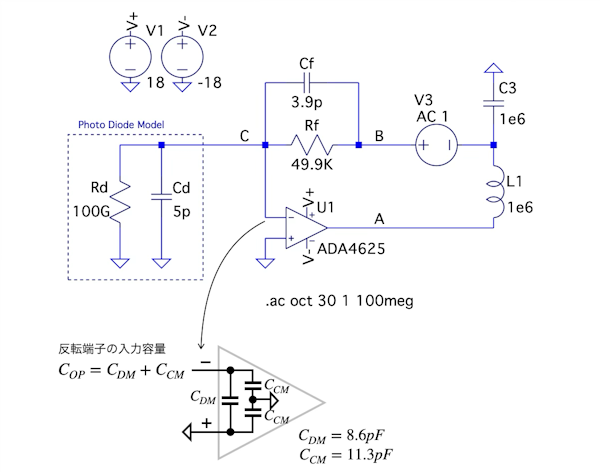

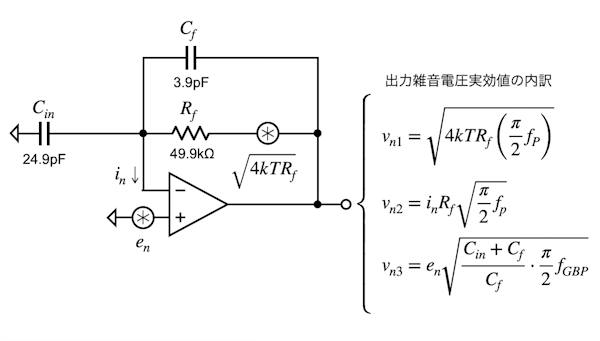

図1は,低雑音のJFET入力OPアンプ(ADA4625-1)を使ったトランスインピーダンス・アンプ(TIA:Transimpedance Amplifier)です.このTIA回路は,点線で囲ったフォト・ダイオード・モデルの電流信号を電圧に変換してoutから出力します.図1において,出力雑音の実効値は(a)~(d)のどれでしょうか.ただし,回路条件は次になります.

●回路条件

・フォト・ダイオードの入力容量:Cd=5pF

・OPアンプの反転端子の入力容量:COP=19.9pF

・OPアンプの入力雑音電圧:en=3.3nV/√Hz

・入力雑音電流:in=4.5fA/√Hz」

・TIAの信号ゲインの帯域:fP=818kHz

・OPアンプのGB積:fGBP=18MHz

(a) 38μVRMS (b) 58μVRMS (c) 70μVRMS (d) 85μVRMS

図1の出力雑音電圧は,次の3つの雑音になります.

- 帰還抵抗(Rf)の熱雑音

- OPアンプの入力雑音電流(in)と帰還抵抗(Rf)で発生する雑音

- OPアンプの入力雑音電圧(en)をTIAのノイズ・ゲイン(NG)で増幅した雑音

雑音電圧の実効値は,3つの雑音に各雑音の雑音帯域幅をかけると求められます.3つの雑音電圧実効値を総合するとoutの雑音電圧実効値になります.

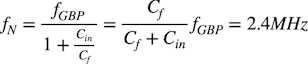

帰還抵抗(Rf)の熱雑音による実効値をvn1,OPアンプの入力雑音電流(in)と帰還抵抗(Rf)で発生する雑音の実効値をvn2,TIAのノイズ・ゲインとOPアンプの入力雑音電圧(en)で発生する雑音の実効値をvn3とします.outの出力雑音電圧の実効値は,vn1,vn2,vn3の二乗和平方根で求められます.

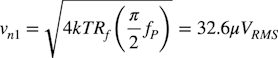

vn1は,帰還抵抗(Rf)の熱雑音に,TIAの帯域から求められる雑音帯域幅をかけた値なので式1になります.

・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・(1)

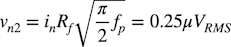

vn2は,入力雑音電流(in)と帰還抵抗(Rf)で発生する雑音に,TIAの帯域から求められる雑音帯域幅をかけた値なので式2になります.JFET入力OPアンプの入力雑音電流は非常に低いので,式2の雑音は低くなります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

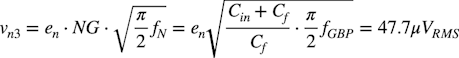

vn3は,入力雑音電圧(vn)をノイズ・ゲイン(NG)で増幅した雑音に,fNによる雑音帯域幅をかけた値になので式3になります.

・・・・・・・・・・・(3)

・・・・・・・・・・・(3)

式3のノイズ・ゲインは「NG=1+Cin/Cf」になります.ここでCinはフォト・ダイオードの容量(Cd)とOPアンプの入力容量を加えた並列容量「Cin=Cd+COP」です.式3のfNはOPアンプのオープン・ループ・ゲインとノイズ・ゲインが交差する周波数になり「fN= fGBP/NG」になります.

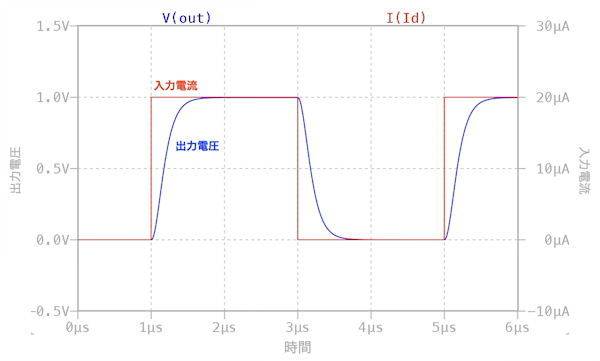

outの出力雑音電圧の実効値は,vn1,vn2,vn3の二乗和平方根で求まり,式4になるります.

・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・(4)

式4より,(b) 58μVRMSが正解になります.式1の抵抗(Rf)は電流を電圧に変換するTIAのゲインなので,必要なゲインの要求が優先です.式2と式3は低雑音のOPアンプを選ぶことで出力雑音が低くなり,全体の出力雑音電圧の実効値を低くすることができます.

●入力のフォト・ダイオード

図1は,ADA4625-1(1)のデータシートP24~P26にあるアプリケーション回路で,フォト・ダイオードの電流信号を電圧に変換するTIAになります.図1のフォト・ダイオードは,Id,Cd,Rdを使ったモデルで表しています.ここで,Idがフォト・ダイオードの光電流,Cdが等価容量,Rdが等価抵抗です.

●JFET入力のOPアンプ

ADA4625-1は,JFETの差動対が入力段になるOPアンプで,高い入力インピーダンス,低い入力バイアス電流が特徴です.TIAにJFET入力のOPアンプを用いると,入力バイアス電流に関する出力オフセット電圧が低くなり,DC特性が優れます.また,低入力バイアス電流なので入力雑音電流も低くなり,入力雑音電流に関する出力雑音電圧も低くなる利点があります.このような特徴からTIAはJFET入力OPアンプを用います.

●TIAの出力雑音電圧の実効値

フォト・ダイオードを入力にしたTIAは,フォト・ダイオードとOPアンプの接続部に付く容量が大きくなります.具体的にはフォト・ダイオードの等価容量とJFET入力OPアンプの入力容量の並列容量になります.この並列容量があると負帰還が不安定になるため,図1の帰還容量(Cf)で補償をします.Cfで補償をすると,TIAのノイズ・ゲインが高くなる周波数帯があるので注意が必要です.本稿ではフォト・ダイオードを入力にしたTIAの出力雑音電圧の実効値の求め方を解説します.

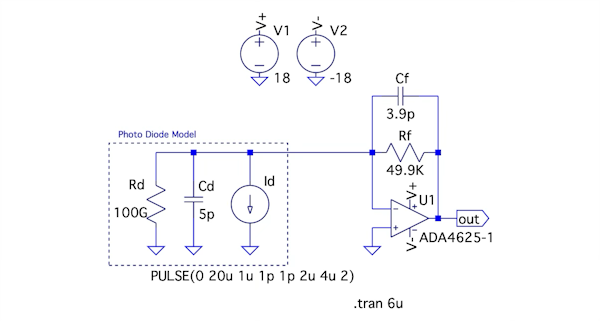

●TIAの動作

先に,フォト・ダイオードを入力にしたTIAの動作について確認します.図2は,フォト・ダイオードの電流(Id)の矩形波(振幅20μA,on時間2μA,周期4μs)がTIAに加わったとき,outの時間変化をシミュレーションする回路になります.シミュレーションはtran解析で0μs~6μsの過渡解析です.

図3は,図2のシミュレーション結果になります.図3より,入力電流(Id)を,Rfで電圧変換して,outから出力する動作になります.実機では図3の出力電圧に式4の雑音が重畳された波形になります.

●負帰還を補償したときのノイズ・ゲイン

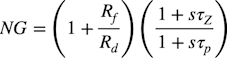

TIAのノイズ・ゲインは,式3のようにOPアンプの入力雑音電圧を増幅します.ここでは図4を用い,Cfによる負帰還の補償でノイズ・ゲインの周波数特性がどのようになるのかを調べます.

図4のADA4625-1の入力容量は,差動モードのCDMと同相モードのCCMがOPアンプ内部にあり,データ・シートの規格には「CDM=8.6pF」,「CCM=11.3pF」と記載されています.

ループ・ゲイン,ノイズ・ゲイン,OPアンプのオープン・ループ・ゲインをシミュレーションします.

OPアンプの非反転端子はGNDなので,反転端子に見えるOPアンプの入力容量は式5になります.式5の反転端子に見える入力容量は図4の回路図には記載が無く,OPアンプのモデル内にあることに注意してください.

・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・(5)フォト・ダイオードとTIAの接続部(図4のCのラベル)に見える合計の容量は,フォト・ダイオードの等価容量(Cd)と式5のOPアンプの入力容量(COP)を加えた並列容量なので式6になります.この並列容量により負帰還が不安定になるので,Cfで補償しています.

・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・(6)ノイズ・ゲインの周波数特性は,Cfによる負帰還の補償に関係しています.負帰還の補償の効果はノイズ・ゲイン,ループ・ゲイン,OPアンプのオープン・ループ・ゲインの関係から分かります.図4中のA,B,Cのラベルを用いると,ノイズ・ゲインは「V(b)/V(c)」,ループ・ゲインは「V(a)/V(b)」,オープン・ループ・ゲインは「V(a)/V(c)」になります.シミュレーションは「.ac」コマンドを用いて,1Hz~100MHz間を周波数が2倍あたり30ポイントでスイープします.

●負帰還のノイズ・ゲインの確認

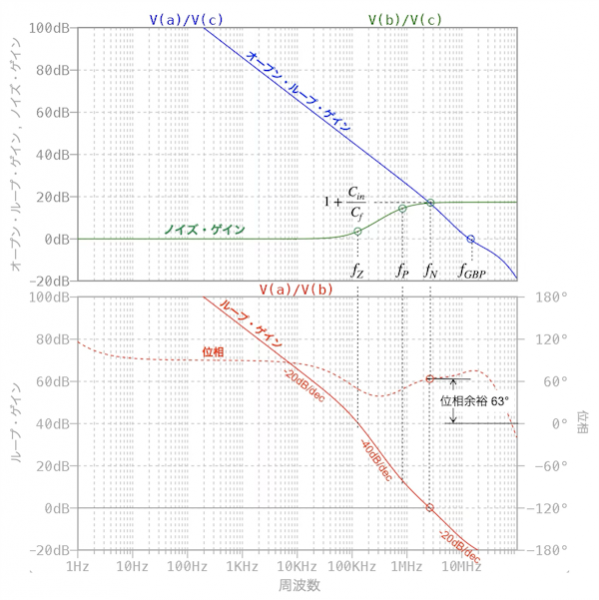

図5は,図4のシミュレーション結果になります.図5の上段はノイズ・ゲインとOPアンプのオープン・ループ・ゲインをプロット,図5の下段はループ・ゲインと位相をプロットしました.

上段はノイズ・ゲインとOPアンプのオープン・ループ・ゲインをプロット.

下段はループ・ゲインと位相をプロット.

Cfを使った負帰還の補償の効果は次になります.

- ノイズ・ゲインがfZの周波数を過ぎると,ループ・ゲインは-20dB/decから-40dB/decの傾きに変わり,位相が遅れ始める

- ノイズ・ゲインがfPの周波数を過ぎると,ループ・ゲインは-40dB/decから-20dB/decの傾きに戻り,遅れた位相を戻して補償する

- オープン・ループ・ゲインとノイズ・ゲインが交差する周波数fNよりfPが低い周波数のとき,位相余裕が生まれる

- ループ・ゲインが0dBのときの位相余裕を調べると63°になる.一般的に位相余裕は60°以上で安定なので,図1の負帰還は安定する

- ノイズ・ゲインがfPより高い周波数のとき,帰還回路がCinとCfによる非反転アンプのゲインになり,「NG=1+Cin/Cf」に落ち着く.このノイズ・ゲインがOPアンプの入力雑音電圧を増幅する

図5のfZ,fP,fNは,次の計算で分かります.負帰還を補償するときは,fZ,fP,fNの周波数位置が図5のような関係になるように,Cfを調整します.

図4のノイズ・ゲインを机上計算すると式7になります.

・・・・・・・・・・・・・・・・・・・・・・・・・(7)

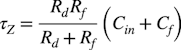

・・・・・・・・・・・・・・・・・・・・・・・・・(7)ここでτZは式8になります.式8の右辺の項で「RdRf/(Rd+Rf)=Rd||Rf」なので,RdとRfの並列抵抗を意味します.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)そしてτPは,式9になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(9)

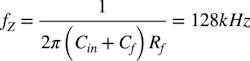

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(9)式8のRdとRfの大小関係は「Rd>>Rf」なので,fZは式10になります.

・・・・・・・・・・・・・・・・・・・・・・・(10)

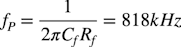

・・・・・・・・・・・・・・・・・・・・・・・(10)式9よりfPは式11になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(11)

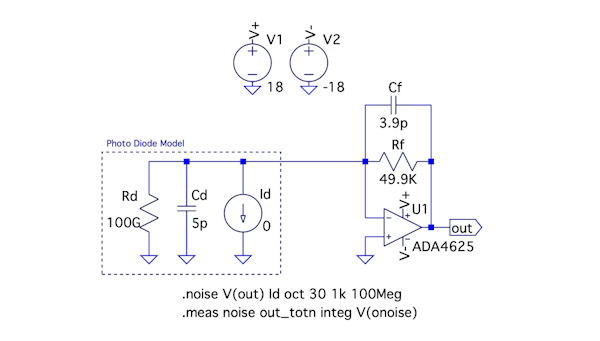

・・・・・・・・・・・・・・・・・・・・・・・・・・・(11)fNは,OPアンプのGB積の周波数と,fP以上の周波数で落ち着いたノイズ・ゲイン「1+Cin/Cf」から分かり,式12になります.

・・・・・・・・・・・・・・・・・・・(12)

・・・・・・・・・・・・・・・・・・・(12)

●出力雑音電圧の実効値を計算

次にフォト・ダイオードを入力にしたTIAの出力雑音電圧の実効値について,図6を用いて机上計算します.図6のCinは式6の容量です.

図1のRdはRfに比べ非常に高い抵抗であり,Rdはオープン(回路に無い)と考えることができるので図6にはありません.図6には雑音源として「抵抗の熱雑音電圧」,「OPアンプの入力雑音電圧」,「OPアンプの入力雑音電流」の3つあり,これらの雑音が出力雑音電圧の実効値になります.その内訳として,帰還抵抗(Rf)の熱雑音による実効値をvn1,OPアンプの入力雑音電流(in)と帰還抵抗(Rf)で発生する雑音の実効値をvn2,TIAのノイズ・ゲインとOPアンプの入力雑音電圧(en)で発生する雑音の実効値をvn3とします.

▼vn1の計算

- 帰還抵抗(Rf)の√Hzあたりの熱雑音電圧は,(4kTRf)1/2になる.ここで,k:ボルツマン定数(1.381×10-23),T:絶対温度(27℃のとき300ケルビン)

- vn1の雑音帯域幅は,TIAの信号ゲインの帯域(fP)が関係する.fPは式11より「fP=818kHz」になる.信号ゲインは,fPの周波数より高くなると-20dB/decの傾きで減衰する特性なので,雑音帯域幅はfPよりπ/2倍だけ高い周波数になる

- vn1は「√Hzあたりの熱雑音電圧」に「雑音帯域幅」をかけた値なので,前述の式1の「vn1=32.6μVRMS」になる

▼vn2の計算

- 入力雑音電流(in)と帰還抵抗(Rf)で発生する√Hzあたりの雑音電圧は「in*Rf」

- vn2の雑音帯域幅はvn1と同じになる

- vn2は「√Hzあたりのin*Rfの雑音電圧」に「雑音帯域幅」をかけた値なので,前述の式2の「vn2=0.25μVRMS」になる

▼vn3の計算

- TIAのノイズ・ゲインとOPアンプの入力雑音電圧(en)で発生する√Hzあたりの雑音電圧は,ノイズ・ゲインをNGとすると「en*NG」になる

- fP付近のノイズ・ゲインは「NG=1+Cin/Cf」にり,ここでCinはフォト・ダイオードの容量CdとOPアンプの入力容量を加えた並列容量「Cin=Cd+COP」になる

- OPアンプのオープン・ループ・ゲインとNGが交差する周波数を見積もると「fN= fGBP/NG」になる.fGBPはデータシートの規格より18MHzになる

- vn3の雑音帯域幅は,オープン・ループ・ゲインとNGが交差する周波数(fN)が関係します.fNは,式12より「fN=2.4MHz」です.オープン・ループ・ゲインはfNの周波数より高くなると-20dB/decの傾きで減衰する特性なので,雑音帯域幅はfNよりπ/2倍だけ高い周波数になる

- vn3は「√Hzあたりのen*NGの雑音電圧」に「雑音帯域幅」をかけた値なので,整理すると前述の式3の「vn3=47.7μVRMS」になる

▼出力雑音電圧の実効値

- outの出力雑音電圧の実効値は,vn1,vn2,vn3の二乗和平方根で求められ,前述の式4で求めた 57.8μVRMSになる

- 入力雑音電流が関係するvn2は,他のvn1,vn3より十分低いので,出力雑音電圧の実効値はvn1,vn3の2つでほぼ決まります.この検討より,TIAの出力雑音電圧の実効値は,JFET入力OPアンプを使うと入力雑音電流の影響が低くなる

このらの机上計算より,問題の答え合わせをすると,(b)58μVRMSが正解になります.

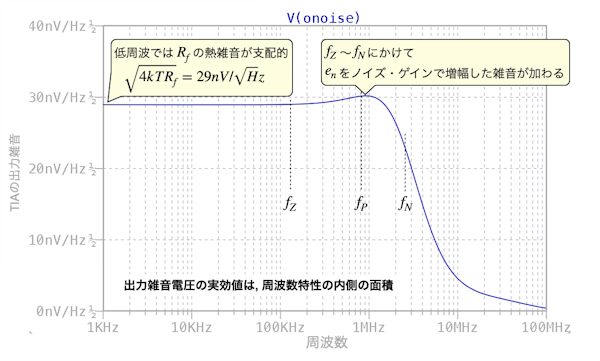

●TIAの出力雑音電圧の確認

最後に,図7を使ってフォト・ダイオードを入力にしたTIAの出力雑音電圧をシミュレーションで調べます.

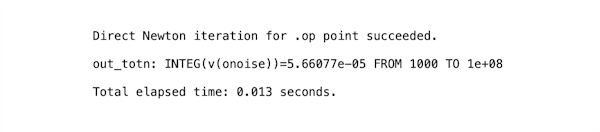

シミュレーションは「.noise」コマンドを用い,1kHz~100MHz間を周波数が2倍あたり30ポイントのスイープになります.シミュレーション結果は「.meas」コマンドを用い,outの出力雑音電圧を積分して実効値を自動計算し,out_totnの変数に入れます.

図8は,図7のシミュレーション結果になります.fZより低い周波数ではRfの熱雑音が支配的になります.fZ~fNにかけて,OPアンプの入力雑音電圧(en)をノイズ・ゲインで増幅した雑音が加わるのが分かります.

図9は,出力雑音の実効値を「.measコマンド」で自動測定した結果のログ・ファイルになります.図9のout_totnの変数の値は56.6μVRMSとなり,解答(b)の58μVRMSに近い実効値になるのが分かります.

出力雑音電圧の実効値は56.6μVRMS.

以上,フォト・ダイオードを入力にしたTIAの出力雑音電圧について解説しました.実機ではフォト・ダイオードとOPアンプの接続部に基板の浮遊容量も加わります.浮遊容量を予測するのは難しいこともあり,シミュレーションと実機の双方で調整していくことになります.

◆参考・引用*文献

(1) ADA4625-1のデータシート:アナログデバイセズ

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice11_038.zip

●データ・ファイル内容

TIA ADA4625 Tran.asc:図2の回路

TIA ADA4625 Tran.plt:図2のプロットを指定するファイル

TIA Characteristics.asc:図5の回路

TIA Characteristics.plt:図5のプロットを指定するファイル

TIA_ADA4625 Noise.asc:図7の回路

TIA_ADA4625 Noise.plt:図7のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs