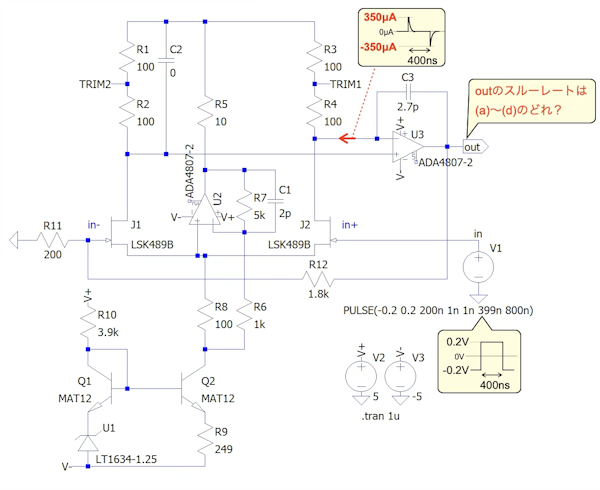

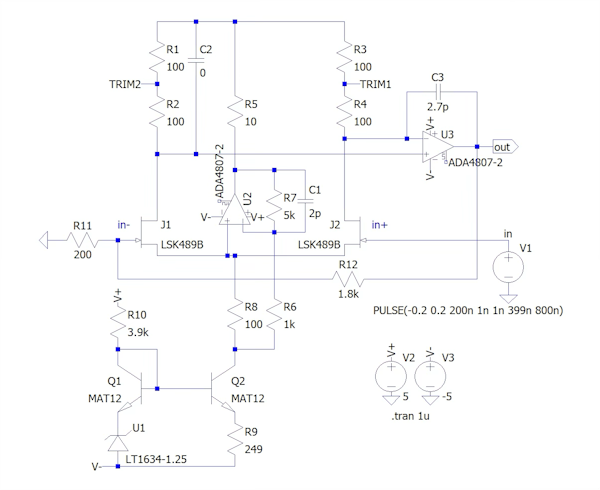

JFETとOPアンプ,電圧リファレンスを使った複合アンプ

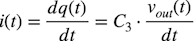

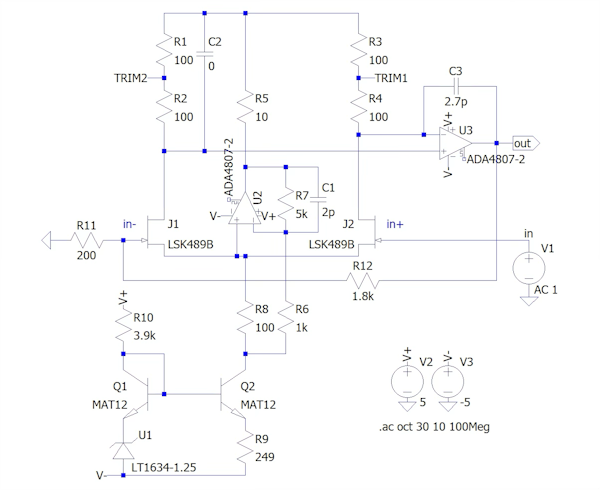

図1は,接合型電界効果トランジスタ(JFET:LSK489B)と高速入出力レール・ツー・レールのOPアンプ(ADA4807-2),出力電圧1.25V高精度シャント電圧リファレンス(LT1634-1.25)を使った複合アンプになります.入力がV1,出力がoutで,R11とR12を使って負帰還アンプを構成しています.

図1のV1に,矩形波を入力すると,JFET(J2)のドレインが繋がるノードからおおよそ±350μAの電流がコンデンサ(C3)に流れます.このとき,outのスルーレートは(a)~(d)のどれでしょうか.ただし,ADA4807-2のOPアンプのスルーレートは,複合アンプのスルーレートより速く,ADA4807-2の入力バイアス電流は0とします.

outのスルーレートは(a)~(d)のどれ?

(a) 65μV/μs (b) 130V/μs (c) 195V/μs (d) 260V/μs

スルーレートとは,矩形波を入力したとき,「1μsあたりの時間変化でoutの電圧が何V変化する」を表します.複合アンプのoutの時間変化は,J2のドレインが繋がるノードから流れる±350μAの電流とC3の容量で決まります.これをヒントに計算すると分かります.

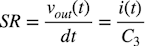

図1のスルーレート(SR)は,次の計算で求められます.

- J2のドレインが繋がるノードから流れる±350μAの電流は,OPアンプの入力バイアス電流が0なので,全てC3へ流れる

- outの電圧は,C3の2.7pFへ流れる電流で充放電されて,スルーレートが発生する

- C3の電流が+350μAのとき,スルーレートは,「SR=350μA/2.7pF=130V/μs」になる

- 同様に,C3の電流が-350μAのとき,スルーレートは,「SR=-350μA/2.7pF=-130V/μs」になる.

これより,(b)の130V/μsが正解になります.

●負帰還アンプの性能を良くする

計測機器アプリケーション向けのアンプは,高い入力インピーダンス,低い入力バイアス電流,低い入力雑音,高いスルーレートといった理想アンプに近づけた性能が必要になります.この性能を単体のOPアンプで実現するのは難しく,図1のような整合が取れた2つのJFETを入力段にし,後段は,OPアンプを用いる複合アンプで実現します.具体的には,JFETの入力段で高い入力インピーダンス,低い入力バイアス電流,低い入力雑音にします.そして後段アンプを含めた複合アンプで負帰還が発振しないように,図1のC3の容量で補償します.スルーレートは,図1のJ2のドレインが繋がるノードから流れる電流とC3の容量で決まります.

●独立した電源生成

電圧リファレンスは,その電圧とR9の抵抗によりQ2コレクタから定電流を生成します.Q2コレクタの定電流の約9割はJFET差動対のテール電流になり,約1割はJFETを使った初段アンプの独立した電源生成に使われます.この構成により,JFETの初段アンプを安定動作させます.

本稿では,図1のスルーレートについてC3の容量とその電流を使って机上計算で検討します.その後,複合アンプを使った負帰還アンプの特性として,「負帰還安定性」,「ゲインの周波数特性」,「入力雑音」,「スルーレート」について各々をシミュレーションで確認していきます.

●回路構成と直流動作点について

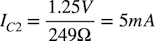

図1の複合アンプは,ADA4807-2(1)のデータシートP26,P27にあるアプリケーション回路になります.JFETの入力段は整合が取れた2つのJFETのLSK489B(2)を使います.JFETを入力段に使うと高入力インピーダンス,低入力バイアス電流,低雑音の特性なので,複合アンプ全体の性能が良くなります.図1のJFETのJ1とJ2を使った入力段の差動対を安定動作にするため,差動対のテール電流は一定になるようにしています.具体的にはQ1とQ2のベース・エミッタ間電圧が等しいとすると,LT1634-1.25(3)の電圧リファレンスとR9の抵抗により,Q2のコレクタ電流はおおよそ式1の定電流になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

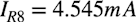

式1のコレクタ電流は,R8とR6に分流しますが,2つの抵抗の両端の電圧はOPアンプ(U2)のバーチャル・ショートで一定となり,「R8:R6=1:10」の関係から,差動対のテール電流となるR8の電流は,式2の定電流になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

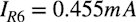

そして,R6の電流は,式3の定電流になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

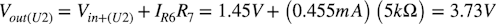

式3は,定電流であること,そしてU2とR6とR7の負帰還の効果により,U2の出力電圧は一定になります.具体的には,U2の非反転端子の電圧を調べると「Vin+(U2)=1.45V」なので,U2の出力電圧は,式4になります.

・・・・・・・・・(4)

・・・・・・・・・(4)

図1では,式4の電圧をJ1,J2,R1,R2,R3,R4の差動アンプの電源として使います.このようにすると,回路の電源であるV2とV3から独立しており,V2とV3が変動しても差動アンプは安定動作になります.

TRIM1とTRIM2は,R1,R2とR3,R4の抵抗を調整するための端子で,複合アンプの入力オフセット電圧調整に使います.C2は複合アンプのoutにリンギングがあるときに微調整する予備の容量になります.図1のC2は,今回のシミュレーションでリンギングがないので0になります.

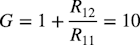

R11とR12は負帰還アンプのゲインを決める抵抗になり,図1のゲインは,式5になります.10倍のゲインをデシベルにすると20dBになります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

●スルーレートの机上計算

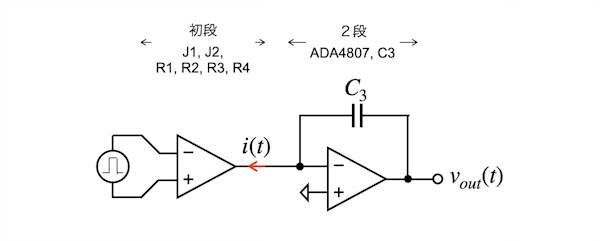

次に図1のスルーレートについて,図2のブロック図を用いて机上計算で検討します.図2の初段は図1のJFETのJ1,J2と抵抗のR1,R2,R3,R4からなるアンプ,2段目は図1のU3のOPアンプ(ADA4807)とコンデンサ(C3)のアンプになります.図2のi(t)の電流は図1の±350μAになります.

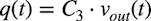

図2の初段アンプに矩形波を入力すると,矩形波の立ち上がりと立ち下がりのとき,初段の出力からi(t)の電流が流れます.2段目のアンプの入力バイアス電流は0とすると,i(t)の電流はC3のコンデンサに流れます.i(t)によるC3の電荷をq(t)とし,出力電圧をVout(t)とすると,式6の関係になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)i(t)は,q(t)を時間微分した値なので,式6を使うと式7になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)スルーレートは,1μs変化したときのVout(t)の変化量なので,式7を使うと式8になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)ここで解答の答え合わせをします.式8より,C3が2.7pF,i(t)が+350μAのとき,スルーレートは「SR=350μA/2.7pF=130V/μs」になります.同様にC3が2.7pF,i(t)が-350μAのとき,スルーレートは「SR=-350μA/2.7pF=-130V/μs」になります.これより,(b) 130V/μsが正解になります.

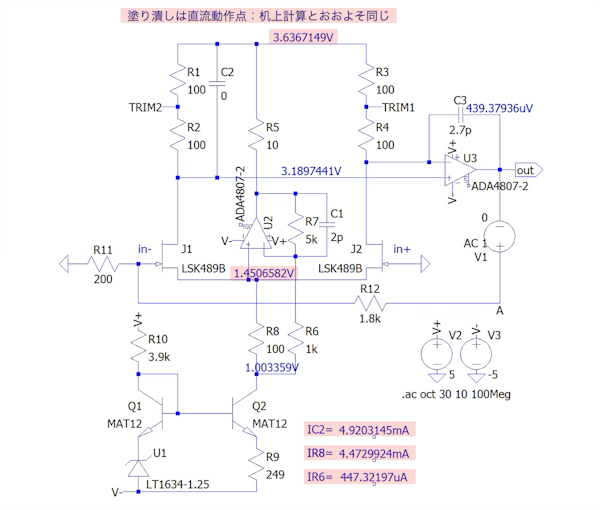

●負帰還アンプの特性と安定性

ここからは,図1の複合アンプを使った負帰還アンプの特性をシミュレーションで調べていきます.図3は,複合アンプを使った負帰還アンプの直流動作点とループ・ゲインと位相を調べる回路になります.直流動作点はシミュレーションを実行すると,図3のように回路図に表示されます.

まず,図3に示した直流動作点(赤く塗り潰した部分)について解説します.図3に示した直流動作点は,次のように,先述しました式1~式4の値とほぼ同じになるのが分かります.

- 式1のIC2のQ2のコレクタ電流(5mA)

- 式2のIR8の電流(4.545mA)

- 式3のIR6の電流(0.455mA)

- シミュレーションで示したU2の非反転端子の電圧(1.45V)

- 式4のU2の出力電圧(3.73V)

また,図3では,式4のU2の出力電圧をJ1,J2,R1,R2,R3,R4の差動アンプの電源として使い,回路の電源(V2とV3)から独立するので,一定の3.64Vになります.

次に図3を使い,複合アンプを使った負帰還アンプのループ・ゲインを簡易的に調べます.図3の「C3=2.7pF」は負帰還を安定にするための補償コンデンサになります.シミュレーションは「.ac」コマンドを使い10Hzから100MHz間を周波数が2倍あたり30ポイントでスイープします.ループ・ゲインは,負帰還ループに入れたV1の両端のラベルAとoutを使い,「Vout/VA」の計算で求めます.

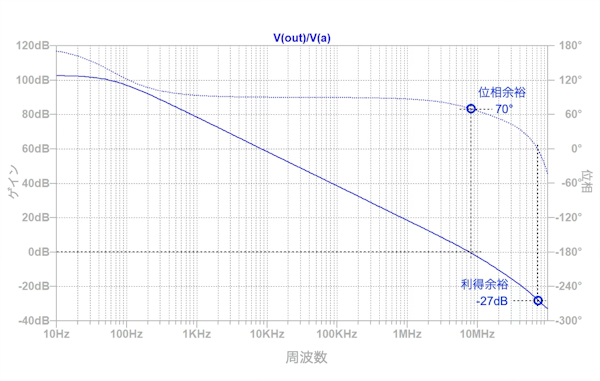

図4は,図3のシミュレーション結果で,ループ・ゲインと位相をプロットしました.図4より「C3=2.7pF」のとき位相余裕は70°,利得余裕は-27dBとなります.一般に位相余裕が60°以上で負帰還は安定ですので,図3の複合アンプも安定の判断になります.

位相余裕が70°,利得余裕が-27dB.

●負帰還アンプの周波数特性

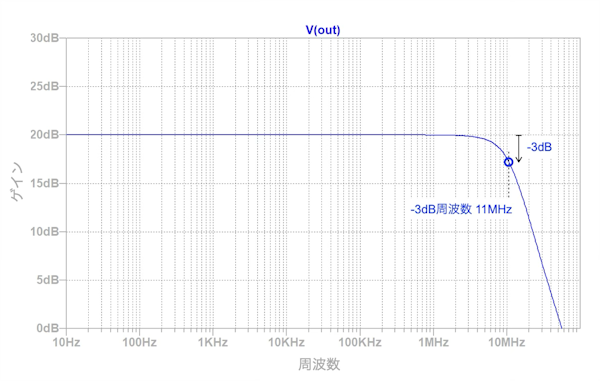

図5は,複合アンプを使った負帰還アンプのゲイン周波数特性をシミュレーションする回路になります.入力はV1で出力はoutになります.シミュレーションで使う「.ac」コマンドは図3と同じになります.

図6は,図5のシミュレーション結果で,ゲインの周波数特性をプロットしました.ゲインは,前述の式5で計算した10倍(デシベルで20dB)になります.ゲインが-3dBになる周波数は,11MHzであり広帯域のアンプになります.

-3dB周波数は11MHz.

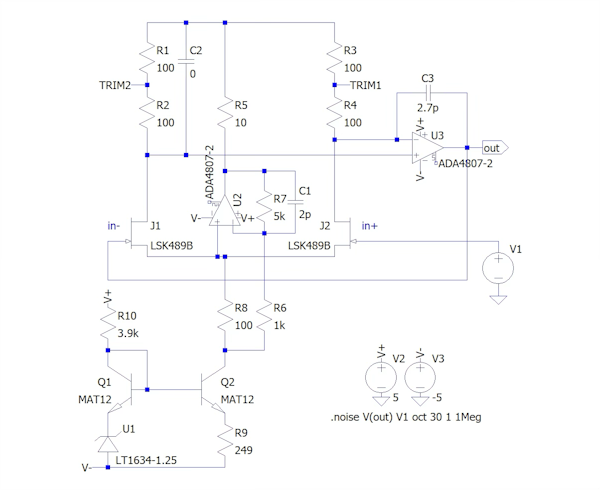

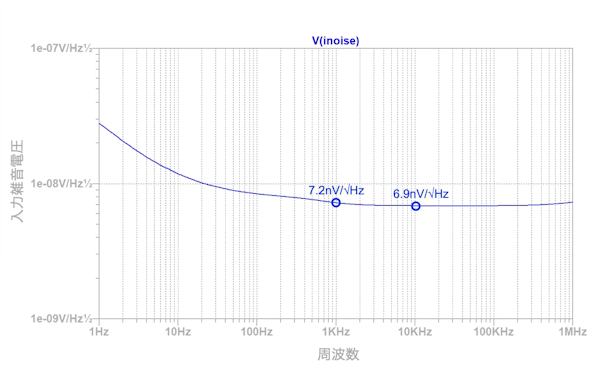

●複合アンプの入力雑音

図7は,ゲインが1倍のユニティ・ゲイン・バッファにして,複合アンプの入力雑音周波数特性をシミュレーションする回路になります.ユニティ・ゲイン・バッファにすると負帰還の抵抗が無いので,複合アンプのみの入力雑音を調べることができます.シミュレーションは「.noise」コマンドを用い,1Hzから1MHz間を周波数が2倍あたり30ポイントのスイープです.

図8は,図7のシミュレーション結果で入力雑音電圧の周波数特性をプロットしました.複合アンプの入力雑音電圧は,1kHzで7.2nV/√Hz,10kHzで6.9nV/√Hzで,10nV/√Hz以下の入力雑音が低い特性になります.

入力雑音は1kHzのとき7.2nV/√Hz,10kHzのとき6.9nV/√Hz.

●負帰還アンプのスルーレート

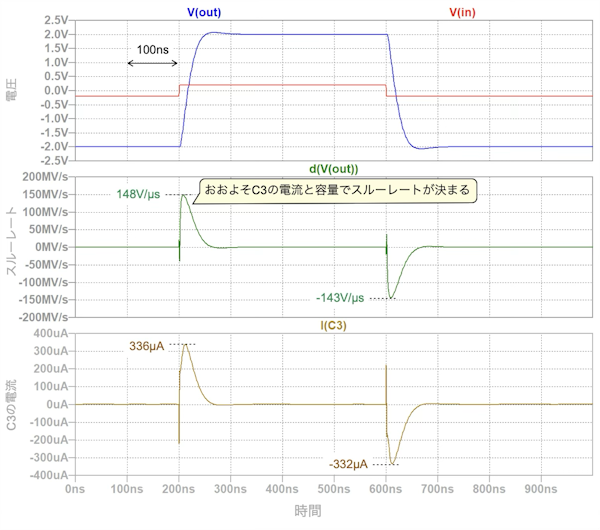

図9は,複合アンプを使った負帰還アンプの過渡応答をシミュレーションする回路になります.入力はV1で振幅が±0.2Vの矩形波になります.このときのoutの波形よりスルーレートを求めます.シミュレーションは「.tran」コマンドを用い,0μs~1μs間の過渡解析になります.

図10は,図9のシミュレーション結果になります.図10の上段はinとoutの時間応答をプロットしています.図10の中段は,outの時間微分をプロットしています.図10の下段はC3の電流をプロットしています.

- 図10の上段は,inのラベルでプロットした入力波形とoutのラベルでプロットした出力の波形になります.V1の矩形波をinのラベルでプロットすると±0.2Vの矩形波です.負帰還アンプのゲインは10倍なので,outの振幅は±2Vになります.このときの時間軸の1目盛は100nsなので,outは高速で動作しているのが分かります.

- 図10の中段は,outの波形を導関数d()を用いて時間微分したスルーレートのプロットになります.outの立ち上がりのスルーレートは148V/μs,立ち下がりが-143V/μsとなり,解答(b)の130V/μsに近いのが分かります.

- 図10の下段は,C3の電流がoutの立ち上がりで+336μA,outの立ち下がりで-332μAになり,図1に示した±350μAに近い電流でコンデンサを充放電しているのが分かります.スルーレートは,式8の検討通り,C3の容量に下段の電流が流れることにより発生します.

◆参考・引用*文献

(1) ADA4807-2のデータシート:アナログデバイセズ

(2) LSK489A/Bのデータシート:Linear Systems

(3) LT1634-1.25のデータシート:アナログデバイセズ

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice11_032.zip

●データ・ファイル内容

LSK489 ADA4807 Composite Amplifier Loop.asc:図3の回路

LSK489 ADA4807 Composite Amplifier Loop.plt:図3のプロットを指定するファイル

LSK489 ADA4807 Composite Amplifier ac.asc:図5の回路

LSK489 ADA4807 Composite Amplifier ac.plt:図5のプロットを指定するファイル

LSK489 ADA4807 Composite Amplifier noise.asc:図7の回路

LSK489 ADA4807 Composite Amplifier noise.plt:図7のプロットを指定するファイル

LSK489 ADA4807 Composite Amplifier tran.asc:図9の回路

LSK489 ADA4807 Composite Amplifier tran.plt:図9のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs