負帰還アンプで大きな負荷容量を安定に駆動する方法

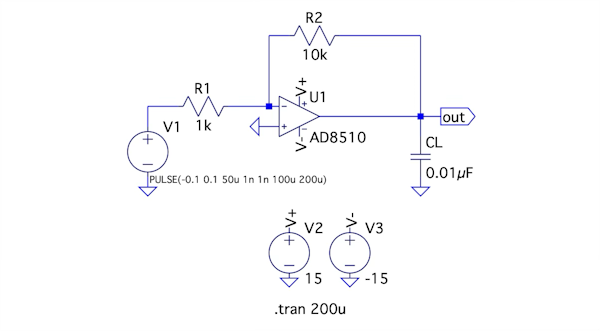

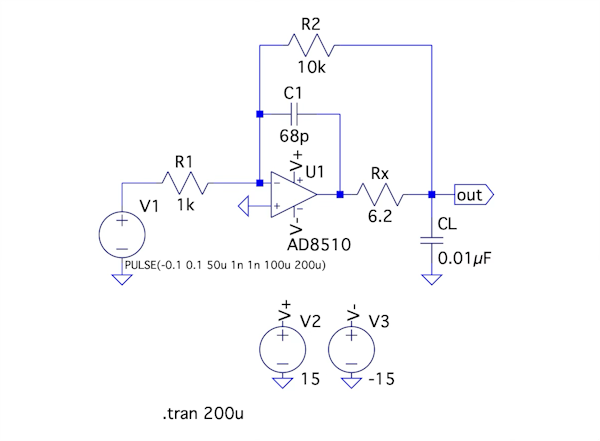

図1は,OPアンプを使用し,大きな負荷容量(CL=0.01μF)でも,安定に駆動させるために補償した負帰還アンプです.図1において,OPアンプ内部の出力抵抗が59Ωのとき,負帰還が安定動作するC1の容量として近いのは(a)~(d)のどれでしょうか.

負帰還を安定にする最適なC1の容量に近いのは(a)~(d)のどれ?

(a) 1pF (b) 4.7pF (c) 22pF (d) 68pF

図1の負帰還安定補償は,負帰還回路で生まれる極の周波数(ゲインが低下し位相が遅れ始める)とゼロの周波数(ゲインが増加し位相が進み始める)を同じ周波数にして,ゲインと位相の変化をキャンセルします.

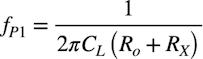

具体的には負帰還回路を場合分けし,「高周波でC1はショートとみなし,RX<<R2,Ro<<R1の条件」のときの極をfP1,ゼロをfZ1とします.

次に「負荷容量(CL)はオープンのとき」の極をfP2,ゼロをfZ2とします.2つの極とゼロの周波数を「fP1=fZ2,fP2=fZ1」にすることで補償します.図1のRXはこの条件で最適化した値を使いています.

そして残りのC1を検討します.

図1は,負帰還回路を場合分けし,ヒントに示した2つの極とゼロの周波数を「fP1=fZ2,fP2=fZ1」にすることによりRXとC1の2つを適切な値にして補償します.図1のRXは最適にした抵抗値を使用しているため,「fP1=fZ2,fP2=fZ1」のどちらかの条件でC1を検討することになります.ここでは「fP1=fZ2」の条件からC1を検討します.

- 「高周波でC1はショートとみなし,RX<<R2,Ro<<R1の条件」のとき,「Ro=59Ω,RX=6.2Ω」より,極は「fP1=1/(2πCL (Ro+RX))=243kHz」になります

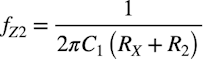

- fZ2は,「fZ2=1/(2πC1 (RX+R2))」になります

- 前述のfZ2の式を使い「fZ2=243kHz」にして「RX=6.2Ω」と「R2=10kΩ」の値を使いC1を求めると,「C1=65pF」になります

- (a)~(d)の中で近いのは「C1=68pF」になります

これよりより,(d)が正解になります.

●負荷容量により負帰還は不安定になる

終端が適切でない同軸ケーブルやノイズを除去する大きなコンデンサ等を駆動するとき,負帰還アンプは,不安定になり,リンギングや発振などの悪い影響が出てきます.

不安定になるのは,大きな負荷容量による位相の遅れが原因です.このため負帰還側で不安定にならないような対策が必要になります.図1で使用したAD8510(1)はゲインが1倍で負荷容量1000pFまで安定に動作するのが特徴ですが,それより大きな負荷容量では不安定になります.

●フィードバック内補償を使う

図1の補償方法は参考文献(2)によると「フィードバック内補償」と呼ばれています.これは補償するC1とRXが負帰還ループの内側にあることによります.

フィードバック内補償の利点として,RXを加えても負帰還ループ内にあるので,直流精度への影響は低くなります.ただし,出力振幅とスルーレートが低くならないように,RXは低い抵抗値にする必要があります.フィードバック内補償の検討にはOPアンプ内部の出力抵抗値も必要になります.

本稿では,まず大きな負帰還容量があるとき,補償前の回路では時間応答と負帰還ループの周波数特性が悪化するのを確認します.次にOPアンプ内部の出力抵抗を調べ,その後にフィードバック内補償について解説します.最後に補償後の効果をシミュレーションで確認します.

●補償前の回路の時間応答

図2は,図1の補償前の負帰還アンプで,ゲインが10倍の反転アンプです.図1と同じ大きな負荷容量(CL=0.01μF)をoutに接続しています.OPアンプは,参考文献(2)で使用しているAD8510(1)を使いました.

outに負荷容量0.01μFを接続している.

図2の回路でV1から振幅の最大が±0.1Vの矩形波を入力し,補償前の回路の時間応答をシミュレーションで調べます.シミュレーションは「.tran」コマンドを使い,200μsまでの過渡解析になります.

図3は,図2のシミュレーション結果になります.ゲインが10倍の反転アンプなので,振幅の最大は±1Vで位相は反転します.図3のプロットで,矩形波の立ち上がりと立ち下がりにリンギングが発生しています.これが負荷容量による影響になります.

outの立ち上がりと立ち下がりでリンギングが発生.

次に補償前の負帰還アンプでループ・ゲインと位相の関係を図4の回路で調べます.図4はループ・ゲインと位相を評価する回路で,LTspiceのEducationalフォルダにある「LoogGain2.asc」を編集して使用しています.この評価回路はMiddle Brook法と呼ばれるもので,正確なループ・ゲインと位相の評価ができます.ループ・ゲインと位相は次の計算式でプロットします.

シミュレーションは「.ac」コマンドを使い,周波数が1Hzから10MHz間を周波数が10倍あたり30ポイントのスイープになります.

Middle Brook法を使用する.

図5は,図4のシミュレーション結果になります.

位相余裕は27°しかなく負帰還は不安定.

1Hzからおよそ10kHz間はOPアンプの周波数特性になります.それ以上の周波数では負荷容量による位相遅れが発生し,位相余裕が27°になります.一般的に負帰還が安定に動作する位相余裕は60°が目安なので,負帰還は不安定になっているのが分かります.

●OPアンプ内部の出力抵抗を調べる

ここでは,OPアンプ内部の出力抵抗を求めるため,OPアンプのオープン・ループ・ゲインと,ユニティ・ゲイン・バッファの出力インピーダンスをシミュレーションで調べ,その2つの値から計算で求めます.

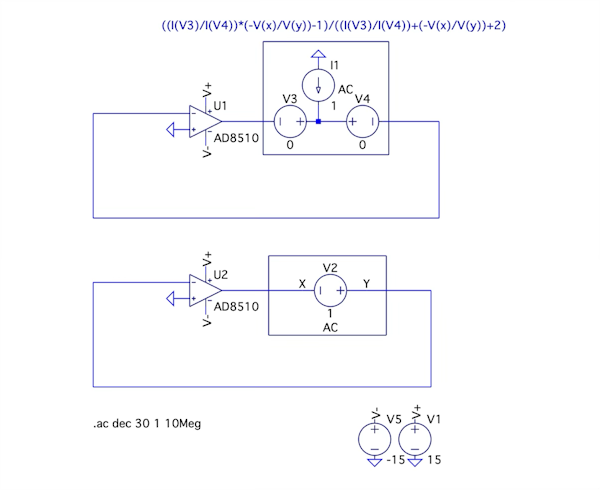

図6は,OPアンプ(AD8510)のオープン・ループ・ゲインを図4と同じMiddle Brook法で調べる回路になります.シミュレーションの設定は図4と同じです.

OPアンプの出力抵抗を求めるため,1Hzでのオープン・ループ・ゲインを調べる.

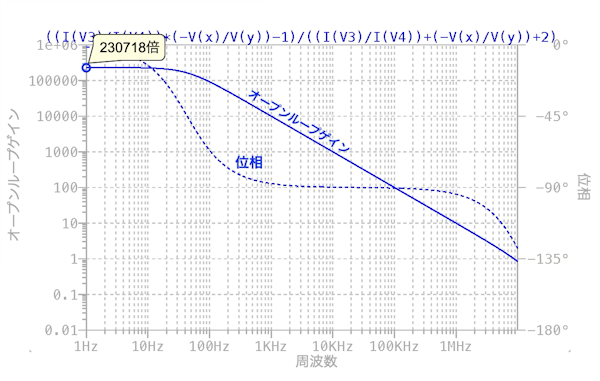

図7は,図6のシミュレーション結果になります.Y軸はデシベルからログスケールに変更してゲインを倍率で表しています.1HzでのOPアンプのオープン・ループ・ゲインを調べると230718倍になります.

1Hzでのゲインは230718倍.

図8は,OPアンプ(AD8510)を使ったユニティ・ゲイン・バッファの出力インピーダンス周波数特性を調べる回路になります.ユニティ・ゲイン・バッファの出力にテスト信号源としてI1の交流信号源を加えました.

調べた出力インピーダンスとオープン・ループ・ゲインより,OPアンプ内部の出力抵抗を計算する.

「.ac」コマンドは図4と同じです.ユニティ・ゲイン・バッファの出力インピーダンスは,負帰還の効果でOPアンプ内部の出力抵抗をオープン・ループ・ゲインで割った値になります.

図9は,図8のシミュレーション結果になります.図9のY軸は,I1の交流電流変化に対するoutの交流電圧変化の周波数特性です.これよりY軸は出力インピーダンスを表しています.図9より,1Hzでの出力インピーダンスは257μΩになるのが分かります.

ユニティ・ゲイン・バッファの1Hzでの出力インピーダンスは257μΩ.

OPアンプ内部の出力抵抗は,ユニティ・ゲイン・バッファの出力インピーダンスにオープン・ループ・ゲインを掛けた値になります.図7と図9で調べた1Hzの2つの値を使うと,AD8510の内部の出力抵抗(Ro)は式1の59Ωであるのが分かります.

・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・(1)図1にはOPアンプ内部の出力抵抗として,式1の値を記載しています.

●フィードバック内補償の検討

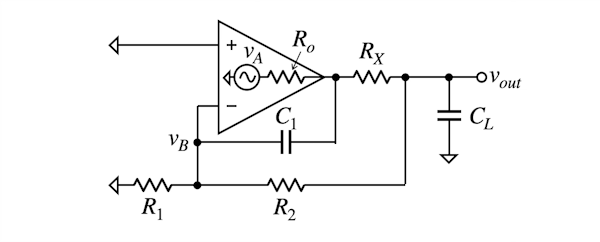

ここではフィードバック内補償の検討をするため,図1を書き直した図10を使います.vAの信号は負帰還回路を通りvBでOPアンプに負帰還されます.

図10の負帰還部分を抜き出したのが図11(a)になります.フィードバック内補償は,図11(a)の負帰還回路を場合分けし,図11(b)の「高周波でC1がショートとみなし,RX<<R2,Ro<<R1の条件」のときのvAからvBまでの伝達特性の極をfP1,ゼロをfZ1とします. 次に図11(c)の「負荷容量(CL)がオープンのとき」のvAからvBまでの伝達特性の極をfP2,ゼロをfZ2とします.極はゲインが低下し位相が遅れ始めるところ,ゼロはゲインが増加し位相が進み始めるところです.2つの極とゼロの周波数を「fP1=fZ2,fP2=fZ1」にすることでゲインと位相の変化をキャンセルする補償方法になります.

(a)図10の負帰還を抜き出した回路

(b)図11(a)のC1をショート,RX<<R2,Ro<<R1とした回路

(c)図11(a)のCLをオープンとした回路

●フィードバック内補償の机上計算

図11(b)と図11(c)を使って,フィードバック内補償するときのRXとC1の値を机上計算で求めます.vAからvBまでの伝達関数を検討すると,図11(b)の極は式2になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

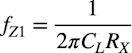

そして図11(b)のゼロは式3になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

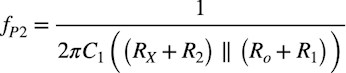

同様に図11(c)の極は式4になります.

・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・(4)

そして図11(c)のゼロは式5になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

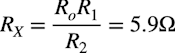

式2と式5を使って「fP1=fZ2」,そして式3と式4を使って「fP2=fZ1」とします.この2つの関係と「RX<<R2,Ro<<R1」の条件を使い,近似より,RXは式6になります.具体的な抵抗値は「Ro=59Ω,R1=1kΩ,R2=10kΩ」より,式6は「RX=5.9Ω」となります.この結果に近く,E24系列で選びやすい抵抗として,ここでは「RX=6.2Ω」としました.この値が図1のRXになっています.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

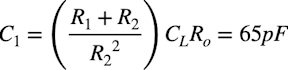

同様に「fP1=fZ2,fP2=fZ1」とすると,C1は式7になります.C1の選びやすい値として,ここでは「C1=68pF」としました.これより解答の(d)になるのが分かります.

・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・(7)

これらの選びやすい抵抗の「RX=6.2Ω」と「C1=68pF」を使い,fP1,fZ1,fP2,fZ2を計算すると,「fP1=243kHz」,「fZ1=2.6MHz」,「fP2=2.5MHz」,「fZ1=234kHz」となり,およそ「fP1=fZ2,fP2=fZ1」になるのが分かります.

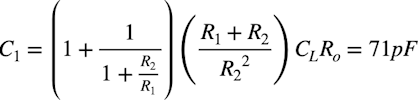

参考文献(2)では,C1を求める式7に「1+R2/R1」の項を含んだ式8になっています.これは実験などの検証により加えられた項になります.式8を使うと,C1は71pFになります.

・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・(8)

●補償後の負帰還ループのゲインと位相変化の確認

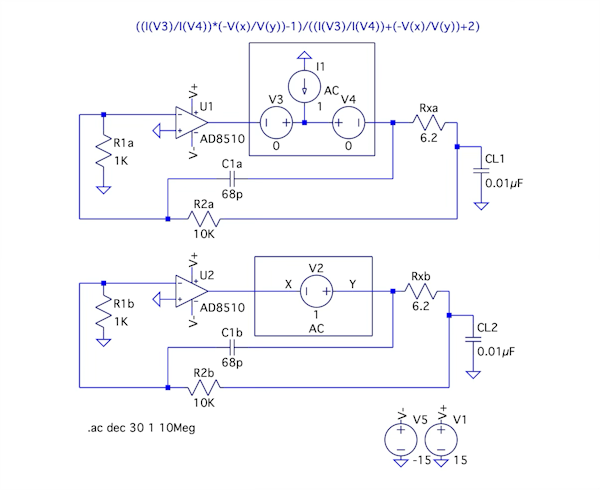

図12は,図1のC1を68pFとした補償後の負帰還ループのゲインと位相の変化を確認する回路になります.シミュレーションの設定は図4と同じです.

図1のC1に相当するC1aとC1bは68pFにしている.

図13は図12のシミュレーション結果になります.補償後の位相余裕は80°になり負帰還は安定しています.補償前の図5のプロットと比べると,10kHz以上で見られたゲインの低下と位相の遅れはキャンセルされているのが分かります.

位相余裕は安定して80°になる.

●補償後の時間応答の確認

図14は,補償後の回路で図1のC1を68pFとした回路になります.図14を使って時間応答の確認をします.シミュレーションの設定は図2と同じになります.

C1は68pFにしている.

図15は,図14のシミュレーション結果になります.図3の補償前のプロットと比べると,矩形波の立ち上がりと立ち下がりのリンギングはなくなり,回路が安定していることが分かります.

補償後はリンギングがない.

以上,大きな負荷容量を駆動するときの補償について解説しました.この補償方法は電圧帰還型OPアンプ全般で使えるものになります.シミュレーションで動作を確認した後は,実機での確認も忘れずに行ってください.

◆参考・引用*文献

(1) AD8510のデータシート:アナログデバイセズ

(2) アプリケーション・エンジニアに尋ねる ― 32容量性負荷によって損なわれるオペアンプ回路の安定性,この問題にはどう対処すればよいのか?:アナログデバイセズ

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice11_026.zip

●データ・ファイル内容

INV_Amp tran.asc:図2の回路

INV_Amp tran.plt:図2のプロットを指定するファイル

LoopGain.asc:図4の回路

LoopGain.plt:図4のプロットを指定するファイル

OpenLoopGain.asc:図6の回路

OpenLoopGain.plt:図6のプロットを指定するファイル

Output Resistance.asc:図8の回路

Output Resistance.plt:図8のプロットを指定するファイル

LoopGain Compensation.asc:図12の回路

LoopGain Compensation.plt:図12のプロットを指定するファイル

INV_Amp_Compensation tran.asc:図14の回路

INV_Amp_Compensation tran.plt:図14のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs