複合アンプを使った低雑音の負帰還アンプ

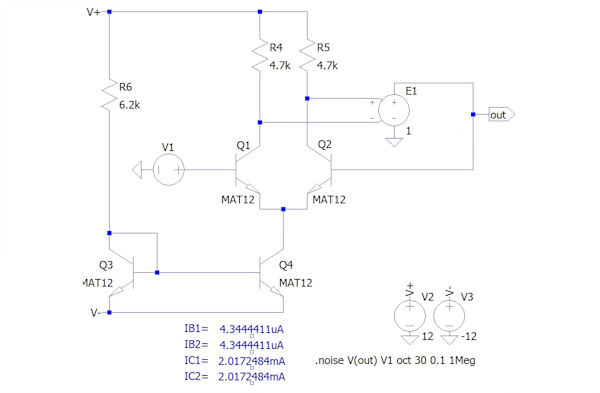

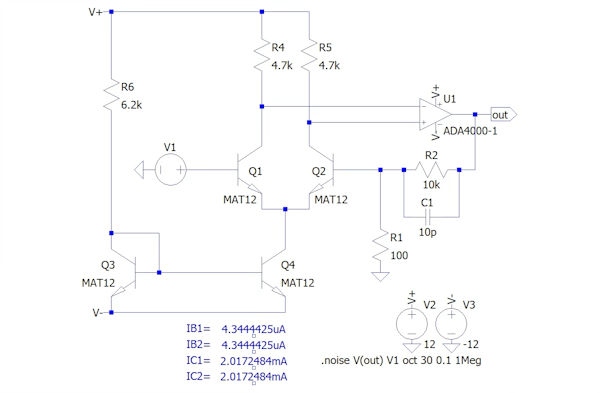

図1は,OPアンプと前段のプリアンプで構成された複合アンプを使用した,低雑音の負帰還アンプです.図1において,回路全体の入力雑音(vinoise)は(a)~(d)のどれでしょうか.ただし,プリアンプの入力雑音は「vn1=0.8nV/√Hz」,OPアンプの入力雑音は「vn2=16nV/√Hz」です.また,プリアンプのNPNトランジスタQ1とQ2のベース電流が4.3μAで,コレクタ電流が2mAです.

(a) 1.0nV/√Hz (b) 1.5nV/√Hz (c) 2.0nV/√Hz (d) 2.5nV/√Hz

回路全体の入力雑音は,複合アンプの入力雑音,R1とR2の等価抵抗で発生する熱雑音,さらにQ2のベース電流による雑音電流にR1とR2の等価抵抗を掛けた雑音で決まります.複合アンプの入力雑音は,プリアンプの雑音(vn1)と,OPアンプの雑音(vn2)に関係します.

- プリアンプのゲイン(G1)は,Q1とQ2のトランスコンダクタンス注1(gm1,gm2)と,R4,R5から求められ「G1=362倍」になる

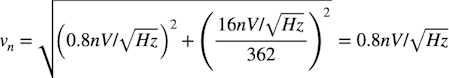

- 複合アンプの入力雑音(vn)は,プリアンプの入力雑音(vn1)と,OPアンプの入力雑音(vn2)をプリアンプのゲイン(G1)で割った「vn2/G1」雑音を,二乗和の平方根で求められ,「vn=0.8nV/√Hz」になる

- R1とR2の並列抵抗が等価抵抗(Req)となり,「Req=99Ω」なので,等価抵抗の熱雑音(vnReq)は「vnReq =1.3nV/√Hz」になる

- Q2のベース電流による雑音電流(in)は,「iB=iB1=iB2=4.3μA」より「in=1.2pA/√Hz」になる

- Q2の雑音電流にR1とR2の等価抵抗を掛けた雑音(inReq)は,「Req=99Ω」なので,「inReq=119pV/√Hz」になる

- 回路全体の入力雑音(vinoise)は,上記の複合アンプの入力雑音(vn)と,等価抵抗の熱雑音(vnReq)と,Q2の雑音電流と等価抵抗による雑音(inReq)を二乗和の平方根で求められ,「vinoise=1.5nV/√Hz」になる

以上の検討より,(b) 1.5nV/√Hzが正解になります.

●複合アンプを低雑音にする

負帰還アンプを低雑音にするには,アンプの雑音を低くし,等価抵抗で発生する熱雑音を低くすることが必要です.アンプの雑音を低くする回路として複合アンプがあります.複合アンプは,2つのアンプを使った回路で,図1はプリアンプとOPアンプになります.

複合アンプの雑音は,プリアンプの入力雑音が支配的になるのが特徴になります.この特徴より,プリアンプを低雑音にすると複合アンプの雑音は低くなります.

具体的には,図1のMAT12(1)を使ったプリアンプの入力雑音をシミュレーションで調べると1kHzのとき「vn1=0.8nV/√Hz」,2段目のアンプはADA4000(2)のOPアンプで入力雑音はデータシートより,1kHzのとき「vn2=16nV/√Hz」です.この場合,プリアンプの「vn1=0.8nV/√Hz」が支配的になり,低雑音になります.

負帰還アンプの雑音は,回路で使う抵抗値を低くすることも必要になります.図1の負帰還アンプは,後述する等価抵抗が99Ωと低い値で,等価抵抗の雑音は「vnReq=1.3nV/√Hz」の低雑音になります.

これ以降では,まず,プリアンプの入力雑音をシミュレーションで調べます.その後,図1に示した回路全体の入力雑音(vinoise)について,机上計算とシミュレーションで答え合わせをします.

●プリアンプの雑音

図2は,MAT12のNPNトランジスタを使ったプリアンプと,理想素子の電圧制御電圧源(E1)でユニティ・ゲイン・バッファを作り,プリアンプの雑音を調べる回路になります.電圧制御電圧源は無雑音なので,図2の回路でプリアンプの雑音を調べることができます.ここでは図1のプリアンプの雑音は「vn1=0.8nV/√Hz」になるのを確かめます.

シミュレーションで雑音を調べるときは「.noise」解析を使います.図2は「.noise V(out) V1 oct 30 0.1 1Meg」のドット・コマンドより,0.1Hz~1MHz間を周波数が2倍あたり30ポイントで,雑音の周波数特性をシミュレーションします.図2にはQ1とQ2のベース電流iB1とiB2,コレクタ電流IC1とIC2の直流動作点を回路図上に表示しています.これらの値は後述の机上計算で使います.

図3は,図2のシミュレーション結果になります.図3より,プリアンプの雑音は,周波数が1kHzのとき0.8nV/√Hzになります.図1には回路全体の入力雑音を検討する条件として,プリアンプの雑音を「vn1=0.8nV/√Hz」として示しています.

プリアンプの入力雑音は1kHzで0.8nV/√Hzになる.

●複合アンプの入力雑音を机上計算する

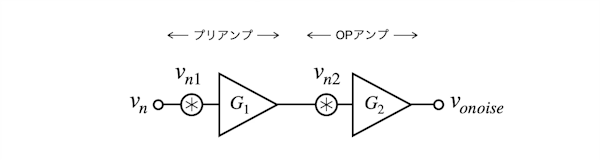

図4は,プリアンプとOPアンプで構成した複合アンプをブロック図で示しました.図4を用いて,複合アンプの雑音はプリアンプの雑音が支配的になるのを机上計算で確かめます.

後段のアンプの雑音vn2は前段のゲインG1で割った値になる.

図4の出力雑音(vonoise)は,「vn1をG1とG2で増幅した雑音」と,「vn2をG2で増幅した雑音」を加えたものになり,具体的には式1になります.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)図4の出力雑音(vonoise)から入力雑音(vn)を求めます.入力雑音(vn)は,式1の出力雑音(vonoise)を全体のゲインG1,G2で割ったものなので,式2になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)式2より,OPアンプの雑音(vn2)は,プリアンプのゲインで割った値にみえるので低くなります.この効果により,複合アンプの入力雑音はプリアンプの入力雑音(vn1)が支配的になります.

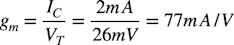

次に,式2の具体的な雑音電圧を検討します.検討するにあたり,プリアンプのゲイン(G1)を求めます.プリアンプのMAT12を使ったQ1とQ2の差動対のトランスコンダクタンス(gm)は式3になります.

・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・(3)ここで,Q1とQ2のコレクタ電流は,図1に示した「IC=IC1=IC2=2mA」,VTは熱電圧で「VT=26mV」とすると,「gm=77mA/V」になります.

プリアンプのゲイン(G1)は,式3のトランスコンダクタンス(gm)と,Q1とQ2のコレクタに繋がる負荷抵抗「RC=R4=R5=4.7kΩ」を乗じた値なので,式4の362倍になります.

・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・(4)式2へ式4のプリアンプのゲイン「G1=362」と,プリアンプの入力雑音「vn1=0.8nV/√Hz」と,OPアンプの入力雑音「vn2=16nV/√Hz」を入れて計算すると式5になります.

・・・・・・・・・・・(5)

・・・・・・・・・・・(5)式5より,複合アンプの入力雑音は,プリアンプの入力雑音と同じになり,プリアンプの雑音が支配的になるのが分かります.

●複合アンプを使った負帰還アンプの入力雑音を机上計算する

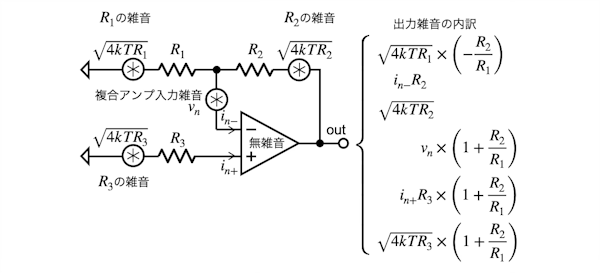

図5は,負帰還アンプの一般的な雑音モデルになります.図5のアンプの三角形の記号のところに複合アンプがあると考えて検討します.図1と図5を比べると,R1とR2の抵抗の位置は同じです.図1にはR3はないので,具体的な机上計算では「R3=0Ω」とします.図5の机上計算で図1の回路全体の入力雑音(vinoise)の答え合わせをします.

図5の負帰還アンプは,複合アンプの入力雑音電圧のvn,雑音電流のin+とin-,R1,R2,R3の熱雑音電圧の6つの雑音から求められます.この詳細は参考文献(3)に記載されています.図5には出力雑音の内訳として,6つの雑音を示しました.図5のノイズ・ゲインは式6になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

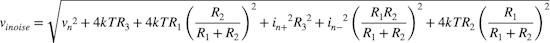

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)負帰還アンプの入力雑音は,図5の出力雑音の内訳に示した6つの雑音を,式6のノイズ・ゲインで割って入力換算し,各雑音を二乗和の平方根で求められます.具体的には,図5の入力雑音は式7になります.

・・・・・(7)

・・・・・(7)ここで,式7中のR1,R2,R3の抵抗で発生する3つの雑音を,1つの等価抵抗の雑音「vnReq」として表すと式8になります.

・・・・・・・・・・(8)

・・・・・・・・・・(8)式8を整理すると式9になります.

・・・・・・・・・・・・・・・・・・・・・・・・・(9)

・・・・・・・・・・・・・・・・・・・・・・・・・(9)式9のR1,R2,R3 からなる等価抵抗は式10になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(10)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(10)同じように,式7中のin+とin-の雑音電流が等価抵抗に流れて発生する雑音を,1つの雑音「inReq」で表すと式11になります.

・・・・・・・・・・・・・・・・・・・・(11)

・・・・・・・・・・・・・・・・・・・・(11)式7を式9のvnReqと式11のinReqを使って表すと,式12になります.

・・・・・・・・・・・・・・・・・・・・・・(12)

・・・・・・・・・・・・・・・・・・・・・・(12)式12を使って複合アンプを使った負帰還アンプの入力雑音を求めます.式10の等価抵抗(Req)は,「R1=100Ω,R2=10kΩ,R3=0Ω」より,「Req=99Ω」になります.これより,Reqの熱雑音は式13になります.

・・・・・・・・・・・・・・・・(13)

・・・・・・・・・・・・・・・・(13)雑音電流(in)はQ1とQ2のベース電流が「iB=iB1=iB2=4.3μA」のとき,式14になります.

・・・・・・・・・・・・・・・・・・(14)

・・・・・・・・・・・・・・・・・・(14)式14のinと等価抵抗(Req)より,2つを乗じたinReqの雑音は式15になります.

・・・・・・・・・・・・・・・・・・・(15)

・・・・・・・・・・・・・・・・・・・(15)式12へ式5のvnと,式13のvnReqと,式15のinReqを入れると式16になります.

・・・・(16)

・・・・(16)式16より複合アンプを使った負帰還アンプの入力雑音は解答の(b) 1.5nV/√Hzになります.

●複合アンプを使った負帰還アンプの雑音を確認

図6は,図1の入力雑音をシミュレーションする回路になります.シミュレーションの設定は図2と同じになります.

図7は,図6のシミュレーション結果になります.1kHzの入力雑音は1.5nV/√Hzになり,式16で机上計算した結果と同じになります.

入力雑音は1kHzで1.5nV/√Hz.

以上,複合アンプの入力雑音は,プリアンプのゲインが高いとOPアンプの入力雑音が見えなくなります.この効果により,プリアンプの入力雑音を低くすれば低雑音の複合アンプになります.低雑音の複合アンプで負帰還回路を作ったときの入力雑音は等価抵抗の熱雑音が見えてきます.回路全体を低雑音にするには等価抵抗を低くすることが必要になります.

◆参考・引用*文献

(1)MAT12のデータシート:アナログデバイセズ

(2)ADA4000のデータシート:アナログデバイセズ

(3)OPアンプ大全 第4章 4-7 OPアンプのノイズ(P201):CQ出版社

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice11_024.zip

●データ・ファイル内容

Pre Amp Noise.asc:図2の回路

Pre Amp Noise.plt:図2のプロットを指定するファイル

Low Noise Amplifier MAT12 noise.asc:図6の回路

Low Noise Amplifier MAT12 noise.plt:図6のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs