OPアンプに出力ドライバを備えた高電圧アンプの動作

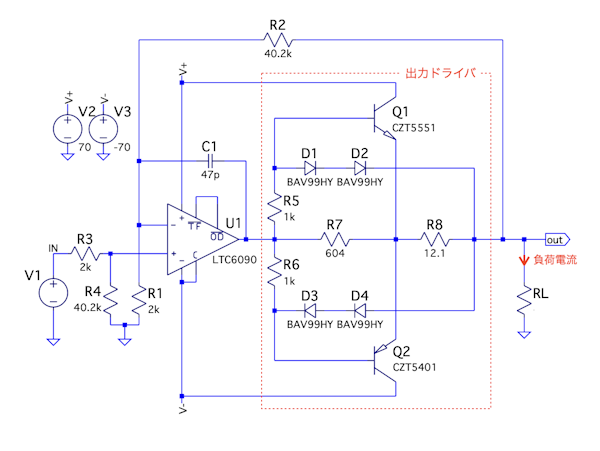

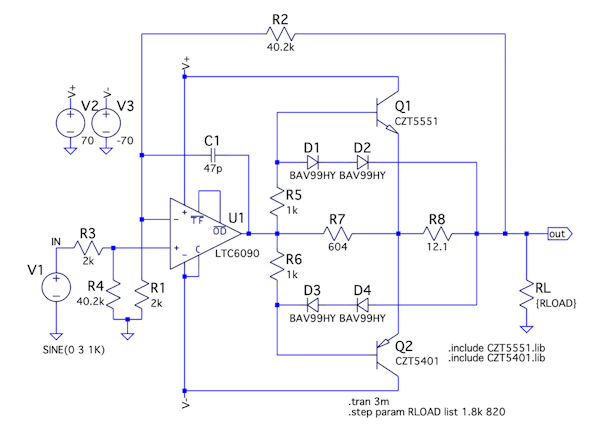

図1は,高出力電流を得るため,電源電圧範囲が140Vで,出力レール・ツー・レールのCMOS OPアンプ(LTC6090)に,出力ドライバを備えた高電圧アンプです.±70Vの電源電圧のときに,高出力電流を得ますが,高電圧アンプ内で出力電流が40mA以上の場合,保護が働くように設計されています.図1の高電圧アンプの正しい動作説明は(a)~(d)どれでしょうか.

出力ドライバを備えた高電圧アンプの働きとして正しいのは?

(a) 回路のゲインはR1,R2,R3,R4で決まりG=1になる

(b) V1が0VのときQ1とQ2のコレクタ‐エミッタ間にはバイアス電流が流れている

(c) V1の信号が0Vからわずかに変化したとき,同時にQ1とQ2も動いて負荷(RL)に電流を流す

(d) R8でQ1とQ2の電流を検出して保護している

次を検討すると分かります.

- 負帰還アンプのゲインはどこで決まるのか?

- V1が無信号のときQ1とQ2の動作がどうなっているのか?

- V1の信号が0Vからわずかに変化したとき,Q1とQ2がどう動くか?

- Q1とQ2の出力トランジスタが高い電流のとき,保護はどのように働くのか?

図1の出力ドライバを備えた高電圧アンプの(a)~(d)の動作は以下になります.

ここで,Q1とQ2のベース‐エミッタ間電圧はVBE1とVBE2,D1,D2,D3,D4の各ダイオードは同じなので順方向電圧はVD,R8の電圧降下をVR8とします.

- 回路のゲインはR1,R2,R3,R4で決まり「G=20.1倍」になる.

- V1が0Vのときoutの電圧は0V,OPアンプの出力は0Vになり,Q1とQ2のベース‐エミッタ間電圧は「VBE1=VBE2=0V」なのでバイアス電流は流れない.

- V1の信号が0Vからわずかに変化したとき,Q1とQ2が動作しないV1の入力電圧範囲がある.

- R8の電圧降下(Q1またはQ2の電流×R8)が「VBE1+VR8=2VD」,または「VBE2+VR8=2VD」の関係になるとQ1とQ2の電流を制限して保護を始める.

この動作よりR8でQ1とQ2の電流を検出して保護しています.これより,(d)が正解になります.

●高出力電流にするには出力ドライバを使う

高電圧の負帰還アンプを作るとき,OPアンプもLTC6090のような高電圧のOPアンプを用います.この場合,出力電流も高電流にしようとすると,OPアンプには出力電流の制限があるので,図1のような出力ドライバを加えた回路にします.出力ドライバに使うQ1とQ2のトランジスタは高耐圧で高いコレクタ電流が可能なトランジスタを選びます.しかし高いコレクタ電流のとき,Q1とQ2のトランジスタが発熱して破壊することもあるので,Q1とQ2の電流を制限して保護する回路が必要になります.今回は図1の出力ドライバを備えた高電圧アンプの動作と,Q1とQ2の電流を制限して40mAの保護する動作について解説します.

●OPアンプの特性を確認する

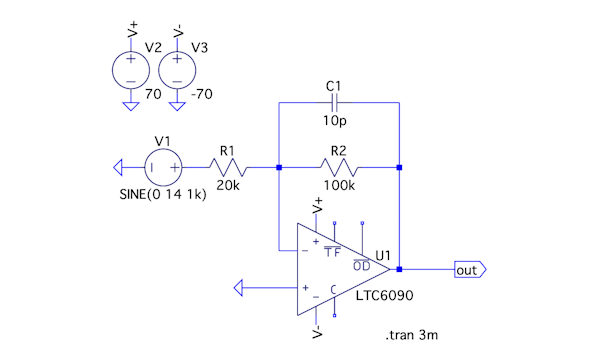

図2は,電源電圧範囲が140Vで,出力レール・ツー・レールのCMOS OPアンプの動作を確認する反転アンプになります.電源は「V2=70V,V3=-70V」でOPアンプの電源端子になるV+とV-に印加し,V+とV-間は140Vになります.反転アンプのゲインはR1とR2で決まり「G=-R2/R1=-5倍」になります.ゲインのマイナス(-)の記号は,位相が反転することを意味します.C1は負帰還を安定にする補償コンデンサです.入力電圧は,V1の振幅が14Vで周波数が1kHzの正弦波です.この回路をシミュレーションし,outの波形で出力電圧を確認します.

振幅14Vの入力信号(V1)を-5倍のゲインで増幅した出力波形を確認する.

図3は,図2のoutの波形をプロットした,シミュレーション結果です.outの波形は,V1から位相が反転し,振幅が70Vの正弦波になります.このようにLTC6090は出力レール・ツー・レールOPアンプなので,V+とV-の電源(正と負の電源のレール)付近までスイングできることが分かります.汎用OPアンプの電源は±15V,±18Vが多いですが,LTC6090はこれよりも高い電源±70Vで出力がレール・ツー・レールになるOPアンプということになります.

outは振幅が70Vの正弦波になる.

●出力ドライバで使うディスクリート部品

図1の40mAで保護が働く,出力ドライバを備えた高電圧アンプは,LTC6090のデータシート(P18)のアプリケーション回路に掲載されている高電圧アンプになります.

図1のQ1のNPNトランジスタは,Central Semiconductorの「CZT5551」で,コレクタ‐エミッタ間の最大電圧が160V,コレクタ電流の最大が600mA,消費電力の最大が2Wの性能になります.

図1のQ2のPNPトランジスタは,Central Semiconductorの「CZT5401」で,コレクタ‐エミッタ間の最大電圧は150V,コレクタ電流の最大は600mA,消費電力の最大は2Wの性能になります.

CZT5551とCZT5401のモデルは,LTspiceのライブラリに無いので,シミュレーションする場合,次に示したCentral Semiconductorからモデル・ファイルをダウンロードし,本記事の「■データ・ファイル」からダウンロードできる「LTspice10_038」のフォルダに一緒に保存してシミュレーションして下さい.

▼CZT5551 https://my.centralsemi.com/product/partpage2.php?part=CZT5551

「Additional Documentation Links:」にある「Spice Model:Spice Model CZT5551」をクリックすると「CZT5551.LIB」のモデル・ファイルをローカルPCへダウンロードできます.

▼CZT5401 https://my.centralsemi.com/product/partpage2.php?part=CZT5401

「Additional Documentation Links:」にある「Spice Model:Spice Model CZT5401」をクリックすると「CZT5401.LIB」のモデル・ファイルをローカルPCへダウンロードできます.

また,図1のBAV99HY(2)は,ロームのスイッチング・ダイオードでLTspiceのライブラリにあるモデルを使用します.

●出力ドライバを備えた高電圧アンプの動作

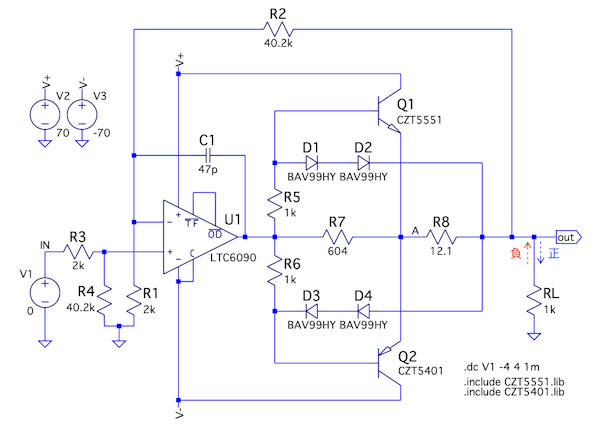

図4は,図1をDC解析で入力信号のV1をスイープして各部の応答をシミュレーションする回路です.電源電圧が±70V,V1が入力信号,outが高電圧アンプの出力,RLが負荷抵抗,ドット・コマンドの「.include」でCZT5551とCZT5401のモデル・ファイルを読み込んでいます.

まず,図4の出力ドライバを備えた高電圧アンプの動作を解説します.その後,解説した動作をシミュレーションします.

「.includeコマンド」で,CZT5551とCZT5401のモデル・ファイルを読み込んでいる.

▼回路全体のゲイン

回路全体のゲインについて解説します.図4の出力ドライバを備えた高電圧アンプは,負帰還を使った非反転アンプになります.図4は入力信号のV1をR3とR4で分圧後,R1とR2でゲインが決まる非反転アンプで増幅します.これより図4のゲインは式1になり,回路の抵抗値を使うと「G=20.1倍」になります.

・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・(1)▼V1が0Vのときの出力ドライバの動作

無信号時を表す入力信号のV1が0Vのとき,負帰還の効果でoutの電圧は0V,OPアンプの出力電圧も0Vになります.このときQ1とQ2のベース‐エミッタ間電圧は0Vになり,出力ドライバのQ1とQ2から電流は流れません.

▼V1の信号が0Vからわずかに変化したときのQ1とQ2の動作

V1の信号が0Vからわずかに変化したとき,Q1のベース‐エミッタ間電圧が0.6Vより高くなるV1にならないと,Q1は動作しません.同様にQ2のベース‐エミッタ間電圧が-0.6Vより低くなるV1にならないと,Q2は動作しません.このようにQ1とQ2が動作しない入力電圧範囲があります.この入力電圧範囲のときは,OPアンプから負荷抵抗に電流を供給し,図4は式1のゲインで動作します.

▼V1に大信号が印加されたときの出力ドライバの動作

V1が正(+)の大信号のとき,負荷抵抗へ流れるQ1の電流も高くなります.このとき電流を検出するR8の電圧降下も高くなります.Q1のベースとout間にはD1とD2の直列回路があります.このダイオード2つがあることで,VR8の電圧降下が高くなって式2の関係になると,VBE1が抑えられてQ1の電流制限がかかります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)同様に,V1が負の大信号のとき負荷抵抗へ流れるQ2の電流も高くなります.このとき電流を検出するR8の電圧降下も高くなります.Q2のベースとout間にはD3とD4の直列回路があります.このダイオード2つがあることで,VR8の電圧降下が高くなって式3の関係になると,VBE2が抑えられてQ2の電流制限がかかります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

●出力ドライバを備えた高電圧アンプのシミュレーション

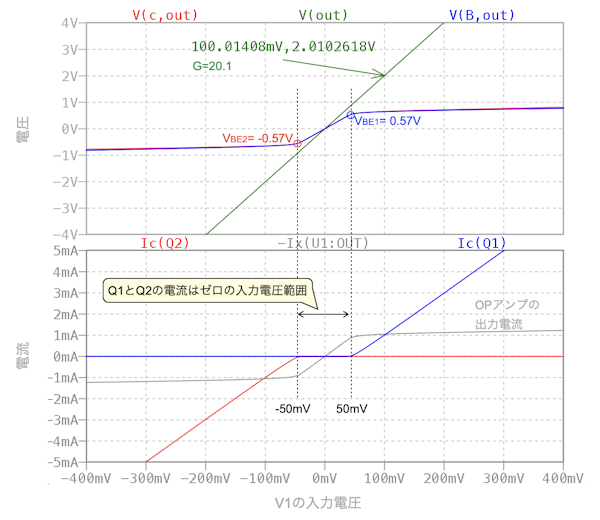

図5は,図4のシミュレーション結果です.V1の入力電圧が-400mVから400mVのときをプロットしています.図5の上段のV(out)のプロットより,入力電圧がおおよそ0.1VのときのV(out)の電圧をテキストで入れています.この値よりゲインは「G=2.01/100mV=20.1」であるのが分かります.

図5の下段より,入力電圧が0Vからわずかに変化したとき,Q1とQ2のコレクタ電流が流れない入力電圧範囲が±50mVあるのが分かります.その電圧を越すと,図5の上段のQ1のベース‐エミッタ間電圧に相当するV(b,out)の差電圧は0.57V以上,Q2のベース‐エミッタ間電圧に相当するV(c,out)の差電圧は-0.57V以下になり,Q1とQ2が動作して出力電流になります.Q1とQ2が動作しない領域は,OPアンプの出力電流が担います.

上段はAとout間の差電圧(R8の電圧降下に相当)のプロットと,outの電圧のプロット.

下段はQ1とQ2のコレクタ電流とOPアンプの出力電流をプロット.

図6は,図4の出力ドライバで,Q1とQ2のコレクタ電流を制限する様子をプロットしたものです.図5のシミュレーション結果からX軸を負荷抵抗の電流に変更したプロットになります.図6の上段のプロットは,負荷電流が変化したときのR8の電圧降下になります.この電圧降下がおおよそ±0.7Vに近づくとQ1とQ2のコレクタ電流は制限されて±43mAになります.この制限でQ1とQ2を保護しています.

上段は負荷電流が変化したときのR8の電圧降下をプロット.

下段はQ1とQ2のコレクタ電流とOPアンプの出力電流をプロット.

R8の電圧降下が±0.7VでQ1とQ2の電流は±43mAで制限して保護する.

●正弦波を入力したときの保護の動作を確認する

図7は,保護が働く様子をより具体的にするためにtran解析を使って,正弦波を入力し確認します.V1へ振幅3V,周波数1kHzの正弦波を入力したとき,outの波形をシミュレーションする回路になります.負荷抵抗は「.stepコマンド」で抵抗値を1.8kΩと820Ωの2種類を入れ替えます.1.8kΩはQ1とQ2の保護が働かない条件,820ΩはQ1とQ2の保護が働く条件になります.

RLの値は1.8kΩ,820Ωの2種類を「.stepコマンド」で変化させている.

図8は,図7のシミュレーション結果になります.図8の上段はoutのプロットです.1.8kΩのときは60Vの正弦波になります.820Ωのときは電流制限の影響から正弦波の山のピークが潰れています.図8の中段は,Q1のコレクタ電流のプロットです.図8の下段は,Q2のコレクタ電流のプロットになります.1.8kΩのときはQ1とQ2のコレクタ電流は,±43mA以内なので制限はかかりません.820Ωのときは±43mAを超えるので制限がかかる様子が確認できます.

RLが1.8kΩのとき保護がかからない.このときのoutの振幅は入力振幅3V×20倍=60Vになる.

RLが820Ωのとき±43mAで保護がかかる.

以上,今回使用したLTC6090のデータシートには,OPアンプを動作させることができる電圧,電流,温度を記した安全動作領域(SOA)が載っています.回路を設計するときは,その情報も参考にしながら進めてください.

◆参考・引用*文献

(1)アナログデバイセズ:LTC6090のデータシート(18ページの「40mAの保護出力ドライバを備えたゲイン20のアンプ」)

(2)ローム:BAV99HYのデータシート

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice10_038.zip

●データ・ファイル内容

LTC6090 Ex1.asc:図2の回路

LTC6090 Ex1.plt:図2のプロットを指定するファイル

LTC6090 G_20 Io.asc:図4の回路

LTC6090 G_20 Io.plt:図4のプロットを指定するファイル

LTC6090 G_20.asc:図6の回路

LTC6090 G_20.plt:図6のプロットを指定するファイル

CZT5551,CZT5401のモデル・ファイルはCentral Semiconductorのウェブ・ページからダウンロードしてください.

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs