信号の最大値を一定時間保持するピーク・ホールド回路の工夫

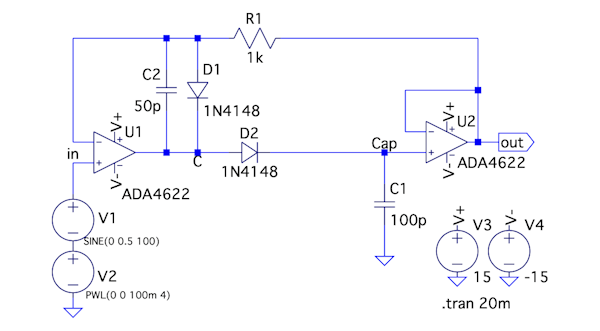

図1は,JFET入力を持つOPアンプ(ADA4622)を使用し,ピーク・メータなどに利用される,信号の最大値を一定時間保持するピーク・ホールド回路です.in端子の入力波形の最大値を保持してoutから出力します.

ピーク電圧のホールド時間を長くするには,C1の放電電流を低く抑えることが必要です.そこで図1では,ホールド区間でC1の充電電圧V(Cap)と,回路内の(a)~(d)のある箇所の電圧を同じにします.同じ電圧になる箇所は(a)~(d)のどれでしょうか.

ホールド区間でCapの電圧と同じになるのは(a)~(d)のどれ?

ただし,JFET入力OPアンプの入力バイアス電流は無視できるほど低いとします.

(a) Aの電圧 (b) Bの電圧 (c) Cの電圧 (d) inの電圧

ホールド区間では,ダイオードのD1がON,D2がOFF,D3がOFFになります.この状態で回路の電圧を検討すると分かります.図1はADA4622のデータシートにあるアプリケーション回路です.

図2は,上段から(a)の波形,(b)の波形,(c)の波形,(d)の波形をプロットし,比較のためCapの電圧[V(Cap)]も加えています.ホールド区間は最初にV(in)のピーク電圧を保持する区間を代表例にしています.

比較のためCapの波形も加えている.

(a)の電圧は,V(out)からR1を介した負帰還とダイオード(D1)を介した負帰還により,OPアンプ(U1)の非反転端子と反転端子はバーチャル・ショートになります.バーチャル・ショートなので,図2(a)の波形のように,(a)の電圧はinの電圧に応じて動きます.よって,ホールド区間でC1の電圧V(Cap)と等しくなりません.

(b)の電圧は,ホールド区間でD1がON,D2とD3がOFFなので,V(out)の電圧から「D1の順方向電圧+R1の電圧降下」を減じた電圧になります.OPアンプ(U2)はユニティ・ゲイン・バッファなので,V(out)の電圧はV(Cap)の電圧と同じです.よって図2(b)の波形のように,V(Cap)から「D1の順方向電圧+R1の電圧降下」を減じた電圧になり,ホールド区間でC1の電圧V(Cap)と等しくなりません.

(c)の電圧は,ホールド区間でD2とD3がOFFなので,R2を介してV(out)の電圧と等しくなります.OPアンプ(U2)は,ユニティ・ゲイン・バッファなので,Cの電圧はV(Cap)の電圧と等しくなります.これより,図2(c)の波形のように,D3の両端の電圧は同じ電圧になります.D3の両端の電圧差が無いので,ダイオードの逆方向の漏れ電流は無くなり,V(Cap)の電圧を長時間保持します.

(d)のinの電圧は,入力電圧のV(in)なので,図2(d)の波形のように,V(Cap)の電圧と等しくなりません.

このような検討と図2の波形プロットより,正解は(c)の電圧になります.

●回路で求められる部品性能と工夫

図1のピーク・ホールド回路は,V(in)>V(Cap)のとき,OPアンプ(U1)からダイオード(D2)とD3を介して,コンデンサ(C1)を充電しながらV(Cap)はV(in)に追随していきます.信号の変化に追随させるため,OPアンプは高いスルー・レートとC1を素早く充電する高い出力電流であることが求められます.

次にV(in)<V(Cap)のホールド区間のとき,V(in)の最大値を保持したV(Cap)の電圧を出力します. 長時間の保持をするには,C1の放電を抑えることが必要になります.このため,OPアンプの入力バイアス電流を低くすること,D3の逆方向の漏れ電流を低くすること,C1の絶縁抵抗を高くすることが求められます.

この検討より,図1のピーク・ホールド回路で使うOPアンプは,入力バイアス電流が低く,高いスルー・レートと高い出力電流を兼ね備えたJFET入力OPアンプ(ADA4622)を用いています.また,ダイオードのD3の逆方向の漏れ電流を低くするには,図1のようにD3の両端にかかる電圧を無くすように回路で工夫しています.

●回路に適したOPアンプ

図1で使用したOPアンプ(ADA4622)は,JFET入力OPアンプです.JFET(接合形電界効果トランジスタ)を入力段に使っているので,JFETのゲートに流れる電流はとても低く,OPアンプの入力バイアス電流が無視できるほど低くなります.ADA4622のデータシートより入力バイアス電流を調べると,標準で2pA,最大で±10pAの性能であるのが分かります.JFET入力OPアンプは,図1のピーク・ホールド回路のような用途に適しています.

●入力バイアス電流を確かめる

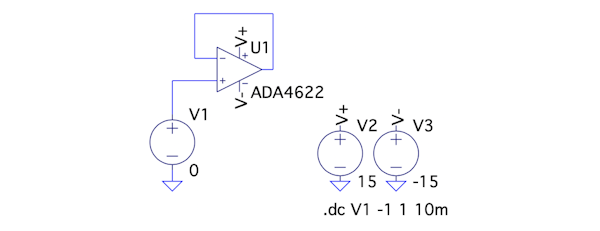

図3は,ADA4622の入力バイアス電流をシミュレーションで簡易的に調べる回路です.図3はユニティ・ゲイン・バッファにして,非反転端子にV1の電圧源を接続し,-1Vから1V間を10mVステップでスイープします.電源は±15Vです.このときOPアンプの非反転端子の入力バイアス電流をシミュレーションします.

図4は,図3のシミュレーション結果になります.図4より,V1が中点電圧の0Vのとき,入力バイアス電流は2pAであることが分かります.このようにJFET入力OPアンプの入力バイアス電流はとても低い電流になります.

V1が中点電圧の0Vのとき,入力バイアス電流は2pAであることが分かる.

●ダイオードの漏れ電流対策がない回路

図5は,図1のD3とR2を取り外したダイオードの漏れ電流対策がないピーク・ホールド回路になります.ホールド区間の動作の比較用として,この回路の性能を調べます.

図5のV(in)のテスト用の入力信号は,V1の振幅が0.5V,周波数が100Hzの正弦波が,V2の100ms後に4Vまで単調に増加する電圧により,V(in)のピークが変化した波形になります.

図6は,図5のシミュレーション結果になります. 図6のプロット内容は,上段が,V(in)の入力電圧とV(out)の出力電圧,中段がV(c)のD2ダイオードのアノード電圧とV(Cap)のC1の充電電圧,下段がD2ダイオードの電流となります.

ホールド区間でoutの波形は時間と共に電圧が低下し,長時間ピーク電圧を保持できない.

原因はダイオード(D2)に逆方向の電圧がかかり,約3nAの漏れ電流が発生するため.

図6の上段のピーク・ホールド回路のV(out)の出力電圧は,時間が0sからのV(in)の入力電圧を追随します.V(in)のピークが過ぎるとホールド区間になり,V(out)はC1で保持した電圧を出力しますが,時間が経過すると低下していきます.この原因はダイオードの漏れ電流対策がないためです.

具体的には,図6の中段のプロットのように,ホールド区間においてD2に逆方向の電圧が加わります.このとき図6の下段に示したD2ダイオードの漏れ電流は,約3nAになります.ホールド区間ではダイオードの漏れ電流がC1の放電電流になり,V(Cap)の電圧が低下してV(out)の電圧も同じように低下します.

●ダイオードの漏れ電流を低くした回路

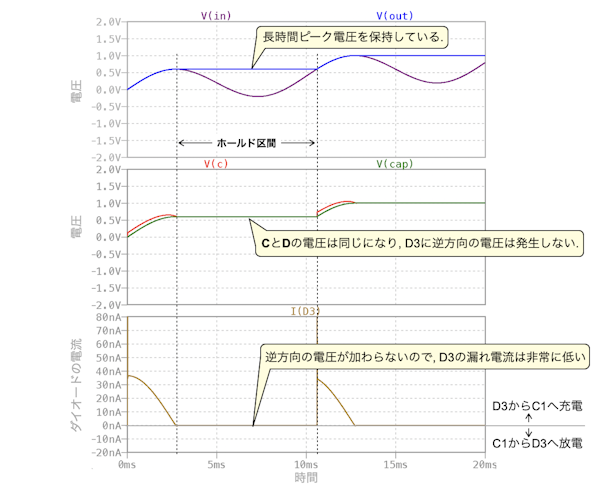

次に,ダイオード(D3)の漏れ電流対策をした図1のピーク・ホールド回路の性能をシミュレーションで調べます.図7は,図1のシミュレーション結果になります.図7のプロット内容は,上段,中段,下段とも図6と同になります.

ホールド区間でV(out)の波形は長時間ピーク電圧を保持している.

D3にかかる逆方向の電圧はほぼ0Vになり,漏れ電流は非常に低くなる.

図7の上段のピーク・ホールド回路のV(out)の出力電圧は,時間が0sからのV(in)の入力電圧を追随します.V(in)のピークが過ぎるとホールド区間になり,V(out)はC1で保持した電圧を出力します.ホールド区間の保持した電圧は,時間が経過しても低下しません.これは,中段のプロットのように,ホールド区間において,ダイオード(D3)に逆方向の電圧が加わらないことによります.また,D3に逆方向の電圧が加わらないので,下段のようにD3の漏れ電流が無くなり,ホールド区間にピーク電圧を保持する性能が向上します.

以上,JFET入力OPアンプを用いたピーク・ホールド回路について解説しました.ホールド区間にピーク電圧を保持する性能を良くするには,JFET入力OPアンプを使って入力バイアス電流を非常に低くし,ダイオードの漏れ電流が発生しないように回路で工夫することです.この他にも基板上の漏れ抵抗によるC1コンデンサの放電電流も加わるので注意が必要です.

◆参考・引用*文献

アナログ・デバイセズ:ADA4622のデータシート

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice10_018.zip

●データ・ファイル内容

Peak Detector ADA4622.asc:図1の回路

Peak Detector ADA4622.plt:図1のプロットを指定するファイル

JFET OPAMP Input Bias Current.asc:図3の回路

JFET OPAMP Input Bias Current.plt:図3の回路

Peak detector.asc:図5の回路

Peak detector.plt:図5のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs