雑音が低く見える低雑音バイアス回路

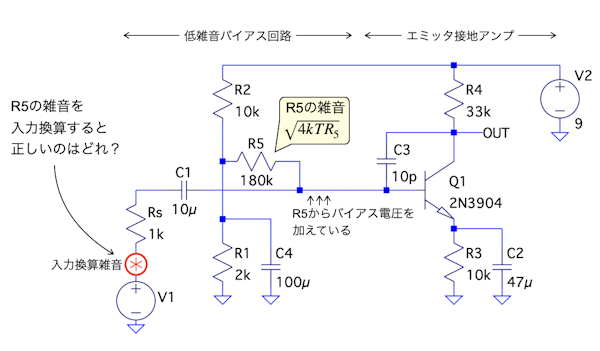

図1は,R5の雑音を入力換算し,V1の位置から見ると雑音が低く見える,低雑音バイアス回路を使った,エミッタ接地アンプです.V1が入力で,outが出力となります.図1の低雑音バイアス回路のR5の雑音を入力換算すると,正しい関係式は(a)~(d)のどれでしょうか.ただし,R5の雑音は(4kTR5)1/2になります.

低雑音バイアス回路のR5の雑音を入力換算すると,正しい関係式は(a)~(d)のどれでしょうか.

(a)  (b)

(b)  (c)

(c)  (d)

(d)

図1は,低雑音バイアス回路の出力となるR5から,エミッタ接地アンプの入力となるQ1のベースへ直流電圧を加えて回路を動かします.低雑音バイアス回路は,R1と並列にC4のコンデンサがあります.C4は100μFの容量なので,R5の左側は交流的に電圧が変化しない交流接地として考えます.そしてC1のコンデンサは,交流信号が導通している状態を考えてC1をショートします.この2つの状態でR5の雑音を入力換算した関係式を検討します.

R1と並列接続しているC4は,容量が100μFのバイパス・コンデンサなので,R1とR2の雑音はC4により減衰してR5側に伝わりません.このためR5の左側は交流接地とみなせます.そして,V1の交流信号は,C1を通過している状態を考えるので,C1は導通とみなしてショートします.この条件のとき,R5の右側のノードに発生する雑音は,RSとR5の並列抵抗の雑音になり,「(4kT(RS||R5))1/2」です.

この雑音を入力換算するときは,RSとR5の分圧回路のゲインで除算します.分圧回路のゲインは「G=R5/(RS+R5)」なので,計算すると「(4kTR5)1/2×(RS/R5)」になり,(c)が正解になります.

具体的には,「RS=1kΩ」,「R5=180kΩ」なので,R5の雑音を入力換算すると,(4kTR5)1/2の雑音を1/180倍した低い雑音に見えます.入力からみたR5の雑音が低く見えるので,エミッタ接地アンプの出力(out)にはR5の雑音がほとんど影響しません.

●直流と交流信号を,エミッタ接地アンプへ伝える

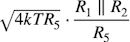

最初に低雑音バイアス回路の動作について解説します.図2は解説のため,図1から低雑音バイアス回路を抜き出したものになります.低雑音回路の主な働きは,図2のBIAS端子に繋がる後段のエミッタ接地アンプへ直流電圧を加えて回路が動くように直流動作点を決めます.

V1の交流信号は,信号源抵抗(RS)を通り,C1で交流信号のみを通過させてBIAS端子の直流に交流信号を重畳させます.この直流と交流信号を,エミッタ接地アンプの入力へ伝える動作が,低雑音バイアス回路の動作になります.

●回路定数の決め方

図2のBIAS端子の直流電圧は,電源電圧(V2)とR1,R2の分圧回路から作ります.具体的には「V2=9V」,「R1=2kΩ」,「R2=10kΩ」のとき,分圧した直流電圧は1.5Vになります.

分圧した直流電圧1.5VはC4のバイパス・コンデンサで安定化されます.C4の効果として,R1とR2で発生する雑音や,V2の電源ラインに飛び込む外来雑音を減衰させ,交流的に安定(交流接地)になり,R1とR2の雑音はR5側に伝わりません.

交流接地とみなせるおおよその目安は,R1の抵抗値とC4のリアクタンスを比べたとき,式1のようにR2の抵抗値より信号の最低周波数におけるC4のリアクタンスが十分小さくなるようにします.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

図1の回路定数のとき,信号の最低周波数を10Hzとすると,式1は「2kΩ>>159Ω」の関係になっています.

V2の電源電圧をR1とR2で分圧した1.5Vの直流電圧は,R5を介してBIAS端子へ伝わります.図1の回路は,図2のBIAS端子にエミッタ接地アンプの入力となるQ1のベースが繋がっています.図1の場合はベース電流が「IB=280nA」です.図2ではQ1のベース電流分をI1の電流源で表しています.

R1とR2の抵抗分圧による1.5Vと大きく変わらない直流電圧をBIAS端子の電圧にしたいので,R5の電圧降下は50mVにしています.これより,R5の抵抗値は「50mV/280nA=179kΩ」となり,選びやすい抵抗値として「R5=180kΩ」になります.

R2に流れる750μAの電流は,R5側にQ1のベース電流分の280nAが分流します.しかし,分流する電流値が750μAに対して280nAなのでとても低く,V2の電源電圧をR1とR2で分圧した1.5Vは僅かに変化するだけになります.

●R5の入力換算雑音を導く

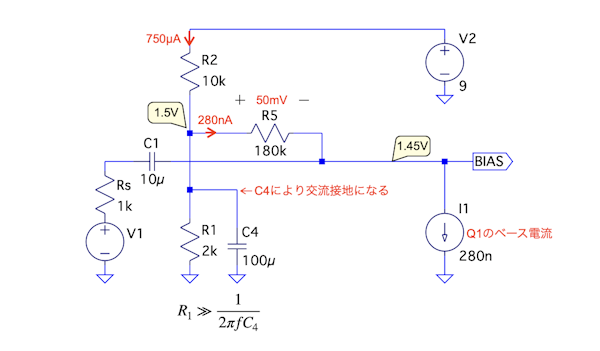

ここでは,図3を用いて低雑音バイアス回路の全体の入力換算雑音からR5の入力換算雑音を導いて答え合わせをします.

図3(a)は,入力換算前でRSとR5の雑音をvBで表しています.図3(b)は,図3(a)のvBを入力換算したもので,vinoiseの記号で表しています.

図1のC4側に繋がるR5の一端は交流接地なので,図3(a)と図3(b)のR5の一端はGNDとみなしています.図1のC1のコンデンサは交流信号が導通している状態を考えるので,C1をショートにし,図3(a)と図3(b)は,RSとR5の一端が繋がります.このように図3(a)と図3(b)のRSとR5は分圧回路になります.

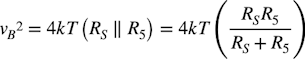

図3(a)のvB2の雑音は,RSとR5の並列接続の雑音になるので,式2になります.

・・・・・・・・・・・・・・・・・・・・(2)

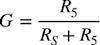

・・・・・・・・・・・・・・・・・・・・(2)図3(a)と図3(b)は,分圧回路なので,ゲインは式3になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)式2のvB2の雑音を式3のゲインの2乗(G2)で除算したものが入力換算雑音なので,式4になります.

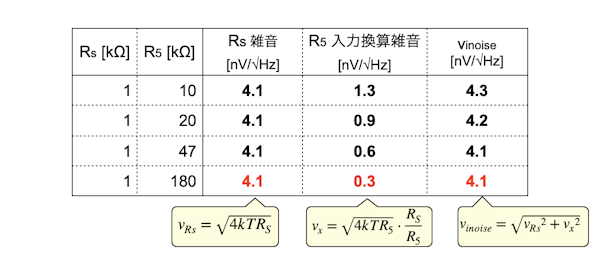

・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・(4)式4より,入力換算雑音はRSの雑音(右辺第一項)とR5の雑音を入力換算した雑音(右辺第二項)を加えた雑音になります.式4の右辺第二項のR5に関する雑音の項を抜き出し,vx2とすると式5になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)式5の平方根をとると式6になります.ここまでの検討で,図3のR5の雑音を入力換算すると,解答の(c)になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

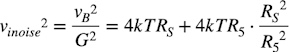

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)表1は,式4を用いて,式4のRSを「1kΩ」で固定し,R5を「10kΩ,20kΩ,47kΩ,180kΩ」と変化させたときの各雑音を調べました.

vinoiseはRSの雑音が支配的になり,R5の雑音は見えなくなる.

低雑音バイアス回路の全体の入力換算雑音(vinoise)は,式4中のRSの雑音とR5の入力換算雑音で決まります.R5が高くなるとR5の入力換算雑音は低くなり,全体の入力換算雑音(vinoise)は低くなります.表1の「RS=1kΩ」,「R5=180kΩ」のとき,RSの雑音とR5の入力換算雑音を比べると,vinoiseはRSの雑音が支配的になり,R5の雑音は見えなくなります.

●低雑音バイアス回路の入力換算雑音の確認

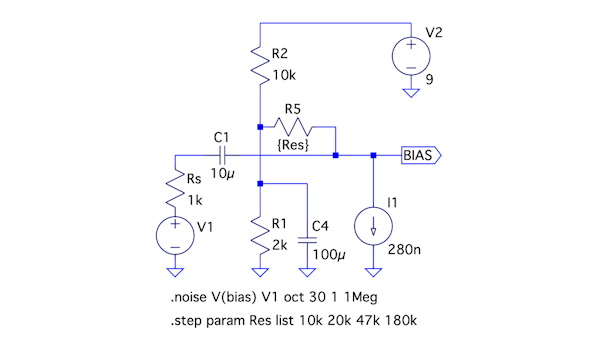

図4は,低雑音バイアス回路の入力換算雑音をシミュレーションする回路になります.Noise解析は「.noiseコマンド」で「.noise V(bias) V1 oct 30 1 1Meg」となり,周波数が2倍あたり30ポイントのスイープで雑音を調べます.R5の抵抗値は「.stepコマンド」で「.step param Res list 10k 20k 47k 180k」と表1と同じように10kΩ,20kΩ,47kΩ,180kΩの4種類を調べます.

R5は10kΩ,20kΩ,47kΩ,180kΩの4種類.

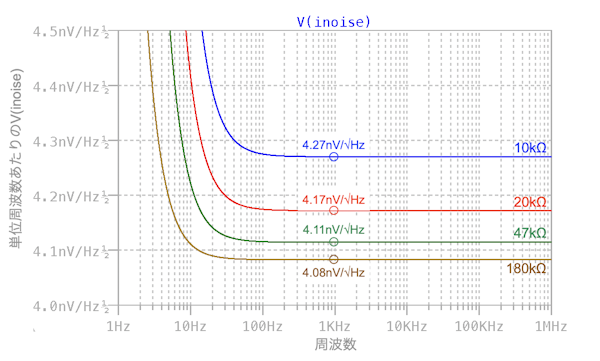

図5は,図4のシミュレーション結果になります.1kHzでの入力換算雑音は,表1のvinoiseと同じになります.

1kHzのvinoiseは表1と同じになる.

●低雑音バイアス回路を使ったエミッタ接地アンプの確認

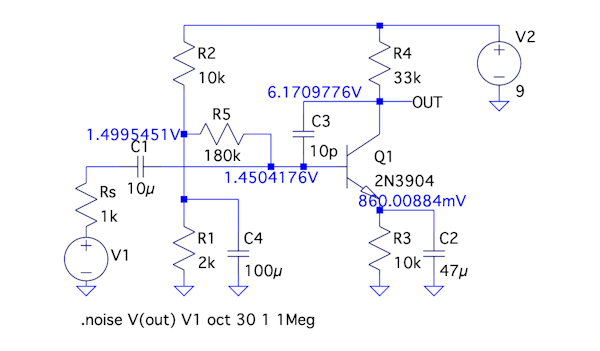

図6は,図1の低雑音バイアス回路を使ったエミッタ接地アンプをシミュレーションする回路になります.Noise解析のスイープの指定は図4と同じです.

図6には,直流動作点を表示しています.「V2=9V」,「R1=2kΩ」,「R2=10kΩ」のとき,分圧した直流電圧は1.5Vになります.そしてR5の右からエミッタ接地アンプのQ1のベースへ加える直流電圧は,1.5Vより50mV低い1.45Vになるのが確認できます.

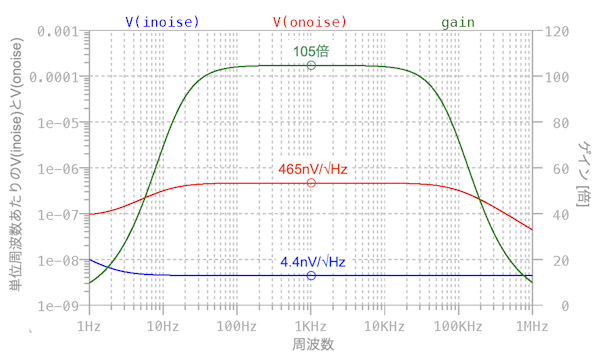

図7は,図6のシミュレーション結果で「.Noiseコマンド」は,図4と同じ設定になります.入力換算雑音(vinoise)はエミッタ接地アンプの入力雑音も加わるので,4.4nV/√Hzになります.outまでの雑音(vonoise)はvinoiseを105倍のゲインで増幅した雑音になります.

エミッタ接地アンプの雑音も加わるので,入力換算雑音は4.4nV/√Hzになる.

入力換算雑音を105倍で増幅するので,出力雑音は465nV/√Hzになる.

以上,低雑音バイアス回路の入力換算雑音について解説しました.回路全体の雑音はメインのアンプ回路の他に,バイアス回路の雑音も含みます.バイアス回路を低雑音にするとき,今回解説したような回路手法を用います.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice9_038.zip

●データ・ファイル内容

Bias.asc:図4の回路

Bias.plt:図4のプロットを指定するファイル

CE Noise.asc:図6の回路

CE Noise.plt:図6のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs