負帰還アンプの雑音が小さい抵抗値の決め方

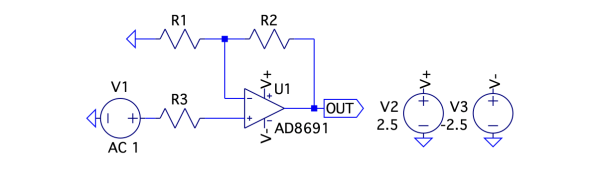

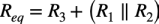

図1はCMOS OPアンプを使った負帰還アンプです.CMOS OPアンプの入力雑音は1kHzのとき9.5nV/√Hzの性能です.R1,R2,R3の抵抗の組み合わせが表1のとき,V1の位置に見える負帰還アンプの雑音(入力換算雑音)が最も小さいのは,(a)~(d)のどの抵抗の組み合わせでしょうか.

R1,R2,R3が表1のとき,図1の入力換算雑音が最小になるのはどれでしょうか.

(a)の抵抗の組み合わせ

(b)の抵抗の組み合わせ

(c)の抵抗の組み合わせ

(d)の抵抗の組み合わせ

図1の負帰還アンプの雑音は,R1,R2,R3の抵抗で発生する3つの雑音にOPアンプの入力雑音を加えた4つの雑音で決まります.これらの4つの雑音が増幅され,2乗平均平方根したものが出力雑音になります.その出力雑音を図1のノイズ・ゲインで除算したものがV1の位置に見える入力換算雑音になります.入力換算雑音にすると,回路に複数ある雑音を入力側で1つにまとめるので,雑音の検討が楽になります.

抵抗の単位周波数あたりの雑音は,抵抗値をRとすると「(4kTR)1/2 [V/√Hz]」で求めることができます.ここで,kはボルツマン定数で「1.38×10-23[J/K]」,Tは絶対温度で27℃のとき300[K]です.またOPアンプの入力雑音は9.5nV/√Hz の性能です.これらを使って雑音の検討をします.

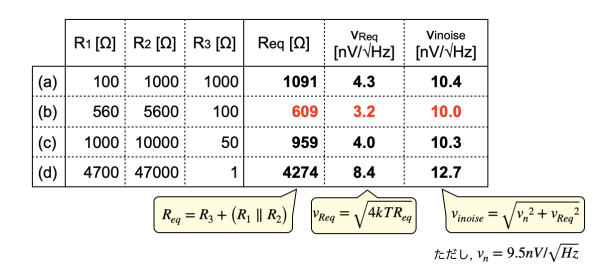

図1の負帰還アンプの入力換算雑音を「vinoise」,OPアンプの入力雑音を「vn」,R1,R2,R3から発生する3つの雑音の2乗平均平方根を「vReq」の記号とします.

これらの記号を使うと,図1の入力換算雑音は「vinoise2=vn2+vReq2」になります.「vn=9.5nV/√Hz」は一定なので,vinoiseを低雑音にするにはvReqが低いときになります.

vReqはR1,R2,R3からなる等価抵抗「Req」が低くなると低雑音になります.Reqは「Req=R3+(R1||R2)」で求めることができ,表1の(a)~(d)のときのReqは次になります.

(a)Req =1091Ω

(b)Req = 609Ω

(c)Req = 959Ω

(d)Req =4274Ω

(a)~(d)のReq が最も低くなる抵抗の組み合わせは(b)になり,このとき負帰還アンプ全体の入力換算雑音が最も低くなります.

●負帰還アンプの雑音はOPアンプの入力雑音と等価抵抗の雑音で決まる

CMOS OPアンプの2つの入力端子は,NチャネルMOS FETまたはPチャネルMOS FETのゲートになります.ゲート電流は流れないことから,CMOS OPアンプの入力バイアス電流はゼロとみなせ,雑音電流を無視できます.この特徴により,図1の負帰還アンプの雑音は,R1,R2,R3の抵抗で発生する雑音と,OPアンプの入力雑音の4つの雑音で決まります.

ここで,R1,R2,R3からなる等価抵抗をReqとし,Reqの雑音を「vReq」とすると,図1の負帰還アンプの入力換算雑音は「vinoise2=vn2+vReq2」になります.この式のようにCMOS OPアンプを使った負帰還アンプは,OPアンプの入力雑音「vn」と等価抵抗の雑音「vReq」で決まります.回路を低雑音にするには,vnとvReqの2つで調整します.

●OPアンプの入力雑音

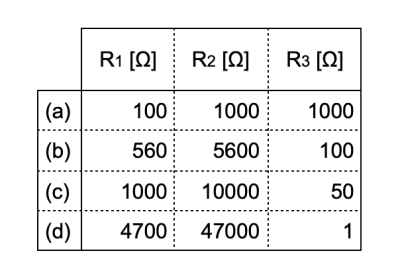

最初に図1で使用しているCMOS OPアンプの入力雑音「vn」を調べます.OPアンプの入力雑音を調べるには,データ・シートの値を使う方法と,シミュレーションで求める方法があります.今回は後者のシミュレーションで調べます.

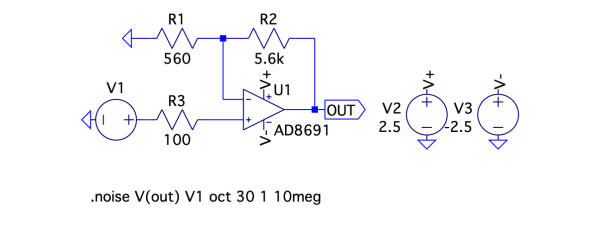

図2は,図1で使用しているCMOS OPアンプをユニティ・ゲイン・バッファにして入力雑音の周波数特性を調べます.LTspiceのドット・コマンドは「.noise V(out) V1 oct 30 1 10meg」の指定で,1Hz~10MHz間を周波数が2倍あたり30ポイントでスイープします.

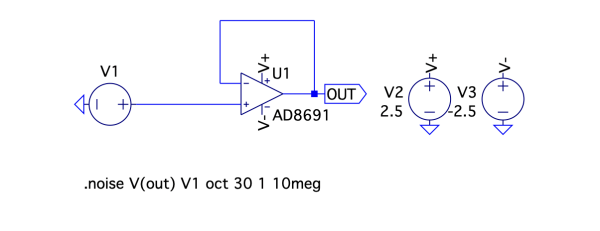

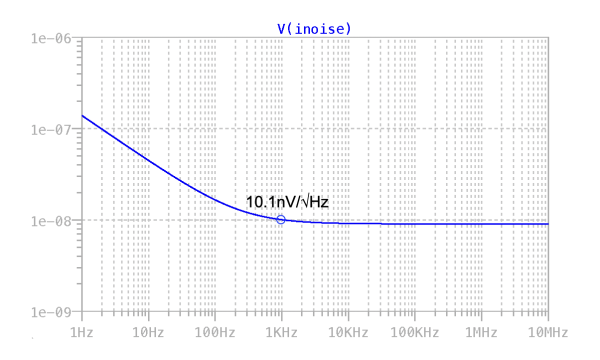

図3は図2の入力雑音「V(inoise)」のシミュレーション結果になります.1kHzでの入力雑音は9.5nV/√Hzになります.この入力雑音を問題で使用しています.

周波数が1kHzのとき,入力雑音は9.5nV/√Hzになる.

●負帰還アンプの入力換算雑音と4つの雑音の関係

図4は,R1,R2,R3の抵抗で発生する雑音と,OPアンプの入力雑音の4つの雑音を負帰還アンプへ加えました.この回路を用いて負帰還アンプの入力換算雑音と4つの雑音の関係を調べます.

出力雑音の内訳も記載.

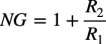

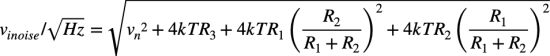

負帰還アンプは4つの雑音が増幅されてoutに出力雑音として現れます.図4の右側に出力雑音の内訳を示しました.負帰還アンプの入力換算雑音「vinoise」は,出力雑音の内訳に示した4つの雑音を,式1のノイズ・ゲイン(NG)で除算して入力換算し,各雑音を2乗平均平方根することにより求めることができます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)図4の入力換算雑音は式2になります.

・・・・・(2)

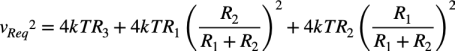

・・・・・(2)ここで,式2中のR1,R2,R3の抵抗で発生する3つの雑音を1つの等価抵抗の雑音「vReq」として表すと式3になります.

・・・・・・・・・・・(3)

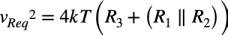

・・・・・・・・・・・(3)式3を整理すると式4になります.

・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・(4)ここで,式4中のR1,R2,R3からなる等価抵抗は式5になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)式2中のR1,R2,R3の抵抗で発生する3つの雑音を,式4の等価抵抗の雑音で表すと,式6の関係になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・(6)式6のように,CMOS OPアンプを使った負帰還アンプは,OPアンプの入力雑音「vn」と等価抵抗の雑音「vReq」で決まるのが分かります.

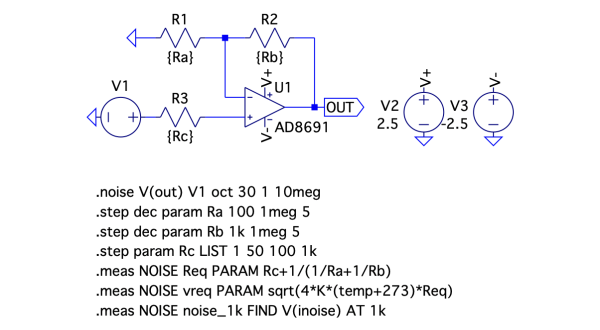

ここまでの計算式を使って答え合わせをします.表2は表1の(a)~(d)の抵抗の条件で式4,式5,式6を計算した結果になります.等価抵抗(Req)が低いとき,等価抵抗の雑音(vReq)も低くなり,負帰還アンプの入力換算雑音は(b)の抵抗が最も低くなるのが分かります.

●等価抵抗と負帰還アンプの入力換算雑音の関係

表2では,等価抵抗と入力換算雑音の結果が4ポイントだけなので,さらにデータ数を増やして視覚的に分かりやすいプロット図を作成します.

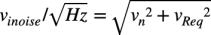

具体的には,X軸(横軸)を等価抵抗(Req),Y軸(縦軸)を入力換算雑音(vinoise)と等価抵抗の雑音(vReq)の2つをプロットし,等価抵抗と負帰還アンプの入力換算雑音の関係を調べます.図5が,等価抵抗と負帰還アンプの入力換算雑音の関係を調べる回路です.

図5は,図1の回路のR1の抵抗値をRaの変数,R2の抵抗値をRbの変数,R3の抵抗値をRcの変数にしました.Noise解析のドット・コマンドは図2と同じです.Raの抵抗値は「.step dec param Ra 100 1meg 5」を用い「.stepコマンド」で100Ω~1MΩ間を抵抗が10倍あたり5ポイントでスイープします.同じようにRbの抵抗値は「.step dec param Rb 1k 1meg 5」を用い1kΩ~1MΩ間を抵抗が10倍あたり5ポイントでスイープします.Rcは「.step param Rc LIST 1 50 100 1k」で1Ω,50Ω,100Ω,1kΩの4種類とします.この3つの変数の組み合わせで等価抵抗のデータ数を増やしています.

次にX軸(横軸)にする等価抵抗は式5の計算を使います.具体的には「.meas NOISE Req PARAM Rc+1/(1/Ra+1/Rb)」で計算します.等価抵抗で発生する雑音は式4を使います.具体的には「.meas NOISE vreq PARAM sqrt(4*K*(temp+273)*Req)」で計算してY軸(縦軸)にプロットします.最後に図5の周波数1kHzにおける入力換算雑音を「.meas NOISE noise_1k FIND V(inoise) AT 1k」で調べてY軸(縦軸)にプロットします.

●R1,R2,R3の決め方

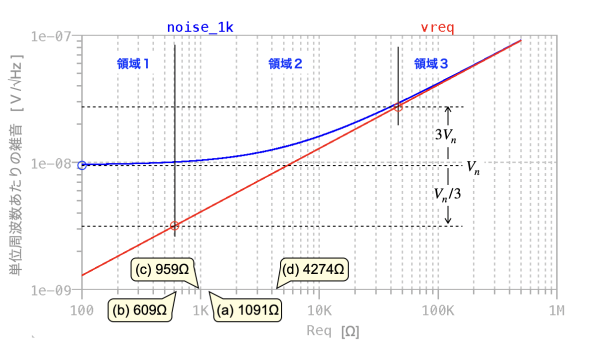

図6は,図5のシミュレーション結果で,等価抵抗と負帰還アンプの入力換算雑音の関係をデータ数を増やして視覚的に分かりやすくしたプロット図です.

このプロットを作成するには,LTspiceのパラメトリック・プロットの機能を使います.操作方法は,図5のシミュレーション終了後,「Ctrl+L」のショート・カット・キーでログ・ファイルを表示させます.ログ・ファイルのウィンドウで右クリックし,「Plot .step'ed .meas data」を選んでパラメトリック・プロットさせます.文末のダウンロードできるLTspiceファイルにはプロットを指定するファイルが同梱されているので,以上の操作方法で図6のプロットを作成できます.「.stepコマンド」の組み合わせが多いのでシミュレーション時間が長くなります.シミュレーションが終了してからパラメトリック・プロットの操作をしてください.

Reqが低くなるほど負帰還アンプは低雑音になる.

図6は「noise_1k」のプロットが,周波数1kHzでの負帰還アンプの入力換算雑音(vinoise)です.「vreq」は等価抵抗による雑音の計算結果になります.X軸には表1の(a)~(d)の等価抵抗の位置を示しました.「noise_1k」と「vreq」を比べると,雑音は2乗和の平方根で計算することから,2つの雑音の大小を比べた場合,3倍大きな雑音が支配的になります.負帰還アンプの入力換算雑音を低くするには,領域1あるいは領域2を使います.具体的には,図6を使って雑音の目標値から等価抵抗を求め,式5の等価抵抗からR1,R2,R3を選ぶことになります.

▼領域1について

領域1は,OPアンプの入力雑音(vn)が支配的になります.(b)の等価抵抗の付近が領域1と領域2の境になります.(b)の等価抵抗よりさらに低くしても,負帰還アンプの入力換算雑音はOPアンプの入力雑音(vn)より低くなりません.

▼領域2について

領域2は,OPアンプの入力換算雑音と等価抵抗の雑音の2つで決まります.等価抵抗が徐々に高くなると,負帰還アンプの入力換算雑音も高くなります.(a),(c),(d)がこの領域にあります.

▼領域3について

領域3は,等価抵抗の雑音が支配的になります.負帰還アンプに使う抵抗が高いと等価抵抗が高くなり,抵抗の雑音が支配的になります.例を挙げると,ゲインを決めるR1とR2の抵抗比は同じでも,R1とR2の絶対値が高くなると雑音は高くなります.この理由から,負帰還アンプで使える抵抗の上限は雑音で決まると言われます.

●入力換算雑音の周波数特性

図7は,図1のR1,R2,R3を表1(b)の抵抗にし,等価抵抗が領域1と領域2の境付近にします.この条件で負帰還アンプの入力換算雑音の周波数特性をシミュレーションする回路になります.

図8は図7のシミュレーション結果です.等価抵抗が領域1と領域2の境付近にあると,OPアンプの入力雑音が支配的になります.これより,負帰還アンプの入力換算雑音周波数特性は,図3のOPアンプの入力雑音周波数特性とほぼ同じになります.また,1kHzの雑音は10.1nV/√Hzであり,表2で計算した10.0nV/√Hzと一致しています.

表1(b)の抵抗は,図3のOPアンプの入力雑音の特性に近づく.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice9_036.zip

●データ・ファイル内容

OPAmp Input referred noise.asc:図2の回路

OPAmp Input referred noise.plt:図2のプロットを指定するファイル

NF Amplifer Input referred noise.asc:図5の回路

NF Amplifer Input referred noise.log.plt:図5のプロットを指定するファイル

NF Amplifer Input referred noise 2.asc:図7の回路

NF Amplifer Input referred noise 2.plt:図7のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs