CR型トーン・コントロール回路の周波数特性

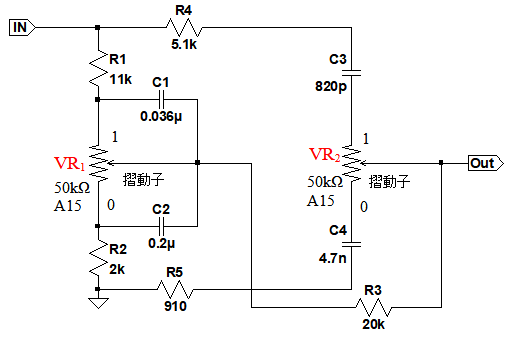

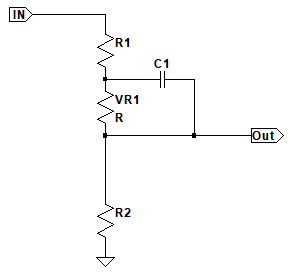

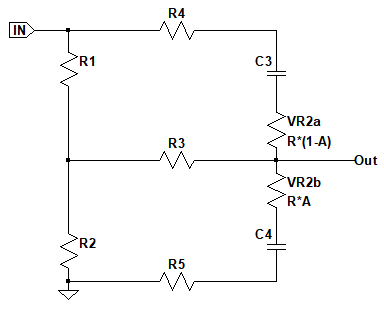

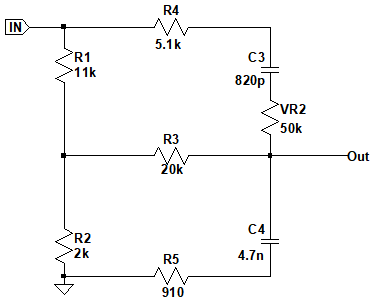

図1は,オーディオ・アンプで音質を調整するために使用するトーン・コントロール回路です.VR1とVR2の2つの可変抵抗器で,周波数特性をコントロールすることができます.VR1とVR2は,50kΩでA15カーブの可変抵抗器です.

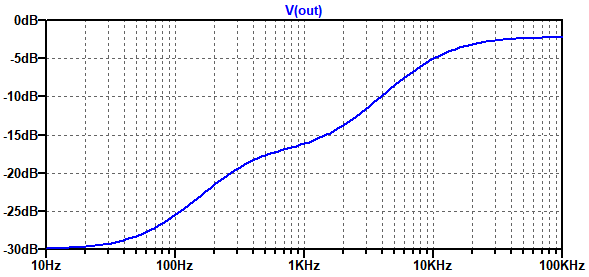

この回路で,図2のような周波数特性にするには,VR1とVR2の摺動子の位置を(a)~(d)のどれに設定すればよいでしょうか.なお可変抵抗器の摺動子が,回路図上で1番下側にあるときを0とし,1番上側にあるときを1とします.

2つの可変抵抗器で,周波数特性をコントロールできる.

この周波数特性となる,VR1とVR2の摺動子の位置は?

(a) VR1の摺動子の位置=0,VR2の摺動子の位置=0

(b) VR1の摺動子の位置=0,VR2の摺動子の位置=1

(c) VR1の摺動子の位置=1,VR2の摺動子の位置=0

(d) VR1の摺動子の位置=1,VR2の摺動子の位置=1

まず,図1の回路で,摺動子の位置を上端または下端にしたとき,どのような等価回路になるか考えます.次に,その等価回路の定数から,どのような周波数特性になるかを考えます.それを踏まえて,図2の周波数特性になるのはどのような場合かを考えれば,答えは分かります.

VR1の摺動子の位置を下端にした場合,C2がショートされた等価回路になります.その等価回路では,直流ゲインは,(R1+VR1)とR2の分圧になり-30dB程度になります.そして,C1の効果で周波数上昇とともに,減衰量が減少する特性になります.

VR2の摺動子の位置を上端にした場合,R4<<(VR2+R5)となとなるため,高域周波数の減衰量は小さくなります.この2つの周波数特性を合成した全体の周波数特性は,図2のように低域がカットされ,高域がブーストされたような特性になります.

●CR型トーン・コントロール回路

オーディオ・アンプのトーン・コントロール回路は,低域や高域を増強したり,減衰させたりして,好みの音質に調整するものです.トーン・コントロール回路には,次のNF型とCR型があります.

・NF型:オペアンプの負帰還ループの周波数特性を変化させるもの

・CR型:信号経路の周波数特性を直接コントロールするもの

ここでは,CR型のトーン・コントロール回路について解説します.CR型トーン・コントロール回路は,増幅回路を持たないため,減衰量をコントロールすることで,高域や低域の,見かけ上のブースト効果を得ています.

可変抵抗器の摺動子の位置をセンターにしたとき,CR型のトーン・コントロール回路の周波数特性は,フラットとなり,そのときの減衰量が,最大ブースト量になります.

前述の,可変抵抗器の特性(カーブ)としては,主に次の3種類があります.

・Aカーブ:ここではAカーブの中のA15カーブを使用,A15は摺動子がセンターで全抵抗の15%

の特性,他にA5,A10,A20などがある

・Bカーブ:Bカーブは線形なので特性は1つ

・Cカーブ:CカーブはAカーブと逆の特性.あまり一般的ではない

CR型のトーン・コントロール回路に,可変抵抗器のA15カーブのものを使用した場合は,摺動子の位置をセンターにしたときの減衰量は16.5dBとなります.仮に,可変抵抗器にBカーブのものを使用した場合,摺動子の位置をセンターにしたときの減衰量は6dBです.

Aカーブの可変抵抗器を使用すると,最大ブースト量を大きくできるため,CR型トーン・コントロール回路では,Aカーブの可変抵抗器が使用されます.

なお,NF型トーン・コントロール回路に関しては,LTspice電子回路マラソン 026:低域が増強されるトーン・コントロール回路はどっち?を参照してください.

また,可変抵抗器のカーブに関しては,LTspiceで学ぶオーディオ回路入門 017:ボリューム・コントロールに使用される可変抵抗器の特性を参照してください.

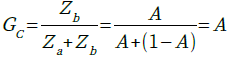

●低域コントロール用回路

図1のCR型トーン・コントロール回路は,低域コントロール用回路と,高域コントロール用回路の2つに分けることができます.図1の左側の回路が低域コントロール用の回路で,VR1で特性をコントロールします.

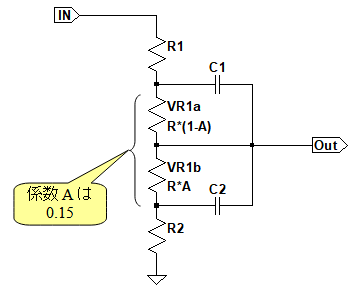

▼VR1の摺動子がセンターのとき

図3は,可変抵抗器(VR1)の摺動子の位置をセンターにしたときの,低域コントロール等価回路です.可変抵抗器(VR1)はVR1aとVR1bの2本の抵抗に置き換えています.A15カーブの可変抵抗器で摺動子の位置をセンターにした場合,下側の抵抗値は全体の抵抗の15%になります.そのため,VR1の全体の抵抗値をRとした場合,図3の係数Aは0.15となります.

変抵抗器(VR1)はVR1aとVR1bの2本の抵抗に置き換えている.

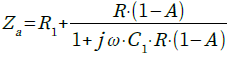

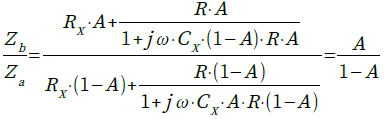

トーン・コントロール回路の動作としては,可変抵抗器の摺動子をセンターにしたときは,フラットな周波数特性となっていることが望まれます.そこで,図3の回路の周波数特性がフラットになる条件を検討します.まず,R1,C1,VR1aの合成インピーダンスをZaとすると,Zaは式1で表されます.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)そして,R2,C2,VR1bの合成インピーダンスをZbとすると,Zbは式2で表されます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)図3の回路の周波数特性がフラットになるためには,すべての周波数でZaとZbの比が一定となっている必要があります.ここで,R2とR1の比をA:(1-A)とし,R2=RX*A,R1=RX*(1-A)とします.また,C1とC2の比をA:(1-A)とし,C1=CX*A,C2=CX*(1-A)とすると,ZaとZbの比は式3のように表されます.

・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・(3)式3から,ZaとZbの比がA/(1-A)となり,周波数によらず一定となることが分かります.IN端子からOUT端子までのゲインGCは式4のようにA倍になります.

・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・(4)

▼VR1の摺動子が上端のとき

図4は,VR1の摺動子の位置を上端にしたときの,低域コントロールの等価回路です.図3のC1はショートされるため,省略しています.

図3のC1はショートされるため,省略している.

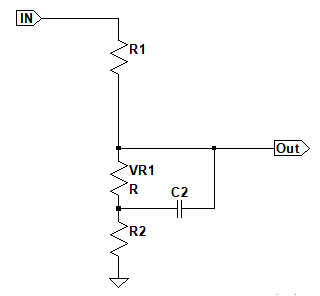

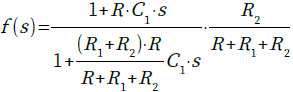

摺動子を上端にすることで,直流領域のゲインは大きくなり,C2の影響で中域が減衰する特性になります.そのため,中域を基準に考えると,低域がブーストされた特性になります.この回路の伝達関数f(s)は,式5で表されます.

・・・・・・・・・・・・・・・・・・・・(5)

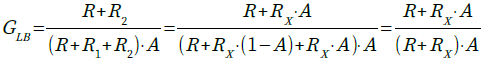

・・・・・・・・・・・・・・・・・・・・(5)直流領域のゲイン(GDC)は(R+R2)/(R+R1+R2)となります.低域のブースト量(GLB)はGDCと摺動子がセンターの場合のゲイン(GC)との比になるため,式6で表されます.

・・・・・・・・・(6)

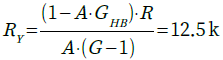

・・・・・・・・・(6)式6をRXについて解くと,式7になります.

・・・・・・・・・・・・・・・・(7)

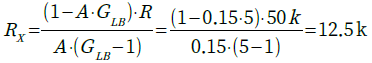

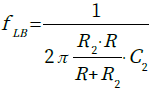

・・・・・・・・・・・・・・・・(7)ここで,GLBを5倍(14dB)に設定する場合,RXは式7のように12.5kΩとすればよいことが分かります.RXを12.5kΩとしてR1,R2を求めると,R1=12.5k*(1-A)=10.6k,R2=12.5k*A=1.9kとなります.R24シリーズの抵抗の中から,R1=11kΩ,R2=2kΩを選択します.低域が上昇を始める周波数fLBは,式5の分子の時定数から,式8のように計算できます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

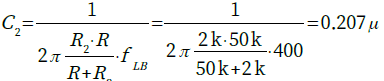

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)fLBを400Hzに設定する場合,C2は式9のように0.2μFとします.C1はC1=C2*A/(1-A)=0.036μFとします.

・・・・・・・・・・・・・・・(9)

・・・・・・・・・・・・・・・(9)

▼VR1の摺動子が下端のとき

図5は,VR1の摺動子の位置を下端にしたときの低域コントロール等価回路です.図3のC2はショートされるため,省略しています.

図3のC2はショートされるため,省略しています.

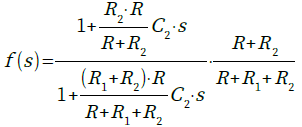

摺動子を下端にすることで,直流領域のゲインは小さくなります.C1により中域のゲインが上昇し,摺動子がセンターの場合のゲインに近づきます.中域を基準に考えると,低域が減衰した特性になります.この回路の伝達関数は式10で表されます.

・・・・・・・・・・・・・・・・・・・・(10)

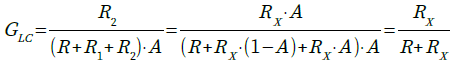

・・・・・・・・・・・・・・・・・・・・(10)直流領域のゲイン(GDC)はR2/(R+R1+R2)となります.低域のカット量(GLC)はGDCと摺動子がセンターの場合のゲイン(GC)との比になるため,式11で表されます.

・・・・・・・・・・(11)

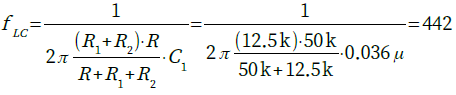

・・・・・・・・・・(11)RX=12.5k,R=50kを代入すると,0.2(-14dB)になります.低域が減衰を始める周波数fLCは分母の時定数から,式12のように計算できます.

・・・・・・・・・・(12)

・・・・・・・・・・(12)

●高域コントロール用回路

図1の右側の回路が高域コントロール用の回路で,VR2で特性をコントロールします.

▼VR2の摺動子がセンターのとき

図6は,可変抵抗器(VR1)の摺動子の位置をセンターにしたときの,高域コントロール等価回路です.図1のC1,C2は高域でインピーダンスが低くなり,ショートとみなせるものとして,VR1とともに省略しています.R3はR1,R2が高域コントロール特性に与える影響を軽減する働きをします.

図1のC1,C2は高域でショートとみなせるものとして,VR1とともに省略している.

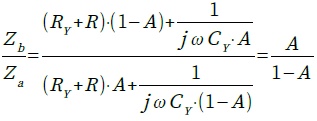

この回路で周波数特性がフラットになるためには,R4,C3,VR2aのインピーダンスZaと,R5,C4,VR2bのインピーダンスZbの比が一定になる必要があります.ここで,R4とR5の比をA:(1-A)とし,R4=RY*A,R5=RY*(1-A)とします.また,C3とC4の比をA:(1-A)とし,C3=CY*A,C4=CY*(1-A)とすると,ZaとZbの比は式13のように表されます.

・・・・・・・・・・・・・・・・・・・(13)

・・・・・・・・・・・・・・・・・・・(13)式13から,ZaとZbの比がA/(1-A)となり,周波数によらず一定となることが分かります.

▼VR2の摺動子が上端のとき

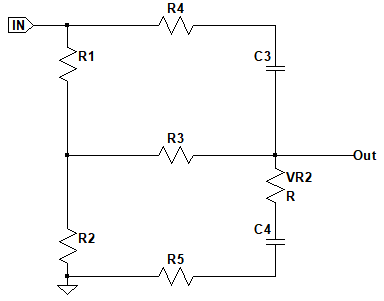

図7は,VR2の摺動子の位置を上端にしたときの,高域コントロールの等価回路です.R4<<(VR2+R5)となるように抵抗値を設定することで,高域での減衰量が小さくなり,見かけ上高域がブーストされた特性になります.

R4<<(VR2+R5)とすると,高域での減衰量が小さくなり,見かけ上高域がブーストされる.

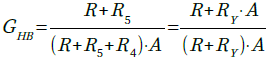

高域のブースト量(GHB)はC3,C4をショートした等価回路で,Out端子までのゲインを計算することで求めることができます.ただし,R1~R3を含めると,計算が煩雑になるので,R1~R3を無視した場合について式14で計算してみます.

・・・・・・・・・・・・・・・・・・・・・・(14)

・・・・・・・・・・・・・・・・・・・・・・(14)式14をRYについて解くと,式15になり,GHBを5倍(14dB)に設定する場合,RY=12.5kとなります.そして,R4=12.5k*(1-A)=10.6k,R5=12.5k*A=1.9kとなりますが,R1~R3を含めたシミュレーション結果を踏まえて,R4=5.1kΩ,R5=910Ωとします.

・・・・・・・・・・・・・・・・・・・・・・・・・(15)

・・・・・・・・・・・・・・・・・・・・・・・・・(15)次に,C3,C4の値を決めます.図6の回路の正確な伝達関数を計算するのは,非常に煩雑なため,C3とC4の比をA:(1-A)とした定数で,シミュレーションにより周波数特性を確認し,C3=820pF,C4=4.7nFと決定しました.

▼VR2の摺動子が下端のとき

図8は,VR2の摺動子の位置を下端にしたときの,高域コントロールの等価回路です.R4(VR2+R5)となっているため,高域での減衰量が大きくなり,高域カット特性となります.

R5<<(VR2+R4)となっているため,高域での減衰量が大きくなり,高域カット特性となる.

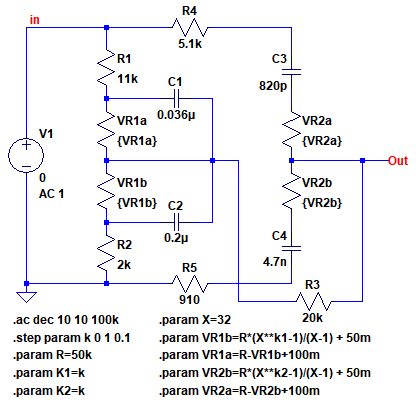

●CR型トーン・コントロール回路を確認する

図9は,CR型トーン・コントロール回路をシミュレーションするための回路です.VR1とVR2はそれぞれ2本の抵抗に置き換え,k1,k2という変数が摺動子の位置を表すように,「.param」コマンドで定数を設定しています.k1がVR1の摺動子の位置を表し, k2がVR2の摺動子の位置を表します.そして,「.step」コマンドを使用して.k1,k2を0から1まで,0.1ステップで変化させたときの周波数特性をシミュレーションします.

摺動子の位置を表すk1,k2を0から1まで,0.1ステップで変化させる.

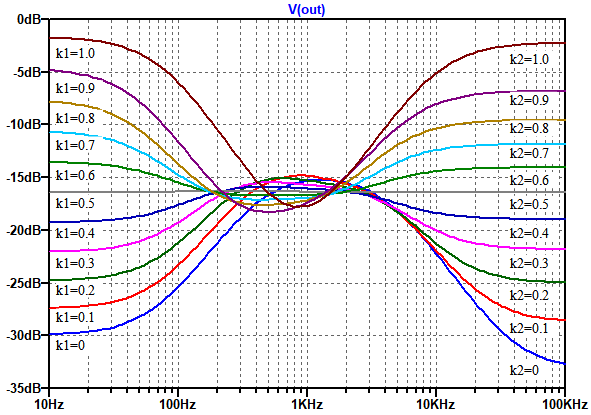

図10は,図9のシミュレーション結果です.k1,k2を変化させることで,低域と高域の周波数特性をコントロールできていることが分かります.図2の周波数特性のグラフは,図9の回路で,k1=0,k2=1としてシミュレーションしたものです.

k1,k2を変化させることで,低域と高域の周波数特性をコントロールできている.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice9_021.zip

●データ・ファイル内容

CR_tonectrl.asc:図2をシミュレーションするための回路

CR_tonectrl.plt:図2のグラフを描画するためのPlot settinngsファイル

CR_tonectrl_step.asc:図9の回路

CR_tonectrl_step.plt:図10のグラフを描画するためのPlot settinngsファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs