オーディオ周波数帯を増幅するNチャネルJFETのアンプ

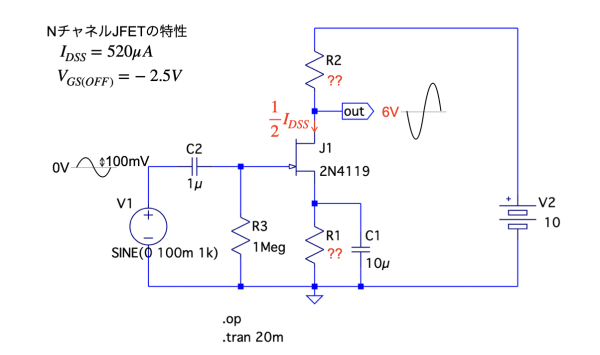

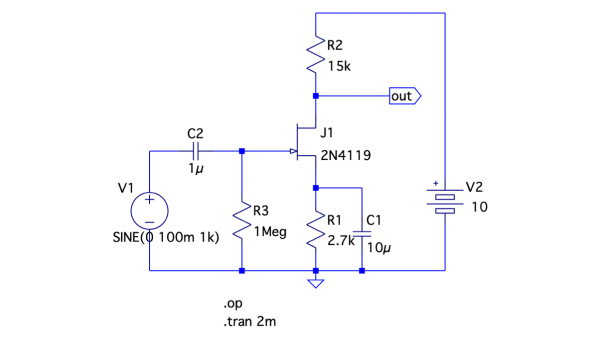

図1は,J1のNチャネル・ジャンクション電界効果トランジスタ(Junction Field Effect Transistor:JFET)を使ったオーディオ周波数帯を増幅するアンプです.NチャネルJFETの特性は,ゲート・ソース間短絡時ドレイン電流(IDSS)が520μAで,ゲート・ソース間カットオフ電圧[VGS(OFF)]が-2.5Vです.

図1で,最大の電流変化を得るため,直流動作点の目標値を,J1のドレイン電流をIDSSの半分に設定し,さらに,outの中点電圧を約6Vに設定します.この目標値に近くなるR1とR2の抵抗の組み合わせは(a)~(d)のどれでしょうか.

ドレイン電流がIDSS/2,outの中点電圧が6Vに近くなるR1とR2の抵抗は?

(a) R1=4.7kΩ,R2=15kΩ

(b) R1=4.7kΩ,R2=20kΩ

(c) R1=2.7kΩ,R2=15kΩ

(d) R1=2.7kΩ,R2=20kΩ

J1のNチャネルJFETは,R1とソース電流による電圧降下が自己バイアス電圧になり,ゲート・ソース間電圧が決まります.outの中点電圧はドレイン電流とR2の電圧降下から計算できます.

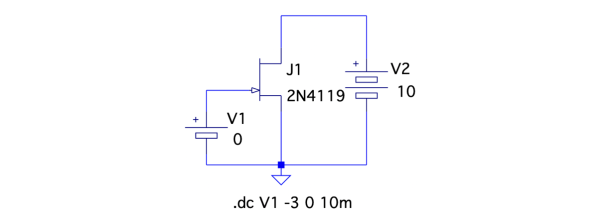

NチャネルJFETのドレイン電流(ID)を「ID=IDSS/2」にするゲート・ソース電圧(VGS)は「VGS=VGS(OFF)/3.4」の関係になります.この関係より「VGS=-2.5V/3.4=-0.735V」になります.このVGSはR1とソース電流の電圧降下で決まります.ソース電流(IS)はドレイン電流(ID)と等しいので「IS=IDSS/2=260μA」になります.オームの法則を使ってR1を求めると「R1=0.735V/260μA=2.8kΩ」になります.これよりR1は2.8kΩに近い選びやすい抵抗として「R1=2.7kΩ」になります.

次にOUTの中点電圧は,V2の電圧からドレイン電流(ID)とR2の電圧降下を減じたものです.OUTの中点電圧を6Vとすると,R2の電圧降下は4Vですので,オームの法則より「R2=4V/260μA=15.4kΩ」になります.これよりR2は15.4kΩに近い選びやすい抵抗として「R1=15kΩ」になります.この検討より,(c) R1=2.7kΩ,R2=15kΩになります.

●JFETの特徴について

電界効果トランジスタ(Filed Effect Transistor:FET)は,バイポーラ・トランジスタと同じくらい古くからあるデバイスになります.FETとバイポーラ・トランジスタを比較すると次の違いがあります.

・FETはゲート電流が流れない

・バイポーラ・トランジスタはベース電流が流れる

この違いにより,FETはバイポーラ・トランジスタより入力抵抗が高くなる特徴があります.例えば,オーディオのマイクやアンプにFETを用いると,入力抵抗が高いので信号が減衰せずにうまく伝わります.FETには,次の2種類があります.

・金属酸化膜半導体電界効果トランジスタ(Metal-Oxide-Semiconductor Field Effect Transistor:MOSFET)

・ジャンクション(接合型)電界効果トランジスタ(Junction Field Effect Transistor:JFET)

今回は,FETの中でデバイスの構造がシンプルであるJFETについて解説します.JFETの特徴は次となります.

・ゲート・ソース間の電圧(VGS)でドレイン電流(ID)を制御する

・ゲート・ソース間のPN接合を逆バイアスした状態で使用する

・逆バイアスして使うので,ゲート電流はゼロに近くなり,高い入力抵抗となる

・高い入力抵抗は,入力側と出力側を分離できる

・ゲート・ソース電圧を負電圧にして,IDSSの最大電流から0Aの電流変化を制御できる

・高い電流により発熱しても,ドレイン・ソース間の電流は負の温度特性なので熱暴走しない

●NチャネルJFETの動作と記号について

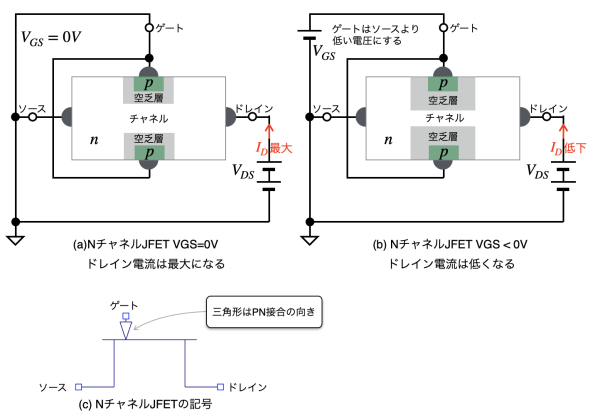

図2(a)は,NチャネルJFETのゲート・ソース電圧が「VGS=0V」のときの動作を解説する図です.また,図2(b)は,NチャネルJFETのゲート・ソース電圧が「VGS<0V」のときの動作を解説する図となります.図2(c)は,NチャネルJFETの記号になります.

NチャネルJFETは,n型の基板にp型のゲートがあります.図2(a)の「VGS=0V」のとき,NチャネルJFETの空乏層が広がらないので,チャネルが広くなり,ドレイン電流は最大になります.この状態から,図2(b)のように「VGS<0V」になるとPN接合の空乏層が広がり,チャネルが狭くなり,ドレイン電流は低くなります.このようにゲート・ソース電圧によりドレイン電流は,最大のIDSSからゼロまで変化をするデバイスになります.

図2(c)は,記号内にある三角形はPN接合の向きを表しています.PチャネルJFETの記号は三角形の向きが逆になります.

●JFETの特性

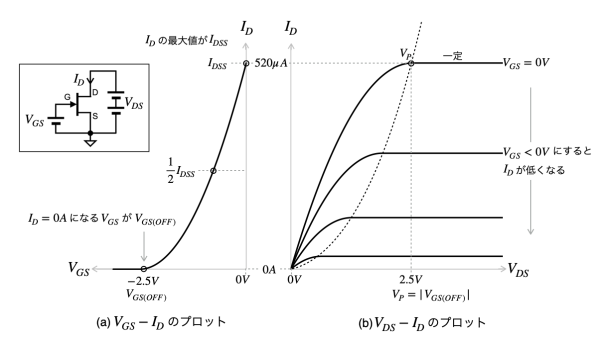

図3(a)は,ゲート・ソース電圧(VGS)を変化させたときのドレイン電流(ID)の変化をプロットした図です.図3(b)は,ドレイン・ソース電圧(VDS)を変化させたときのドレイン電流(ID)の変化をプロットした図になります.

図3(a)の「VGS=0V」のとき,ドレイン電流(ID)は最大になり,このときのドレイン電流をIDSSと呼びます.図3(a)のVGSを負側にスイープし,「ID=0A」になるゲート・ソース電圧をVGS(OFF)と呼びます.次に図3(b)はVDSを正側にスイープしたプロットになります.図3(b)の「VGS=0V」のとき,IDSSの電流で一定になるVDSをピンチオフ電圧(VP)と呼びます.ピンチオフ電圧はVGS(OFF)の絶対値と等しくなります.

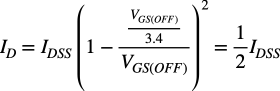

●最大の電流変化を得るIDSS/2にするVGS

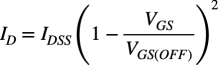

JFETをアンプとして使うときのIDの直流バイアス電流ですが,図3(a)のIDはIDSS~0までの範囲になるので,その中間のIDSS/2に設定すると,IDSS/2を境に高い方と低い方で最大の電流変化を得られます.ここではIDSS/2にするVGSについて調べます.図3(a)のVGS-IDの関係は式1になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

IDをIDSS/2に設定し,このときのVGSをVGS(OFF)と変数xで表すと式2になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

式2よりxを求めると「x=3.414」になります.キリの良い数値として「x=3.4」とします.この解析より,式1のIDをIDSS/2に設定し,VGSをVGS(OFF)と変数xで表すと式3の関係になります.

・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・(3)

これで,IDをIDSS/2にするVGSは式4になります.式4へ図1の「VGS(OFF)=-2.5V」を入れると,「VGS=-0.735V」になります.

・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・(4)

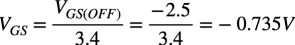

次にJ1のトランスコンダクタンス(gm)は,式1をVGSで微分したものなので式5になります.

・・・・・・・・・・・・(5)

・・・・・・・・・・・・(5)

トランスコンダクタンスは,アンプのゲインを計算するときに使います.

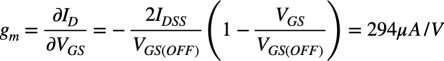

●直流解析

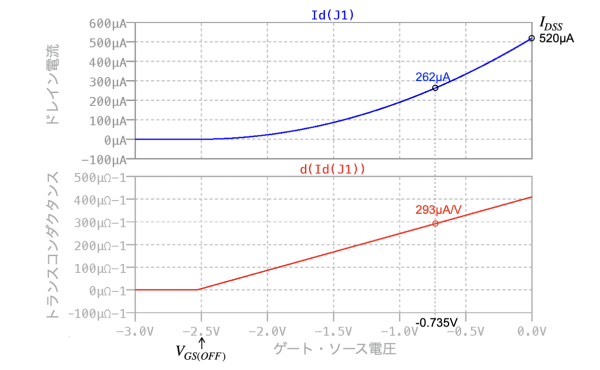

図4は,図1のJ1のVGS-ID特性を直流解析で調べる回路です.図4は,V1を-3V~0V間を10mVステップでスイープし,J1のドレイン電流をプロットします.

図5は,図4のシミュレーション結果です.図5上段はVGS-IDのプロット,図5下段は図5上段のドレイン電流に対応したトランスコンダクタンスになります.図5上段より,式4で求めた「VGS=-0.735V」のとき,ドレイン電流はIDSSの半分になる約262μAになるのがわかります.そして図5下段より,そのときのトランスコンダクタンスは式5とほぼ同じの293μA/Vになるのが確認できます.

上段はVGS-ID特性のプロット,下段はトランスコンダクタンス.

VGS=-0.735VのときIDはIDSS/2=262μAになる.

VGS=-0.735Vのときgmは293μA/Vになる.

●抵抗値とゲインの机上計算

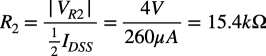

図6は,図1のR1とR2を机上計算で求め,その後直流動作点をop解析,ゲイン周波数特性をac解析し,2つの解析を同時にシミュレーションする回路です.まず先に,式4で求めたVGSとIDSS/2を用いてR1を求めます.J1のゲートはR3でGNDに接続しています.ゲート電流はゼロに近い電流なので,ゲート電圧はほぼGNDと考えることができます.このときJ1のドレインからソースにかけて電流が流れてR1に電圧降下が生まれ,ソース電圧はGNDより高くなり,「VGS<0V」になります.具体的にはR1の電圧降下を0.735Vにすると式4の「VGS=-0.735V」になります.

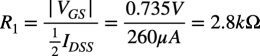

R1を机上計算します.J1のソース電流(IS)は,ドレイン電流(ID)と等しいので「IS=IDSS/2=260μA」になります.このときのVGSは式4で求めたVGSの絶対値「|VGS|=0.735V」を使うと,R1はオームの法則より式6になります.これよりR1は2.8kΩに近い選びやすい抵抗として「R1=2.7kΩ」になります.このようにJ1のソース電流とR1の電圧降下を用いたバイアス電圧の加え方を自己バイアスと呼びます.

・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・(6)

次に,OUTの中点電圧は,V2の電圧からドレイン電流(ID)とR2の電圧降下を減じたものです.OUTの中点電圧を6Vとすると,R2の電圧降下は4Vですので,オームの法則より「R2=4V/260μA=15.4kΩ」になります.これよりR2は15.4kΩに近い選びやすい抵抗として「R2=15kΩ」になります.

・・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・・(7)

図6のゲート,ドレイン,ソースの各電圧は,op解析で分かります.図6ではop解析の結果を青字で示しました.ゲート電圧は7μVなのでほぼGNDです.ソース電圧は「R1=2.7kΩ」の選びやすい抵抗にしたので0.69Vとなり,「VGS=-0.69V」になります.outの中点電圧は「R2=15kΩ」にしたので,「Vout=6.2V」になります.このR1とR2が回答の(c)になります.

次に回路のゲインを検討します.J1のソースとGND間にあるC1の効果により,ソースは交流的にGNDと考えることができます.これより式5の「gm=294μA/V」と「R2=15kΩ」より式8になります.

・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・(8)マイナスの符号は位相が反転することを表しています.

●ゲインをシミュレーションで調べる

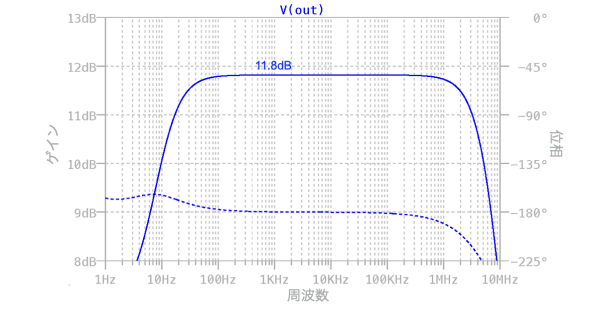

図7は,図6のac解析の結果をプロットしました.ac解析は「.ac oct 30 1 10meg」の指定で,1Hz~10MHz間を周波数が2倍あたり30ポイントでスイープした結果になります.

ゲインは11.8dB(3.9倍),位相は反転する.

図7の実線がゲイン,点線が位相になります.V1とNチャネルJFETのアンプの間はC2で結合しているので,約100Hz以上の周波数でゲインが落ち着きます.図7よりゲインは式8に近い11.8dB(3.9倍),位相は180°違うのでoutはV1の入力の位相から反転します.

●outの波形をシミュレーションで調べる

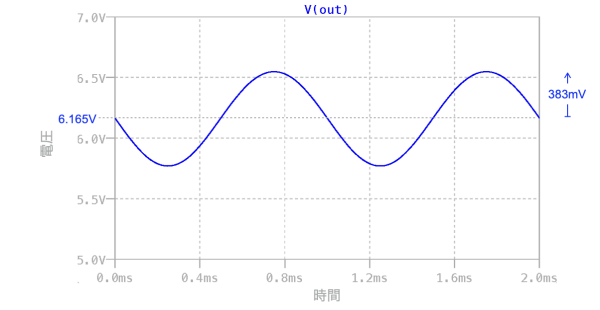

図8は,図1のR1とR2の値を「R1=2.7kΩ,R2=15kΩ」とし,tran解析でoutの波形を調べる回路になります.V1は振幅が100mV,周波数が1kHzの正弦波を入力しています.tran解析は「.tran 2m」の指定で0ms~2ms間の解析になります.

図9は,図8のシミュレーション結果でoutの信号をプロットしました.outの信号は約6.2Vが中点電圧で振幅が383mVになり,位相が反転した正弦波になります.図7で調べたゲインは3.9倍ですので,ac解析の結果とほぼ一致した振幅になります.

outの中点電圧は6.2V,振幅は383mVになるのが分かる.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice9_014.zip

●データ・ファイル内容

JFET Transfer_Characteristics.asc:図4の回路

JFET Transfer_Characteristics.asc:図4のプロットを指定するファイル

JFET Self-Bias AC.asc:図6の回路

JFET Self-Bias AC.plt:図6のプロットを指定するファイル

JFET Self-Bias Tran.asc:図8の回路

JFET Self-Bias Tran.plt:図8のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs