オーディオ用パワー・アンプのダンピング・ファクタとは

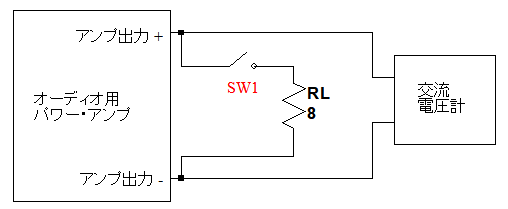

図1は,オーディオ用パワー・アンプのダンピング・ファクタ(DF)を測定する回路です.定格インピーダンス8Ωのスピーカを使用したときにDFを測定するため,8Ωの抵抗負荷を使用しています.

まず,スイッチ(SW1)がOFFの状態で,パワー・アンプに1kHzの正弦波を入力します.そして,パワー・アンプ出力を交流電圧計で測定して,1VRMSになるようにパワー・アンプのボリュームを調整しました.次に,SW1をONさせ,交流電圧計でパワー・アンプの出力を計測した所,980.4mVRMSでした.

このパワー・アンプのダンピング・ファクタの値は(a)~(d)のどれでしょうか.

SW1がOFFのときとONのときの出力レベルから,DFを計算する.

(a) 20 (b) 50 (c) 98 (d) 200

ダンピング・ファクタ(DF)は,オーディオ用パワー・アンプの性能を表す指標の1つです.一般的に,数値が大きいほど,性能が良いとされています.使用するスピーカの定格インピーダンス(RL)と,パワー・アンプの出力抵抗(RO)の比として定義されており,DFは「DF=RL/RO」で計算できます.出力抵抗は,SW1がOFFのときとONのときの出力レベルの変化から計算することができます.出力抵抗が分かれば,DFは簡単に計算できます.

SW1がONのとき,パワー・アンプの出力は,パワー・アンプの出力抵抗(RO)と負荷抵抗(RL)で分圧されます.SW1がOFFのときの出力レベルをVOとし,SW1がONのときの出力レベルをVLとすると,VLは「VL=VO*RL/(RL+RO)」で計算できます.この式とダンピン・グファクタ(DF)の定義式を使用して,式を変形すると,DFはDF=VL/(VO-VL)となります.問題文の数値を代入すると,DF=980.4mV/(1V-980.4mV)=50となります.

●オーディオ用パワー・アンプのダンピング・ファクタとは

ダンピング・ファクタ(DF)は,オーディオ用パワー・アンプの性能を表す指標の1つです.使用するスピーカの定格インピーダンス(RL)と,パワー・アンプの出力抵抗(RO)の比として定義され,式1で計算することができます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

式1から分かるように,出力抵抗(RO)が小さいほど,DFは大きくなります.通常,オーディオ用スピーカは,出力抵抗の十分小さいパワー・アンプで駆動したときに,最適な周波数特性となるように設計されています.

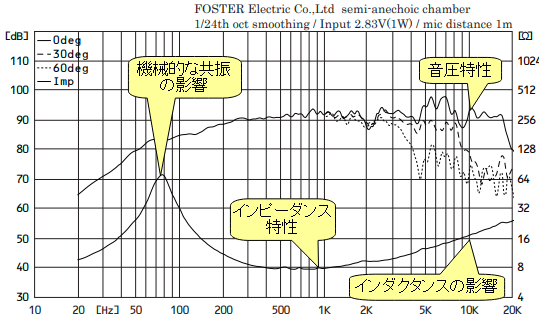

図2は,フォスター電機株式会社(FOSTEX)のFE126NV2というスピーカの仕様書に記載されている,スピーカの周波数特性です.

このスピーカの定格インピーダンスは8Ωですが,インピーダンスのグラフを見ると2kHz以上で大きくなっています.また300Hz以下でも大きくなっており,80Hz付近でインピーダンスが最大になっています.

このように,スピーカのインピーダンスは,一定ではなく,周波数によって異なっています.そのため,DFが小さく,出力抵抗の大きなパワー・アンプでスピーカを駆動すると,出力抵抗とスピーカのインピーダンスで分圧されるため,実際にスピーカに加わる電圧が,周波数によって変化してしまいます.そのため,DFの値によって,スピーカから出力される音圧の周波数特性が変化することになります.

インピーダンスは一定ではなく,周波数によって異なっている.

●ダンピング・ファクタによる周波数特性の変化を確認

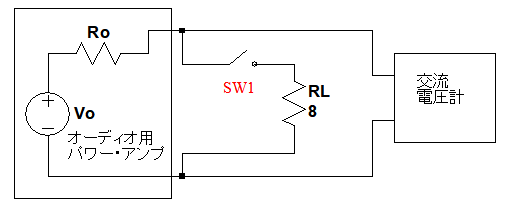

図3は,ダンピング・ファクタ(DF)を変えたときに,スピーカに印加される電圧の周波数特性がどのように変化するかをシミュレーションするための回路です.

スピーカの等価回路は図2のインピーダンス特性を模擬したものになっている.

スピーカ部分は,図2のスピーカのインピーダンス特性を模擬した等価回路を使用しています.パワー・アンプは,信号源に出力抵抗を挿入したものになっています.出力抵抗の値は,スピーカの定格インピーダンスの8Ωを,DFで割ったものになっています.そして,DFを,1から100までディケードあたり3ポイントで変化させたときの周波数特性をシミュレーションします.等価回路に関しての詳細は,「オーディオ用ダイナミック・スピーカの構造と等価回路」を参照ください.

図4は,DFを変えたときのスピーカ印加電圧の周波数特性のシミュレーション結果です.DFが小さい1のときは,1kHzのときのレベルが6dB減衰しており,相対的に見ると,高域と低域が増強された周波数特性となっています.

逆に,DFが大きくなっていくと,1kHzの減衰は小さくなり,周波数特性はフラットなものに近づいていきます.DFが22以上では,ほぼフラットな周波数特性となっています.

DFが小さいときは,相対的には高域と低域が増強された周波数特性となっている.

●ダンピング・ファクタの測定方法

図5は,図1のダンピング・ファクタ(DF)の測定回路を書き換えたものです.スイッチで負荷の接続と非接続を切り替え,それぞれの出力レベルからDFを求めます.

SW1がONときは,パワー・アンプの出力はROとRLで分圧される.

スイッチ(SW1)がOFFのときのパワー・アンプの出力レベルをVOとし,SW1がONのときの出力レベルをVLとします.SW1がONときは,パワー・アンプの出力はROとRLで分圧されるため,VLは式2で表されます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)式2からROを求めると,式3になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)一方,DFは,RLをROで割ったものなので,DFの定義式に,式2のROを代入使用して変形すると,式4のようになります.

・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・(4)つまり,SW1がONのときの出力レベル(VL)と, SW1がOFFのときの出力レベル(VO)から,DFを計算できることが分かります.式4に問題文の値を代入すると,式5のようにDFは50となることが分かります.

・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・(5)

●ダンピング・ファクタ測定結果を確認する

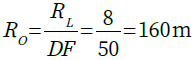

図6は,図1のダンピング・ファクタ(DF)の測定回路の測定結果を,シミュレーションで確認するための回路です.パワーアンプは電圧源(V1)と出力抵抗(RO)で構成されています.

0~10msecの間,SW1はOFFとなっており,10msec経過後ONになる.

DFが50になるROの値は,式6のように160mΩになるため,ROの値を160mΩとしています.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)SW1を経由して負荷抵抗RLが接続されています.SW1はV2でコントロールしていますが,0~10msecの間,SW1はOFFとなっており,10msec経過後ONになるように設定されています.

図7は,図6のDFの測定回路のシミュレーション結果です.上段がSW1のコントロール電圧で,下段がパワー・アンプの出力電圧(V(L))です.

10msec後に出力振幅が小さくなるが, 非常に小さな変化のため確認できない.

10msec後にSW1がONすると,パワー・アンプの出力電圧は若干小さくなるのですが,非常に小さな変化のため,図7では確認することができません.そこで,SW1がOFFのときとSW1がONのときのパワー・アンプ出力波形を分離してプロットしてみます.

図8は,図7のシミュレーション結果を0~10msecと10msec~20msecに分離して表示したものです.図8の左が0~10msecのパワー・アンプの出力で,図8の右が10msec~20msecのパワー・アンプの出力です.

SW1がOFFのときの出力電圧が1VRMSで,SW1がONのときは980.4mVRMSとなる.

左側のパワー・アンプの出力は1VRMSで,右側のパワー・アンプの出力は980.4mVRMSとなっていることが分かります.このように,DFが50のパワー・アンプを,図1の測定回路で測定すると,SW1がOFFのときの出力電圧が1VRMSで,SW1がONのときの出力電圧は980.4mVRMSとなることが確認できました.

以上,オーディオ用パワー・アンプのダンピング・ファクタ(DF)について解説しました.パワー・アンプの出力抵抗は,負帰還を掛けることで,大幅に小さくすることができます.一般的なパワー・アンプは適切な負帰還がかかっており,DFは,十分大きな値になります.負帰還と出力抵抗の関係に関しては,「IoT時代のLTspiceアナログ回路入門:負帰還による出力抵抗低減効果」を参照してください.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice9_013.zip

●データ・ファイル内容

DF_SPK.asc:図3の回路

PW_AMP_DF_MM.asc:図6の回路

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs