オーディオ周波数帯を増幅するNチャネルMOSFETのアンプ

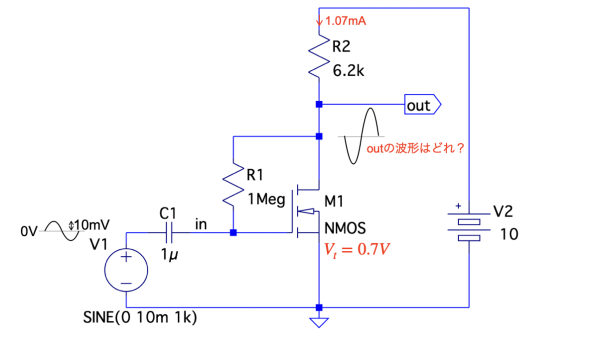

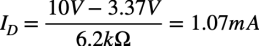

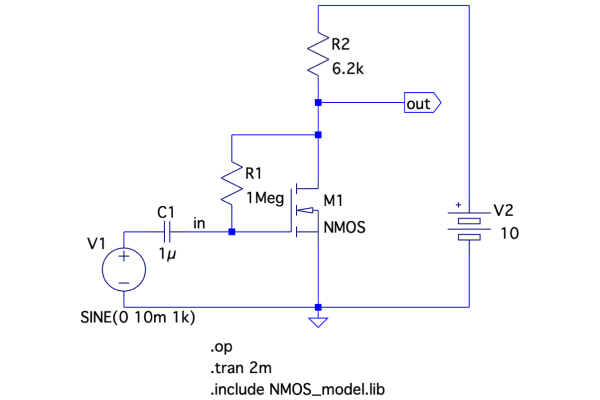

図1は,M1のNチャネルMOSFETを使ったオーディオ周波数帯を増幅するアンプです.V1の振幅が10mVの正弦波のとき,outの波形は,図2の(a)~(d)のどの波形でしょうか.ただし,M1のNチャネルMOSFETのスレッショルド電圧はVt=0.7V,V1が無信号のときのR2の電流は1.07mAとします.

R2の直流電流は1.07mA,M1のスレッショルド電圧はVt=0.7V

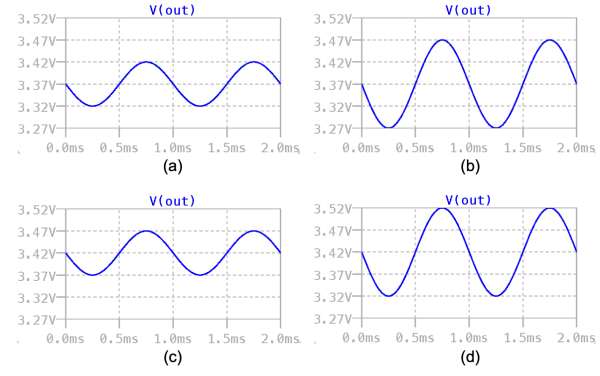

(a)の波形 (b)の波形 (c)の波形 (d)の波形

M1のNチャネルMOSFETは,R1でドレインとゲートを接続した,ドレイン・フィードバック・バイアスでゲート電圧が決まります.この回路のoutの直流電圧とゲインを調べ,波形がどうなるかを検討します.

M1のNチャネルMOSFETは,ゲート電流が流れないので,V1が無信号のときM1のゲート電圧がドレイン電圧と同じになります.また,この電圧がoutの中点電圧になります.具体的には,outの中点電圧は,ドレイン電圧をVDとすると「VD=10V-1.07mA×6.2kΩ=3.37V」になります.この直流電圧の検討より,(a)と(b)が候補になり,(c)と(d)は消えます.

次にゲインの検討をします.R2の電流はM1のドレイン電流となり,M1のトランスコンダクタンスは「gm=801μA/V」になります.ゲインは「G=-gmR2」で決まり,「R2=6.2kΩ」なので,おおよそ「G=-5」になります.以上よりoutの振幅は50mVで位相が反転した信号になり,この波形になるのは(a)になります.

●トランジスタの種類

トランジスタには,大きく分けて,次の3種類があります.

・バイポーラ・トランジスタ(Bipolar Junction Transistor:BJT)

・電界効果トランジスタ(Filed Effect Transistor:FET)

・絶縁ゲート型バイポーラ・トランジスタ(Insulated Gate Bipolar Transistor:IGBT)

上記3種類の中で,オーディオ周波数帯の増幅に,一般的に使用される電子部品は,次の2種類になります.

・バイポーラ・トランジスタ(Bipolar Junction Transistor:BJT)

・電界効果トランジスタ(Filed Effect Transistor:FET)

▼バイポーラ・トランジスタと電界効果トランジスタの違い

バイポーラ・トランジスタと呼ばれる理由は,動作の特性として,正孔と電子の2つのキャリアが関係するからです.一方,電界効果トランジスタは,正孔または電子のいずれか1つが関係するので「ユニポーラ・トランジスタ」とも呼ばれます.

バイポーラ・トランジスタと電界効果トランジスタの違いは,バイポーラ・トランジスタは,ベース電流によって制御します.電界効果トランジスタは,ゲート電圧による電界によって制御します.この違いにより,バイポーラ・トランジスタは,ベース電流が流れるので入力抵抗が低くなります.また,電界効果トランジスタは,ゲート電流が流れないので,バイポーラ・トランジスタより入力抵抗を高くすることができます.

▼電界効果トランジスタの種類

また,電界効果トランジスタ(FET)には,次の2種類があります.

・ジャンクション電界効果トランジスタ(Junction field effect transistor:JFET)

・金属酸化膜半導体電界効果トランジスタ(metal-oxide-semiconductor field effect transistor:MOSFET)

さらに,MOSFETには,次の2種類があります.

・Nチャネル型

・Pチャネル型

ここでは,NチャネルMOSFETを使った,オーディオ周波数帯の信号を増幅するアンプ回路の解説を行います.

●NチャネルMOSFETの動作と記号について

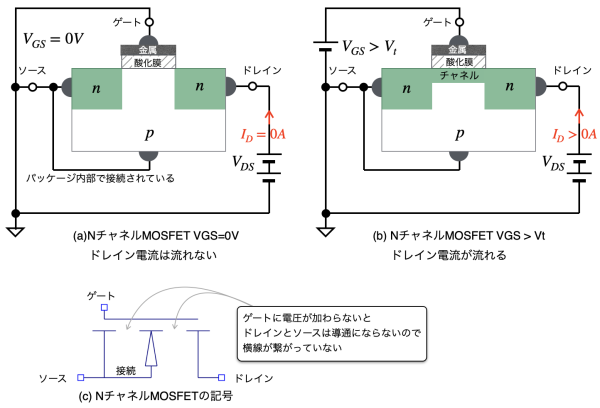

図3(a)は,NチャネルMOSFETのゲート・ソース電圧が「VGS=0V」のときの図です.また,図3(b)は,NチャネルMOSFETのゲート・ソース電圧が「VGS>Vt」のときの図です.図3(c)は,NチャネルMOSFETの記号になります.

(a) VGS=0Vのときドレイン電流は流れない

(b) VGS>Vtになるとドレイン電流が流れる

(c) NチャネルMOSFETの記号

NチャネルMOSFETは,p型の基板にn型のドレインとソースがあります.ゲートの金属の下に酸化膜があり,ゲート電流は構造上流れません.p型の基板はパッケージ内部でソースに接続されており,ゲート,ドレイン,ソースの3端子のデバイスになります.

図3(a)の「VGS=0V」のとき,NチャネルMOSFETのドレイン電流は流れません.この状態から図3(b)のように「VGS>Vt」になるとゲートの正の電圧の電界でp型基板の電子が酸化膜の下に引き寄せられてチャネルを形成し,ドレインからソースへ電流が流れます.このようなモードをエンハンスメント・モードと呼びます.Vtはドレイン電流が流れ始める最小のVGSを表し,スレッショルド電圧と呼びます.エンハンスメントモードのMOSFETは,ゲート電圧が高くなるとチャネルが広がりドレイン電流が増加するので,ゲート電圧により制御するデバイスになります.

図3(c)の記号は,図3(a)の状態を表しており,p型の基板とn型のドレインは接続し,ゲートに電圧が加わらないとドレインとソース間に電流が流れないことから,ドレインとソースは線が繋がっていない記号になります.記号内にある三角形はPN接合の向きを表しています.PチャネルMOSFETの記号は三角形の向きが逆になります.

●直流解析

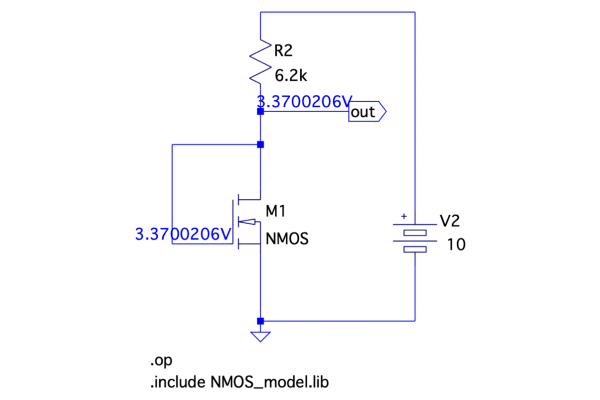

図1のV1とM1のゲートの間にはC1があるので,V1の直流電圧はM1のゲートに伝わりません.そして,R1によるドレインとゲートを接続したドレイン・フィードバック・バイアスは,M1のゲートに電流は流れないのでR1の電圧降下は無く,ゲートとドレインは同じ直流電圧になります.これより,図4は,図1の直流解析の等価回路となります.

図1のゲートには電流が流れないのでR1の電圧降下は無い.

ゲートとドレインをショートした回路と等価になる.

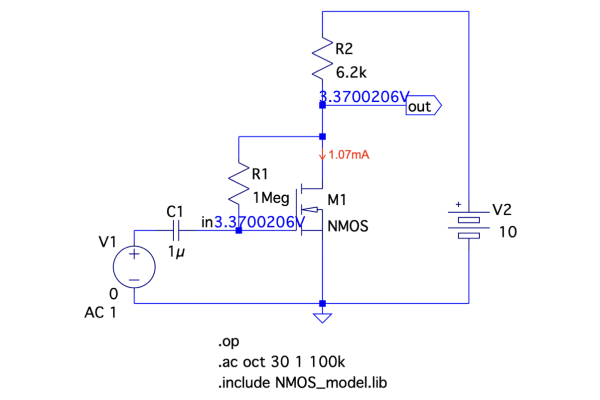

図4は「.op解析」でoutの直流電圧を回路図へ示しました.outの直流電圧は3.37Vになり,この電圧がoutの信号が振れたときの中点電圧になります.M1のドレイン電流はoutの直流電圧とV2の電圧,そしてR2の抵抗値より式1になります.

・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・(1)M1のドレイン電流はゲインを求めるときに使用します.

●ゲインを机上計算する

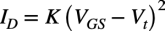

図5は,図1のac解析をする回路になります.この回路に直流解析で調べたM1ゲート電圧とoutの直流電圧,M1のドレイン電流を示しました.

M1のドレイン電流(ID)とゲート・ソース電圧(VGS)とスレッショルド電圧(Vt)の関係は式2になります.ここでKはMOSFETのトランスコンダクタンス・パラメータです.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

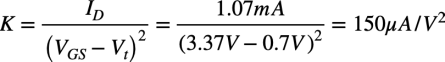

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)図5より,ドレイン電流は「ID=1.07mA」,M1のソースはGNDなので「VGS=3.37V」,スレッショルド電圧は「Vt=0.7V」とすると, トランスコンダクタンス・パラメータ(K)は式3になります.

・・・・・・・・・・・(3)

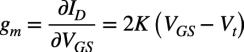

・・・・・・・・・・・(3)M1のトランスコンダクタンス(gm)は,式2をVGSで微分したものなので式4になります.

・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・(4)式4へ式3のKとVGSとVtを入れると,gmは式5になります.

・・・・・(5)

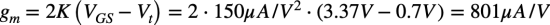

・・・・・(5)ゲイン(G)はgmとR2より求められ,式6になります.

・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・(6)式6よりゲインはおおよそ5倍,マイナスの符号は位相が反転することを表しています.

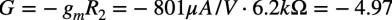

●ゲインをシミュレーションで調べる

図6は,図5のac解析の結果をプロットしました.ac解析は「.ac oct 30 1 100k」の指定で,1Hz~100kHz間を周波数が2倍あたり30ポイントでスイープした結果になります.

図6の実線がゲイン,点線が位相になります.V1とNチャネルMOSFETのアンプの間はC1で結合しているので,10Hz以上の周波数でゲインが落ち着きます.図6よりゲインは4.95倍,位相は180°違うので反転しており,式6の結果と同じになるのが分かります.

ゲインは13.9dB(4.97倍),位相は反転する.

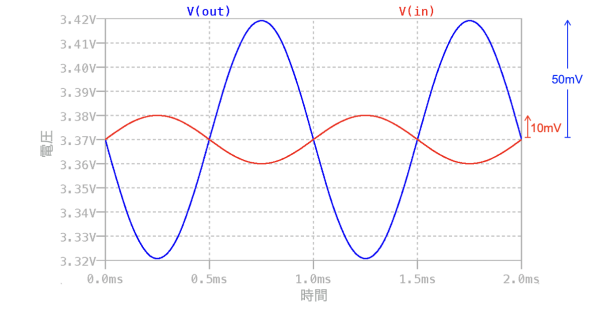

●outの波形をシミュレーションで調べる

図7は.図1のtran解析をする回路になります.V1の振幅が10mV,周波数が1kHzの信号を入力し,outの波形を調べます.tran解析は「.tran 2m」の指定で0ms~2ms間の解析になります.

図8は,図7のシミュレーション結果で,M1のゲートの信号(inのラベル)とoutの信号をプロットしました.M1のゲートの信号は,V1の信号がC1を通過した後,ドレイン・フィードバック・バイアスにより3.37Vを中点電圧にした振幅が10mVの正弦波になります.その信号をNチャネルMOSFET使ったゲインが5倍のアンプで増幅するので,outの信号は3.37Vが中点電圧で振幅が50mVになり,位相が反転した正弦波になります.このプロットより,解答の(a)の波形になるのが分かります.

outは(a)の波形になるのが分かる.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice9_012.zip

●データ・ファイル内容

Drain feedback Bias DC.asc:図4の回路

Drain feedback Bias AC.asc:図5の回路

Drain feedback Bias AC.plt:図5のプロットを指定するファイル

Drain feedback Bias Tran.asc:図7の回路

Drain feedback Bias Tran.plt:図7のプロットを指定するファイル

NMOS_model.lib :NチャネルMOSFETのモデルパラメータ

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs