オーディオ機器でのソース・フォロア回路のひずみ

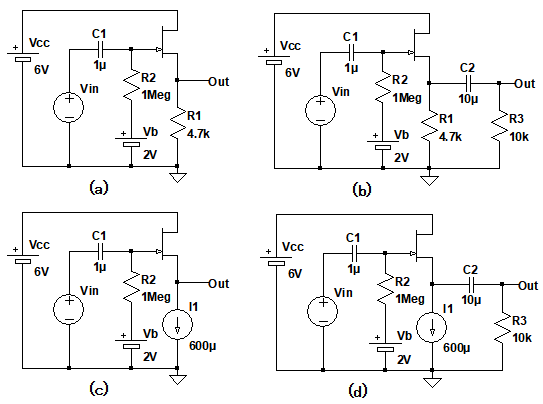

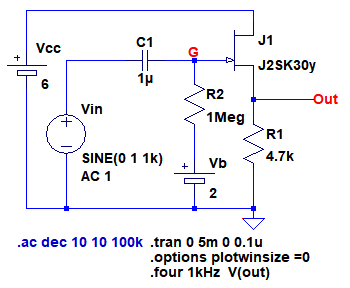

図1の(a)~(d)は,ジャンクションFETを使用したソース・フォロア回路です.図1のそれぞれの回路において,Vinからピーク電圧1Vで1kHzの信号を入力したとき,Out端子の全高調波ひずみ率が最も小さいのは,(a)~(d)のどれでしょうか.

なお,無信号時のジャンクションFETのドレイン電流は,どの回路も同じになっているものとします.

Out端子の全高調波ひずみ率が最も小さいのは?

(a)の回路 (b)の回路 (c)の回路 (d)の回路

ソース・フォロア回路は,オーディオ機器の中で,バッファ・アンプとして使用されることがあります.ソース・フォロア回路では,ソース端子の電圧は,ゲート端子の電圧変化に追従して変化します.このとき,ソース端子の電圧が,ゲート端子の電圧を正確に追従できない場合にひずみが発生します.この点に着目すれば答えが分かります.

ソース・フォロア回路では,ソース端子の電圧は,ゲート端子の電圧から,ジャンクション・FETのゲート・ソース間電圧を引いたものになります.信号を加えたときに,ジャンクション・FETのゲート・ソース間電圧が非線形に変化すると,ソース端子の電圧は,ゲート端子の電圧を正確に追従できず,ひずみが発生します.

ジャンクション・FETのゲート・ソース間電圧は,ドレイン電流によって変化します.図1の(a)~(d)の中で,信号を加えたときに,ジャンクション・FETのドレイン電流が変化しないのは(c)だけです.そのため,全高調波ひずみ率が最も小さいのは(c)になります.

●ジャンクションFETの特性

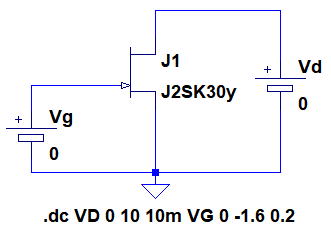

ソース・ホロア回路の動作を解析する前に,ジャンクションFETの特性を確認しておきます.図2はジャンクションFETの特性をシミュレーションするための回路です.DC解析で,ドレイン電圧(Vd)を0Vから10Vまで10mVステップで変化させ,さらにゲート電圧(Vg)を0Vから-1.6Vまで0.2Vステップで変化させます.

DC解析で,ドレイン電圧とゲート電圧を変化.

図3がジャンクションFETの特性のシミュレーション結果です.図3では,ドレイン電流(Id)を表示していますが,グラフの色とゲート電圧(Vg)の関係が分かるように,対応表を表示しています.この対応表は,グラフ画面でマウスを右クリックし,表示されたメニューから[View]⇒[Step Legend]を選択することで,表示することができます.

ゲート電圧が0Vのときが最もドレイン電流が大きく,ゲート電圧に負(-)の電圧を印加すると,ドレイン電流が減少することが分かります.一般的なMOSFETでは,ゲートに正(+)の電圧を印加して使用しますが,ジャンクションFETの場合はゲートに負(-)の電圧を印加して使用します.

ゲート電圧が0Vのときが最もドレイン電流が大きい.

●ソース・フォロア回路の動作を解析する

ここでは,図1の(a)~(d)の回路をシミュレーションし,ジャンクションFETを使用したソース・フォロア回路の動作を解析します.

▼図1(a)のソース・フォロア回路

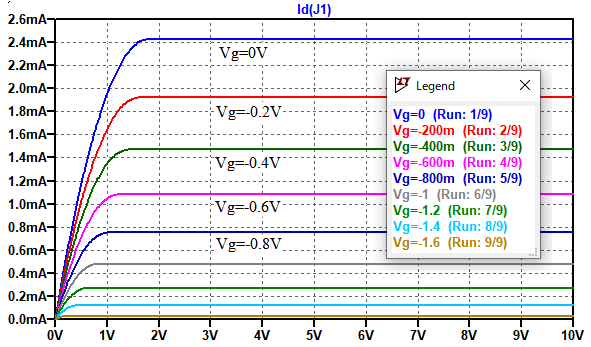

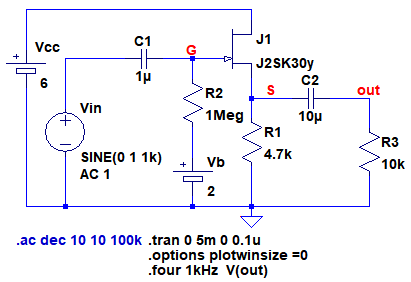

図4は,図1(a)のソース・フォロア回路をシミュレーションするための回路です.この回路では,2Vの電圧源(Vb)に接続された1MΩの抵抗(R2)で,ジャンクションFETのゲートにバイアス電圧を印加しています.ジャンクションFETは,ゲートに流れる電流が非常に小さいため,大きな値のバイアス抵抗を使用することができます.ソース端子に接続された,4.7kΩの抵抗(R1)で,ジャンクションFETの動作電流を設定しています.Vinはピーク電圧1Vで1kHzの信号を発生するように設定しています.

ソースに接続された抵抗(R1)で,ジャンクションFETの動作電流を設定している.

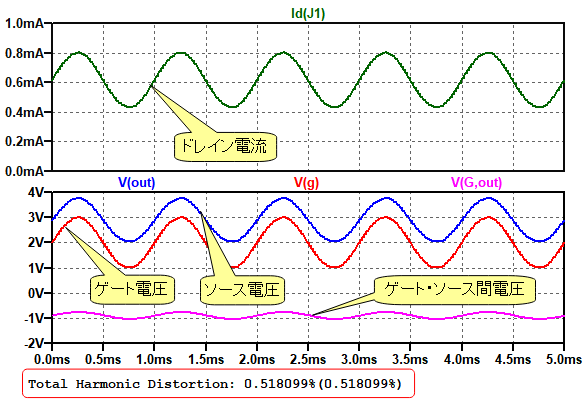

図5は,図1(a)のソース・フォロア回路のシミュレーション結果です.Out(ソース)端子の電圧は,ゲート端子よりも1V程度高くなっています.

「.Four」によるひずみ解析では,THDは0.52%となっている.

一般的なMOSFETを使用したソース・フォロア回路では,ゲートよりもソースのほうが電圧が低くなりますが,ジャンクションFETを使用したソース・フォロア回路では電圧が逆転します.そして,ソース端子は,信号の入力されたゲート端子の電圧の動きに合わせて,追従するように変化していることが分かります.

ジャンクションFETのゲート・ソース間電圧も表示していますが,小さく変動しています.これはドレイン電流の変化により,ジャンクションFETのゲート・ソース間電圧が変化するためです.ドレイン電流の変化に対して,ゲート・ソース間電圧が直線的に変化するのであれば,Out端子の波形はひずみませんが,ゲート・ソース間電圧は非線形に変化するため,Out端子の波形にひずみが発生します.「.Four」によるひずみ解析では,Out端子のTHDは0.52%となっています.

▼図1(b)のソース・フォロア回路

図6は,図1(b)のソース・フォロア回路をシミュレーションするための回路です.この回路は,図1(a)のソース・フォロア回路にC2とR3が追加されたものです.R3は,ソース・フォロア回路をバッファ・アンプとして使用した場合の,次段の入力インピーダンスに相当するものです.

次段の入力インピーダンスに相当するC2とR3が追加されている.

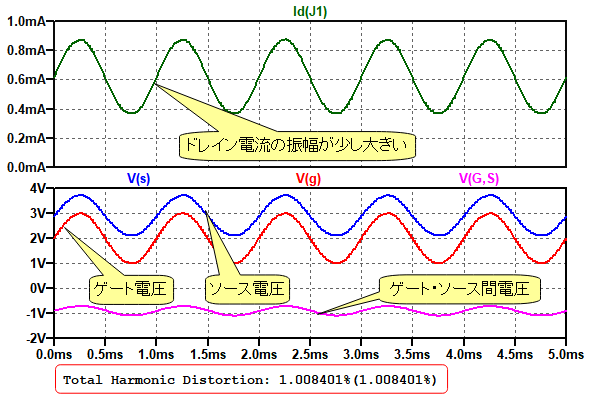

図7は,図1(b)のソース・フォロア回路のシミュレーション結果です.図1(a)の回路のシミュレーション結果とほとんど同じですが,ドレイン電流の振幅が少し大きくなっています.これは,R3に流れる信号電流が追加されるためです.ドレイン電流の振幅が大きくなったことにより,ゲート・ソース間電圧の変化も若干大きくなり,「.Four」によるひずみ解析では,THDは1%に増加しています.

「.Four」によるひずみ解析では,THDは1%に増加している.

▼図1(c)のソース・フォロア回路

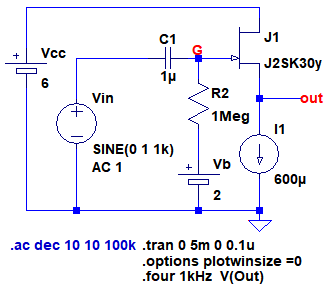

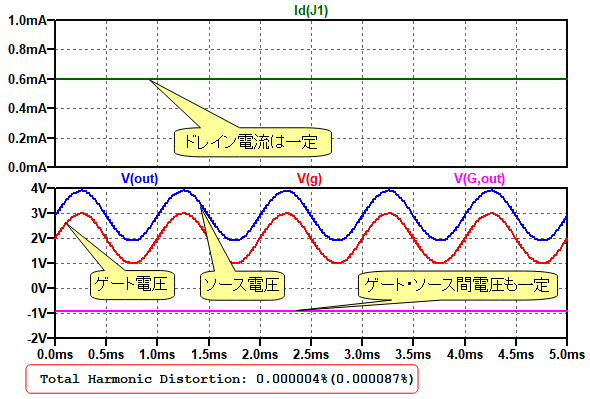

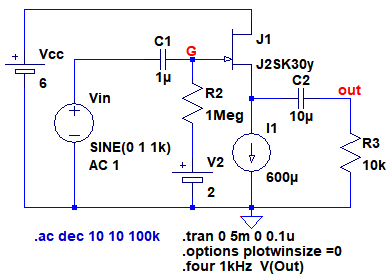

図8は,図1(c)のソース・フォロア回路をシミュレーションするための回路です.この回路では,ジャンクションFETの動作電流の設定は,定電流源(I1)で行っています.定電流源を使用することで,ソース端子の電圧が信号によって変化しても,ドレイン電流が変化することはありません.

ジャンクションFETの動作電流の設定は,定電流源(I1)で行っている.

図9は,図1(c)のソース・フォロア回路のシミュレーション結果です.ドレイン電流は一定で信号成分はありません.そのため,ゲート・ソース間電圧も一定となっています. そして,「.Four」によるひずみ解析では,THDは0.000004%となっており,ほとんどひずみが発生していないことが分かります.

「.Four」によるひずみ解析では,THDは0.000004%となっている.

▼図1(d)のソース・フォロア回路

図10は,図1(d)のソース・フォロア回路をシミュレーションするための回路です.この回路は図1(c)のソース・フォロア回路にC2とR3が追加されたものです.R3はソース・ホロア回路をバッファ・アンプとして使用する場合の,次段の入力インピーダンスに相当するものです.そのため,図8の回路よりも,より現実に近いシミュレーションができます.

図8の回路よりも,より現実に近いシミュレーションができる.

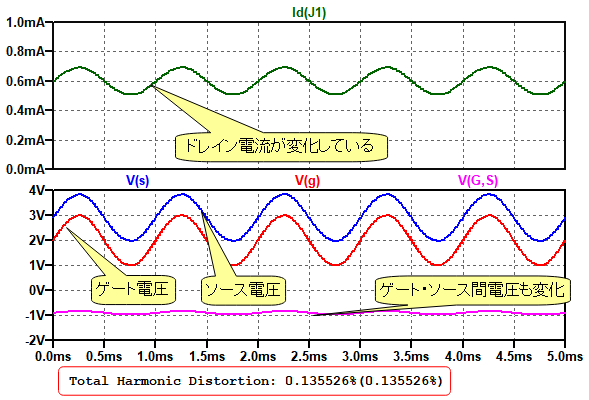

図11は,図1(d)のソース・フォロア回路のシミュレーション結果です.図9では一定だったドレイン電流が,入力信号によって変化していることが分かります.そのため,ゲート・ソース間電圧も若干変化しています.そして,「.Four」によるひずみ解析では,THDは0.14%と,図8の回路よりも増加しています.

「.Four」によるひずみ解析では,THDは0.14%と,図8の回路よりも増加している.

●ソース・フォロア回路のひずみを改善する

ここまでの解析で,図1の回路の中で最もTHDが小さいのは(c)の回路であることが分かりました.ただし,ソース・フォロア回路をバッファ・アンプとして使用する場合,かならず次段の入力インピーダンスが負荷として接続されます.そのため,(c)の回路は現実的ではありません.そこで,次段の入力インピーダンスが負荷として接続された場合も,THDを小さくできる回路を考えてみます.

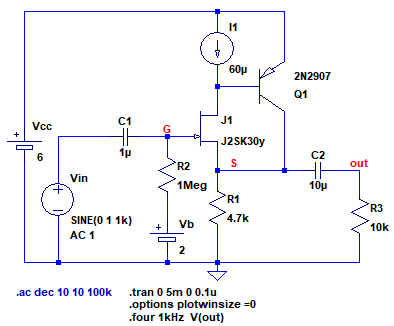

図12が,ソース・フォロア回路のひずみを改善した回路です.ジャンクションFETのドレインに,定電流源とPNPトランジスタ(Q1)のベースが接続されています.そして,Q1のコレクタがジャンクションFETのソースに接続されています.

信号電流はQ1が供給するため,ドレイン電流はほとんど変化しない.

このように接続することにより,信号電流はQ1が供給するようになり,ジャンクションFETのドレイン電流はほとんど変化しなくなります.その結果,ゲート・ソース電圧の変化も小さくなるため,ひずみを大幅に改善することができます.

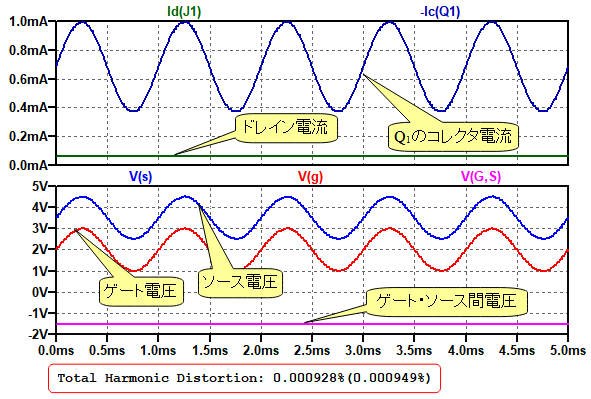

図13がひずみを改善したソース・ホロア回路のシミュレーション結果です.Q1のコレクタ電流は信号によって変化していますが,ジャンクションFETのドレイン電流は,ほとんど変化せず,一定になっています.その結果,ゲート・ソース電圧も一定になっています.そして,「.Four」によるひずみ解析では,THDは0.00095%となっており,ひずみが大幅に改善されていることが分かります.

「.Four」によるひずみ解析では,THDは0.00095%と大幅に改善されている.

以上,ジャンクションFETによるソース・フォロア回路について解説しました.図12の回路は,ひずみを大幅に改善することができますが,ドレイン電流が一定になるように,Q1で帰還をかけているため,回路が発振してしまうリスクがある点に注意が必要です.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice9_007.zip

●データ・ファイル内容

JFET_DC.asc:図2の回路

SF_A.asc:図4の回路

SF_A.plt:図5のグラフを描画するためのPlot settinngsファイル

SF_B.asc:図6の回路

SF_B.plt:図7のグラフを描画するためのPlot settinngsファイル

SF_C.asc:図8の回路

SF_C.plt:図9のグラフを描画するためのPlot settinngsファイル

SF_D.asc:図10の回路

SF_D.plt:図11のグラフを描画するためのPlot settinngsファイル

SF_LF.asc:図12の回路

SF_LF.plt:図13のグラフを描画するためのPlot settinngsファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs