静電シールドで外来雑音を防ぐ

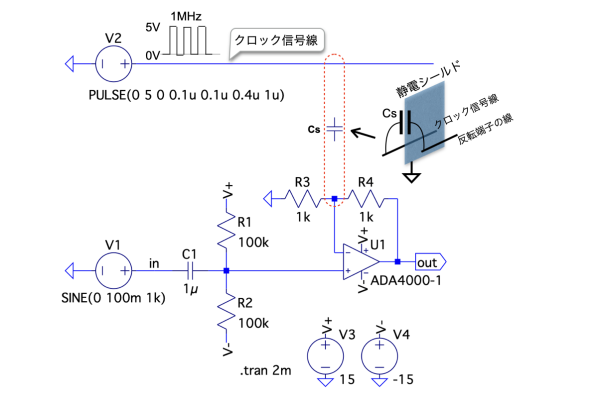

図1は,V1の信号をゲイン2倍の非反転アンプで増幅する回路の近くに,別の信号源(V2)を配置した図です.V2からは,振幅が5V,周波数が1MHzの矩形波のクロック信号が流れています.OPアンプ(U1)の反転端子とV2のクロック信号線の距離が近く,その間には0.1pFの浮遊容量(寄生容量:CS)があります.

この浮遊容量により,クロック信号が非反転アンプに悪影響を及ぼさないように,浮遊容量の間に図中で示すように静電シールドを入れました.図1において,静電シールドの効果として,正しいのは(a)~(d)のどれでしょうか.

静電シールドは金属の導体で,接続先のGNDはインピーダンスが低く,安定している.

(a) outにV2の信号は現れない

(b) outにV2の約1/100の振幅が現れる

(c) outにV2の約1/40の振幅が現れる

(d) outにV2の約1/10の振幅が現れる

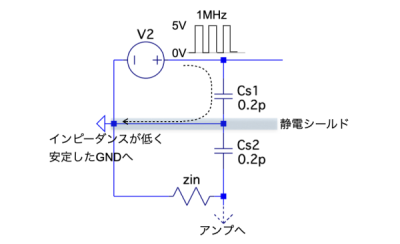

浮遊容量(Cs)の2つの電極の間に,金属の導体で,GNDに接続された,静電シールドがあるので,浮遊容量(Cs)は,静電シールドを境に2つに分けることができます.1つは,V2のクロック信号の配線と静電シールド間の浮遊容量で,もう1つは,OPアンプ側の静電シールド間の浮遊容量と反転端子に繋がる配線になります.このように考えたとき,V2のクロック信号は,2つの浮遊容量をどのように伝わるかを検討すると簡単に分かります.

図2は,図1の浮遊容量(Cs)付近で,2つの電極の間に静電シールドが有るときの等価回路です.静電シールドは,Csの2つの電極の中間にあると仮定しています.静電シールドが中間にあるので,図1のCsは,図2のように静電シールドを境にCs1とCs2の2つの浮遊容量にみなせます.図2のzinは,図1の浮遊容量側から非反転アンプ側をみたインピーダンスになります.

V2のクロック信号による電流は,Cs1を通りGNDへ流れ,Cs2側には流れない.

静電シールドが無い場合,V2のクロックの信号線とOPアンプの反転端子に繋がる配線は浮遊容量のCs1とCs2を介して静電結合になり,outにV2のクロック信号成分が現れます.

静電シールドが有る場合,V2のクロック信号による電流は,Cs1からGNDに流れ,Cs2側には流れません.この効果により,非反転アンプ側には伝わらないので,outにV2の信号は現れません.

●外来雑音について

回路システム全体の出力信号に干渉し,その出力信号に望ましくない変化を加えるものとして,外来雑音があります.外来雑音を大きく分けると次の2つになります.

・配線を伝わってくるもの

・空中を伝わってくるもの

さらに,空中を伝わってくる外来雑音を大きく分けると次の2つになります.

・電磁結合により回路に侵入するもの

・静電結合により侵入するもの

ここでは,静電結合を防ぐ静電シールドについて解説します.

●静電結合について

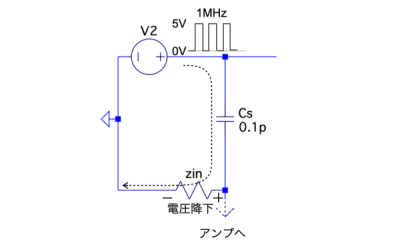

図3は外来雑音とみなしたV2の信号が静電結合によりアンプ側に侵入する様子を解説する図です.

静電結合は2つの配線間にある浮遊容量を介して,アンプ側へ侵入します.図3では外来雑音のV2による雑音電流が浮遊容量(Cs)を通り,アンプ側のインピーダンス(zin)に電圧降下を発生させます.この電圧降下がアンプ側に加わるのでoutにV2のクロック信号成分が現れます.

静電結合は浮遊容量(Cs)が大きくなる,あるいはアンプ側のインピーダンス(zin)が高くなると,outに現れる外来雑音は高くなります.具体的に,浮遊容量が大きくなるのは,配線間の距離が短いときや,同じ配線間の距離でも配線長が長いときです.また,アンプ側のインピーダンスは,回路定数や周波数特性に依存し,インピーダンス(zin)が高くなるときがあります.

このような外来雑音の侵入を防ぐのが静電シールドです.静電シールドは金属の導体を使い,浮遊容量の2つの電極とみなせる場所の間に入れてGNDに接続します.図1は,静電シールドによりCsを介した静電結合を防止する回路例で,浮遊容量は「Cs=0.1pF」としています.

●アンプ側のインピーダンスのシミュレーション

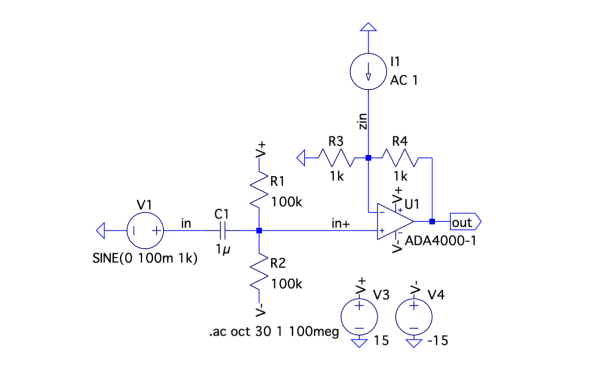

図4は,図1の浮遊容量側から非反転アンプ側をみたインピーダンスを調べる回路です.この回路を使って,zinのインピーダンスがどれくらいになるかを確かめます.

I1はテスト用の交流電流の信号源.

図4のI1は,シミュレーションでインピーダンスを調べるためのテスト用の交流電流の信号源です.このI1をOPアンプの反転端子に繋がる配線へ接続しています.シミュレーションは,AC解析を用います.I1の交流信号を加えたときzinの電圧変化をプロットすると「V(zin)/I(I1)」となるのでインピーダンスの周波数特性を調べることができます.ここで,I1の直流は「0A」にしているので回路の直流動作点に影響を与えません.

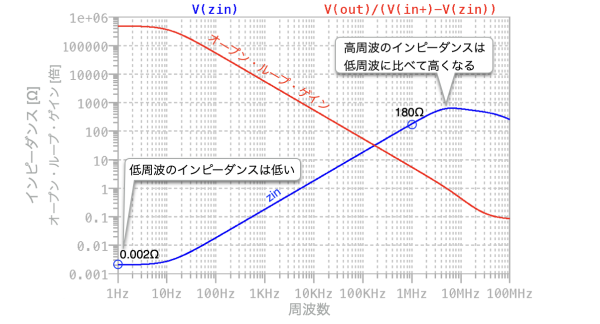

図5は,図4の回路で調べたインピーダンスのプロットになります.青のプロットがzinのインピーダンスです.また,赤のプロットは解説のためOPアンプのオープン・ループ・ゲインをプロットしました.zinは,低い周波数ではインピーダンスが低く,高い周波数ではインピーダンスが高くなります.この理由は,zinのインピーダンスは負帰還の効果により,OPアンプのオープン・ループ・ゲインが高いとzinのインピーダンスは低くなり,逆にオープン・ループ・ゲインが低いとzinのインピーダンスは高くなるからです.

クロック周波数の1MHzでは約180Ωになる.

図5に示したオープン・ループ・ゲインは,低い周波数でゲインが高く,1Hz付近のインピーダンスは約0.002Ωになります.逆に高い周波数ではオープン・ループ・ゲインが低く,V2のクロック周波数の1MHzでは約180Ωになります.インピーダンスは1Hzと1MHzのときと比べると9万倍も変化することが分かります.V2は1MHzの矩形波なので,静電シールドが無いときは1MHzの基本波成分とその高調波成分の電流が静電結合のCsを通ってzinの約180Ωで電圧になり,外来雑音のV2はアンプ側へ侵入します.

●静電シールドが無い場合

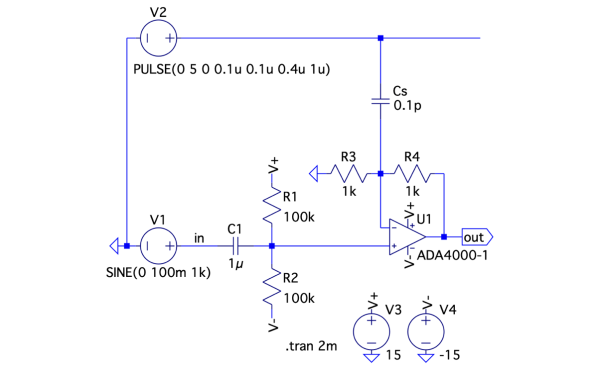

図6は,図1の静電シールドが無いとき,V2の信号成分が侵入してoutの波形がどうなるかを確認する回路になります.

図6のアンプは,V1の信号をゲインが2倍の非反転アンプで増幅してoutが出力になります.V1はオーディオの周波数帯を想定し,振幅が100mVで周波数が1kHzです.外来雑音を想定したV2は,振幅が5Vで周波数が1MHzの矩形波のクロック信号です.V2のクロックの信号線とOPアンプの反転端子に繋がる配線は0.1pFの浮遊容量(Cs)で静電結合しています.シミュレーションはtran解析を用いて,V1はinラベルでプロットします.また,非反転アンプの出力はoutのラベルでプロットします.

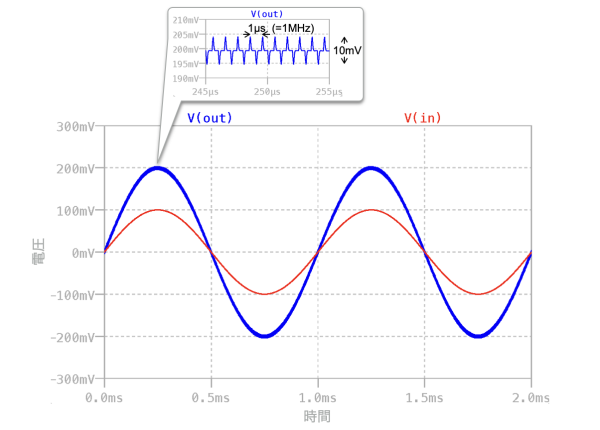

図7は,図6のシミュレーション結果です.outのプロットはinの2倍になります.outのプロットは線が太くなっており,拡大すると静電結合によりV2の外来雑音が侵入しているのが分かります.図7では,周波数が1MHzで雑音のピーク・ツー・ピークの振幅は10mVの雑音がoutに重畳された結果になります.

outの波形を拡大すると,V2の外来雑音が侵入している.

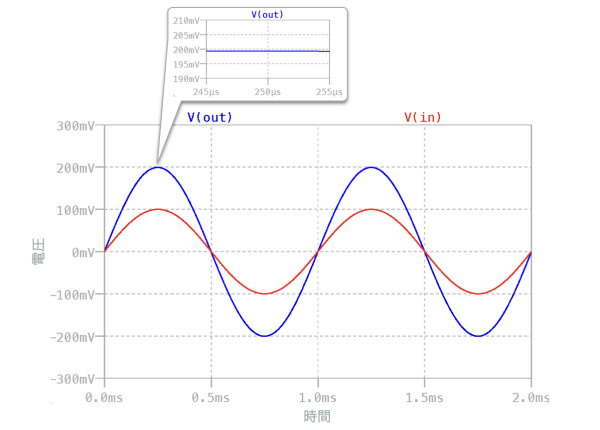

●静電シールドが有る場合

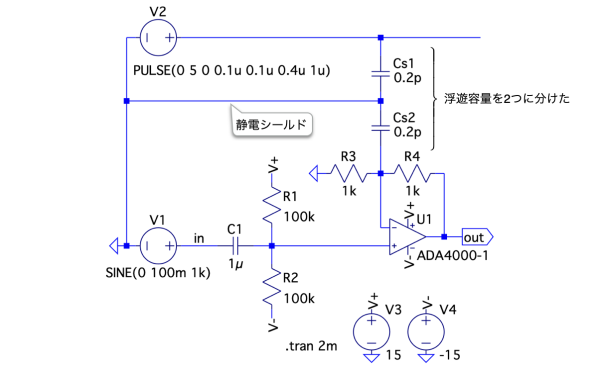

図8は,図1の浮遊容量の間に静電シールドが有るとき,outの波形がどうなるかを確認する回路になります.

静電シールドは,V2のクロック信号線とOPアンプの反転端子に繋がる配線の中間にあると仮定しています.この静電シールドにより,図1のCsは図8のCs1とCs2の2つの浮遊容量になります.静電シールドはGNDに接続しています.シミュレーション方法は図6と同じになります.

図9は,図8のシミュレーション結果です.outを拡大しても先程の図7のような外来雑音の侵入はありません.以上の検討より,図1の解答は(a)になるのが分かります.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice9_004.zip

●データ・ファイル内容

No shield zin.asc:図4の回路

No shield zin.plt:図4のプロットを指定するファイル

No shield.asc:図6の回路

No shield.plt:図6のプロットを指定するファイル

shield.asc:図8の回路

shield.plt:図8のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs

(11) ◆LTspiceで始める実用電子回路入門アーカイブs