CMOSで作るシュミット・トリガ回路

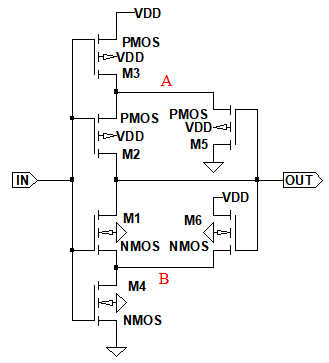

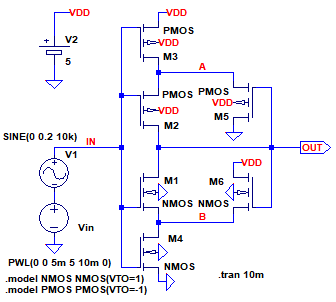

図1は,ある機能を持ったCMOS論理素子の,簡略化した内部回路図です.VDDには,5Vの電圧が加えられます.この論理素子の機能の説明として,最も適切なのは,(a)~(d)のどれでしょうか.

(a) しきい値電圧がVDD/2のバッファ

(b) しきい値電圧がVDD/2のインバータ

(c) しきい値電圧がヒステリシスを持ったバッファ

(d) しきい値電圧がヒステリシスを持ったインバータ

図1の回路の機能を考える場合,IN端子の電圧によって,OUT端子の電圧がどのように変わるかを考えます.このとき,A点の電圧と,B点の電圧が,OUT端子の電圧によってどのように変化するかということを,合わせて考える必要があります.

図1の回路は,IN端子の電圧がLowレベル("L"レベル)の0Vのとき,M2とM3がONするため,OUT端子はHighレベル("H"レベル)のVDDになります.IN端子の電圧が"H"レベル(VDD)のとき,M1とM4がONするため,OUT端子は"L"レベル(GND)になります.入力と出力の論理が反転するため,この回路はインバータとして動作します.

また,M5とM6は,ソース・フォロア回路として働き,OUT端子が"H"レベルのとき,B点の電圧を持ち上げます.また,OUT端子が"L"レベルのとき,A点の電圧を引き下げます.その結果,M1とM2がON/OFFするしきい値電圧が変化することになり,しきい値電圧にヒステリシス(履歴効果)が発生します.そのため,正解は(d)ということになります.

●CMOSインバータ回路の動作

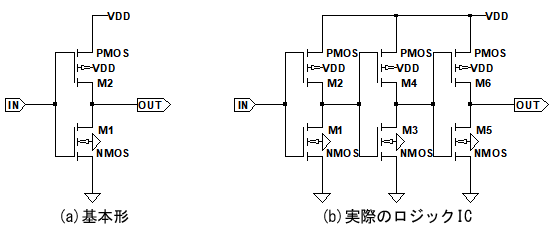

図1のCMOSシュミット・トリガ回路の動作を解説する前に,基本的なCMOSインバータ回路の動作を考えてみます.図2(a)が最も基本的なCMOSインバータ回路です.

IN端子の電圧が"H"レベルのとき,Nチャネル型MOS(NMOS)のM1がONし,Pチャネル型MOS(PMOS)のM2がOFFするため,OUT端子は"L"レベルになります.また,IN端子が"L"レベルのとき,M2がONし,M1がOFFするため,OUT端子は"H"レベルになります.このように,出力はIN端子の論理を反転したものになるため,インバータとして動作します.

入力電圧が「VDD/2」近辺のとき,M1とM2ともにONします.通常,このようなCMOSインバータ回路では,M1とM2に同じ大きさのゲート・ソース電圧を印加したとき,それぞれのON抵抗が等しくなるように,特性を設定します.すると,入力電圧が「VDD/2」になったとき,出力電圧が「VDD/2」となり,インバータとしてのしきい値電圧が「VDD/2」になります.実際のロジックICでは,図2(b)のように,図2(a)の回路を3段従属接続し,入力電圧の変化に対して,出力電圧がメリハリ良く変化するようにしています.

(a)が基本形で,実際のロジックICでは(b)のような回路となっている.

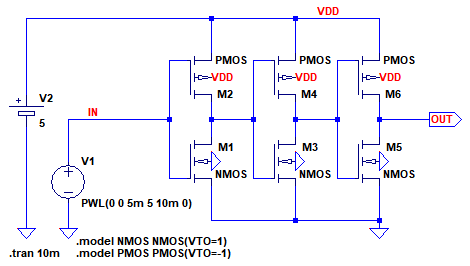

●CMOSインバータ回路をシミュレーションする

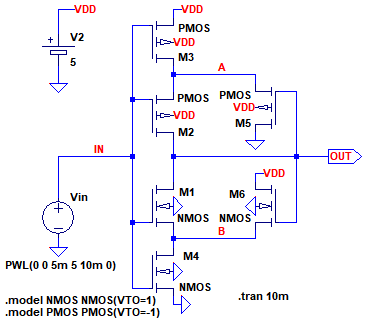

図3は,CMOSインバータ回路の入出力特性をシミュレーションする回路です.インバータは,図2(b)の回路となっています.「.modelコマンド」を使用して,MOSトランジスタのスレッショルド電圧が1Vとなるように,モデル・パラメータを設定しています.IN端子の電圧は,PWLを使用し,0Vから5Vまで変化させ,その後再び0Vになるようにしています.また,VDDには5Vの電圧が加わっています.

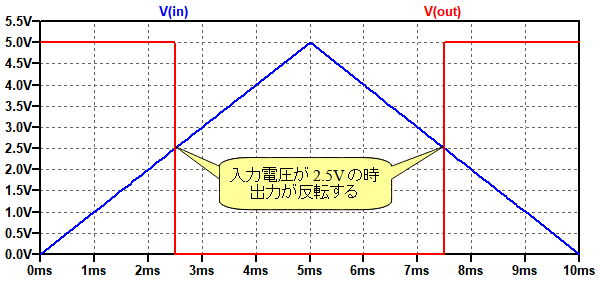

図4は,図3のシミュレーション結果です.入力電圧がVDDの半分の2.5Vになったときに,出力が反転していることが分かります.

入力電圧が2.5Vになったときに,出力が反転している.

●ノイズが混入した信号を入力したときの,CMOSインバータ回路の動作

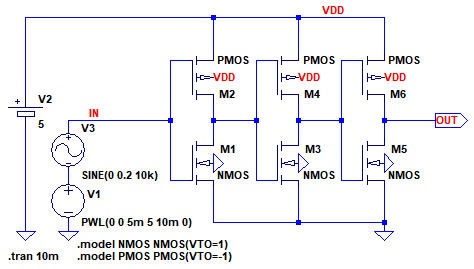

図5は,図3のインバータ回路に,ノイズが混入した信号を入力したときの,CMOSインバータ回路の動作をシミュレーションする回路です.どのような動作となるか確認してみます.図3の入力信号に,10kHzでピーク電圧0.2Vの正弦波信号を加えています.

図6は,図5のシミュレーション結果です.出力が反転するときに,何度も"H"レベルと"L"レベルを繰り返しています.このような信号を,カウンタに入力すると,意図したカウント数にならない等の不具合が発生してしまいます.このような現象を防止するには,しきい値電圧にヒステリシスを設ける必要があります.

出力が反転するときに,何度も"H"レベルと"L"レベルを繰り返している.

●CMOSシュミット・トリガ回路の動作をシミュレーションで確認する

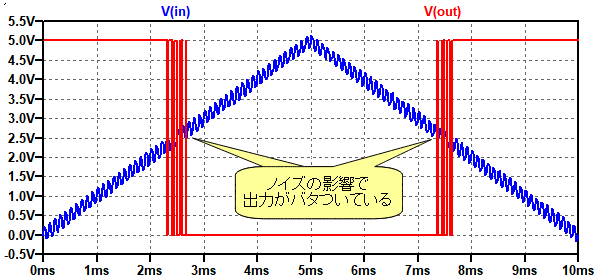

図7は,図1のCMOSシュミット・トリガ回路をシミュレーションする回路です.IN端子の電圧は,0Vから5Vまで変化し,その後再び0Vになるよう設定しています.

図8が,図7のシミュレーション結果です.シミュレーション結果を見ながら,図1の回路動作を解析します.

しきい値電圧にヒステリシス特性がある.

▼IN端子の電圧が"L"レベルから大きくなっていくときの動作

IN端子が0Vのとき,M2とM3がONし,M1とM4はOFFになるため,OUT端子は5Vとなります.M1とM4がOFFとなっているため,B点のインピーダンスは,非常に高くなっています.このとき,M6のゲートが5Vとなっていることから,B点の電圧は5VからM6のゲート・ソース電圧だけ低い,4Vとなっています.

IN端子の電圧が上昇していき,M4のスレッショルド電圧を越えると,M4がONします.M6がなければ,M4がONすることで,B点の電圧は0Vとなります.ところが,M6がソース・フォロア回路として動作するため,B点の電圧は,「OUT端子の電圧(5V)-M6のゲート・ソース電圧」に引き上げられます.

IN端子の電圧がさらに上昇し,M4のドレイン電流が増加すると,M6のゲート・ソース電圧が大きくなるため,B点の電圧は徐々に低下していきます.そして,IN端子の電圧が,「B点の電圧にM1のスレッショルド電圧を加えた値」を越えるとM1がONします.するとM1とM4が両方ともONすることになり,OUT端子の電圧が低下し,その結果B点の電圧も低下することで,M1のオン抵抗がさらに小さくなる,というループが発生し,OUT端子は急速にGNDレベルとなります.このように,M6でB点の電圧を引き上げることで,OUT端子が"H"レベルから"L"レベルになるしきい値電圧は,「VDD/2」よりも大きくなります.

▼IN端子の電圧が"H"レベルから小さくなっていくときの動作

IN端子の電圧が"H"レベルのとき,M1とM4がONし,M2とM3がOFFするため,OUT端子は0Vとなります.IN端子の電圧が下がっていき,M3のゲート・ソース電圧がスレッショルド電圧を越えると,M3がONします.M5がなければ,M3がONすることで,A点の電圧はVDDとなります.ところが,M5がソース・フォロア回路として動作するため,A点の電圧は「OUT端子の電圧(0V)+M5のゲート・ソース電圧」に引き下げられます.

IN端子の電圧がさらに下がり,M3のドレイン電流が増加すると,M5のゲート・ソース電圧が大きくなるため,A点の電圧は徐々に上昇していきます.そして,IN端子の電圧が「A点の電圧からM2のスレッショルド電圧を引いた値」よりも下がるとM2がONします.すると,M2とM3が両方ともONすることになり,OUT端子の電圧が上昇し,その結果A点の電圧も上昇することで,M2のオン抵抗がさらに小さくなる,というループが発生し,OUT端子は急速にVDDレベルとなります.このように,M5でA点の電圧を引き下げることで,OUT端子が"L"レベルから"H"レベルになるしきい値電圧は,「VDD/2」よりも小さくなります.

●ノイズが混入した信号を入力したときの,CMOSシュミット・トリガ回路の動作

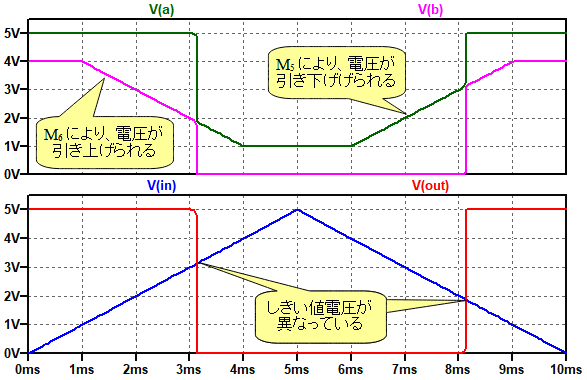

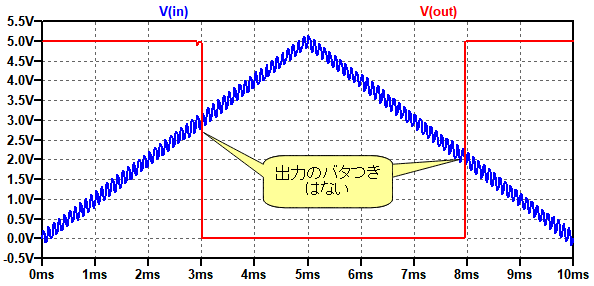

図9は,ノイズが混入した信号を入力したときの,CMOSシュミット・トリガ回路の動作をシミュレーションする回路です.図5と同様に,0Vから5Vまで変化する信号に,10kHzでピーク電圧0.2Vの正弦波信号を加えています.

図10は,図9のシミュレーション結果です.出力が切り替わる”しきい値電圧”にヒステリシスがあるため,一度出力が反転すると,多少入力電圧が変動しても再反転することはなく,きれいな出力信号が得られています.

ノイズによる出力のバタつきはない.

以上,CMOSシュミット・トリガ回路の動作について解説しました.このCMOSシュミット・トリガ回路は,LTspiceで始める実用電子回路入門 019で解説した「インバータで作るシュミット・トリガ回路」とは異なり,入力インピーダンスが高いため,出力抵抗の大きな信号源でも問題なく使用することができます.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice8_021.zip

●データ・ファイル内容

CMOS_INV.asc:図3の回路

CMOS_INV_N_VA.asc:図5の回路

CMOS_Schmitt_trigger.asc:図7の回路

CMOS_Schmitt_trigger_N.asc:図9の回路

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs