インバータで作るシュミット・トリガ回路

図1は,2つのCMOSインバータと2本の抵抗を使用したシュミット・トリガ回路です.IN端子に電圧を印加すると,その電圧値によってOUT端子がHighレベル("H"レベル)とLowレベル("L"レベル)に切り替わります.

シュミット・トリガ回路は,"H"レベルと"L"レベルに切り替わるしきい値電圧が,ヒステリシス(履歴効果)特性をもっています.そのしきい値電圧の組み合わせ(表1)として正しいのは,(a)~(d)のどれでしょうか.ただし,CMOSインバータの電源電圧は5Vとします.

この回路のしきい値電圧は?

| "H"レベルとなるしきい値電圧 | "L"レベルとなるしきい値電圧 | |

| (a) | 2.5V | 2.0V |

| (b) | 3.0V | 2.5V |

| (c) | 3.0V | 2.0V |

| (d) | 3.3V | 1.7V |

(a)の組み合わせ (b)の組み合わせ (c)の組み合わせ (d)の組み合わせ

CMOSインバータ単体のしきい値電圧は,電源電圧の1/2になります.IN端子に加えられる電圧が変化したときに,CMOSインバータの入力端子の電圧がどのように変化するかを考えれば,答えが分かります.

図1の回路のしきい値電圧は,電源電圧とR1,R2の値から計算することができます."H"レベルとなるしきい値電圧(VINH)は「VINH=5*(R1+R2)/(2*R2)=5*(33k+100k)/200k≒3.3V」となり,"L"レベルとなるしきい値電圧(VINL)は「VINL=5*(R2-R1)/(2*R2)=5*(100k-33k)/200k≒1.7V」となります.したがって正解は,(d)の組み合わせということになります.

●インバータ回路の動作

インバータは,入力の論理を反転するものです.入力が"L"レベルのとき,出力は"H"レベルになり,逆に,入力が"H"レベルのとき,出力が"L"レベルになります.

図2は,LTspiceに内蔵されているインバータ素子(INV)をシミュレーションする回路です.Valueの欄に「Vhigh=5」と記入すると,"H"レベルのときの出力電圧が5Vとなり,CMOSインバータを電源電圧5Vで使用したときと等価な動作になります.ここでは,IN端子の電圧を0Vから5Vまで変化させ,ふたたび0Vに変化させます.

図3は,図2のインバータ素子(INV)のシミュレーション結果です.入力電圧が2.5Vになったときに,出力が反転していることが分かります.OUT2は,OUT1の出力結果を反転したものになっています.

入力電圧が2.5Vになったときに,出力が反転している.

●ノイズが混入した信号を入力した場合のインバータ回路の動作

図2の回路で,ゆっくりと変化する信号にノイズが混入したとき,どのような動作となるか,シミュレーションで確認してみます.図4は,ノイズが混入した場合の信号を入力したときの,インバータの動作をシミュレーションする回路です.図2の入力信号に,10kHzでピーク電圧0.2Vの正弦波信号(V2)を加えています.

図5は,図4のシミュレーション結果です.出力が反転するときに,何度も"H"レベルと"L"レベルを繰り返しています.このような信号を,カウンタに入力すると,意図したカウント数にならないなどの不具合が発生してしまいます.

出力が反転するときに,何度も"H"レベルと"L"レベルを繰り返している.

●インバータ回路と抵抗を組み合わせたシュミット・トリガ回路

図5のような現象を防ぐため,しきい値電圧にヒステリシスを持たせた,シュミット・トリガ回路というものがあります.図1が2つのインバータと2本の抵抗を使用したシュミット・トリガ回路です.2つのインバータは,1つのバッファに置き換えても同じ動作になります.

図6は,インバータ回路と抵抗を組み合わせたシュミット・トリガ回路をシミュレーションする回路図です.この回路図を使用して,しきい値電圧がいくつになるか計算してみます.ここでは汎用的に使用できる式とするため,ロジック回路の出力振幅をVddとして計算します.

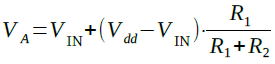

IN端子の電圧をVINとし,OUT端子の電圧をVOUTとすると,A点の電圧(VA)は式1で計算することができます.

・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・(1)

最初に,IN端子の電圧が0Vから大きくなっていく場合を考えます.IN端子の電圧が0Vの場合,A点の電圧も0Vになり,B点はVddでOUTは0Vになります.A点の電圧が「Vdd/2」以下の場合,OUT端子は0Vを維持します.式1で「VOUT=0」とすると,式2になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

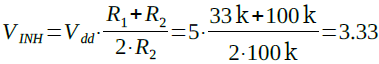

IN端子の電圧が上昇して,A点の電圧が「Vdd/2」となるIN端子の電圧(VINH)を,式2を使用して求めると式3になり,Vddが5Vの場合,3.33Vになります.

・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・(3)

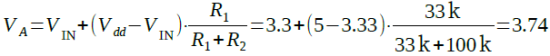

IN端子の電圧が3.33Vを少しでも越えると,OUT端子が0VからVddに切り替わります.すると,A点の電圧が急激に上昇し,式4のように3.74になります.

・・・・(4)

・・・・(4)

この状態になると.IN端子の電圧が多少小さくなってもOUT端子は変化しません.

次にIN端子の電圧が小さくなっていった場合を考えます.A点の電圧がVdd/2以上なので,OUT端子の電圧はVddとなっています.このとき,IN端子の電圧とA点の電圧の関係は式5で表されます.

・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・(5)

IN端子の電圧が下降していきA点の電圧がVdd/2となるIN端子の電圧(VINL)を,式5を使用して求めると式6になります.

・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・(6)

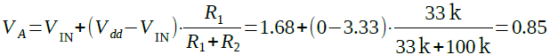

今度は,IN端子の電圧が1.68Vより少しでも小さくなると,OUT端子は0Vになります.するとA点の電圧が急激に低下し,式7のように0.85Vになります.

・・・・(7)

・・・・(7)

この状態になると,IN端子の電圧がふたたび3.33Vを越えるまで,OUT端子の状態は変化しません.つまり,図6の回路の"H"レベルとなるしきい値電圧が約3.3Vで,"L"レベルとなるしきい値電圧が約1.7Vになります.

●計算結果とシミュレーション結果の確認

図7は,図6のシミュレーション結果です."H"レベルとなるしきい値電圧が3.3Vで,"L"レベルとなるしきい値電圧が1.7Vとなっており,式3,式6で計算した値と一致しています.

しきい値電圧は式3,式6で計算した値と一致している.

●ノイズが混入した場合のシュミット・トリガ回路の動作を確認する

図8は,図6にノイズが混入した場合のシュミット・トリガ回路の動作をシミュレーションする回路です.図4と同様に,入力信号に,10kHzでピーク電圧0.2Vの正弦波信号(V3)を加えています.

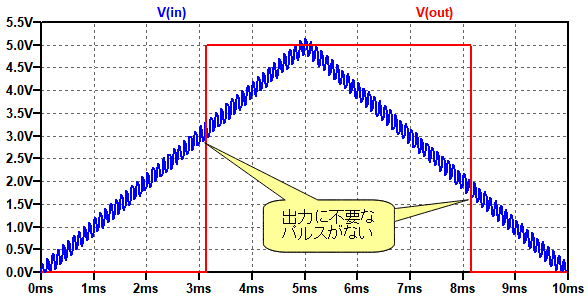

図9は,ノイズが混入した場合のシュミット・トリガ回路のシミュレーション結果です.図5とは異なり,出力に不要なパルスがありません.これは,しきい値にヒステリシスがあるため,小さなノイズがあっても出力が反転してしまうことがないためです.

出力に不要なパルスがない.

以上,CMOSインバータと2本の抵抗を使用したシュミット・トリガ回路を紹介しました.この回路は,抵抗で帰還をかけているため,入力として,出力抵抗の大きな信号源を接続すると,所望の特性が得られないことに注意が必要です.

また,オペアンプを使用したシュミット・トリガ回路については,「ヒステリシス・コンパレータのしきい値を2Vと3Vにする抵抗値は?」,「ヒステリシス・コンパレータのしきい値」を参照してください.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice8_019.zip

●データ・ファイル内容

INV_DCIN.asc:図2の回路

INV_DCIN.plt:図3のグラフを描画するPlot settinngsファイル

INV_DC_N_IN.asc:図4の回路

INV_DC_N_IN.plt:図5のグラフを描画するPlot settinngsファイル

INV_R_Schmitt_DC.asc:図6の回路

INV_R_Schmitt_DC.plt:図7のグラフを描画するPlot settinngsファイル

INV_R_Schmitt_DC_N.asc:図8の回路

INV_R_Schmitt_DC_N.plt:図9のグラフを描画するPlot settinngsファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs