4倍の出力電力が得られるフィルタレスD級アンプ

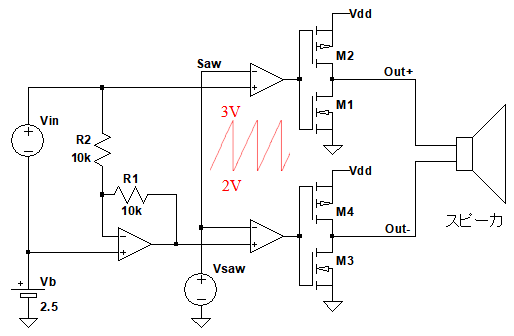

図1は,通常のオーディオ用D級パワーアンプより,フィルタレスで部品点数が少なく,2つの出力によるブリッジ出力で,1つの出力アンプに比べ,4倍の出力電力が得られるD級パワーアンプの簡易ブロック図です.

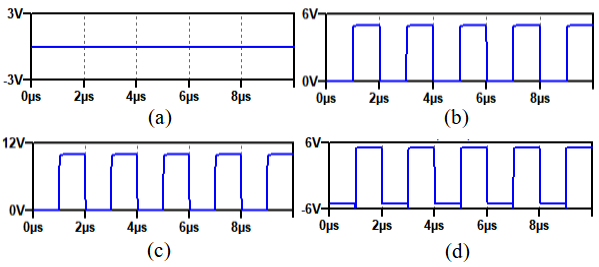

Vinが入力信号で,コンパレータの-端子(Saw)には,振幅1V(最低電圧2V,最大電圧3V)で500kHzの「のこぎり波」が加えられています.2つのコンパレータの出力には,MOSトランジスタによるインバータが接続され,Vddに5Vの直流電圧が印加されています.インバータの出力(Out+,Out-)にスピーカが接続されていますが,入力信号が0Vのとき,このスピーカに印加される電圧波形は,図2の(a)~(d)のどれでしょうか.

(a)の波形 (b)の波形 (c)の波形 (d)の波形

図1の回路は,出力段のLCフィルタが省略可能で電力効率の良い,フィルタレス・ブリッジ出力型D級パワーアンプと呼ばれるものです.入力信号が0Vのとき,それぞれのコンパレータ出力がどのような波形になるかを考えれば,答えは簡単に分かります.

入力信号が0Vのとき,それぞれのコンパレータ出力は,全く同じ500kHzの矩形波になります.そして,Out+とOut-の波形も同じ500kHzの矩形波になります.Out+とOut-の波形が同じなので,その差電圧は0Vです.そのため,正解は(a)の波形となります.

図1の回路は,無信号時に,スピーカにスイッチング信号が印加されないため,通常のD級パワーアンプでは必要な,LCフィルタを省略できます.そのため,フィルタレスと呼ばれます.

●基本的なD級パワーアンプ

D級パワーアンプは,PWMパワーアンプとも呼ばれ,通常のアンプに比べてアンプの損失電力が小さく,効率が良いという特長があります.効率が良いことから,ポータブル機器では,バッテリ駆動時間を長くすることが可能です.また,大電力アンプでは発熱が少ないことから,小型化が可能になります.

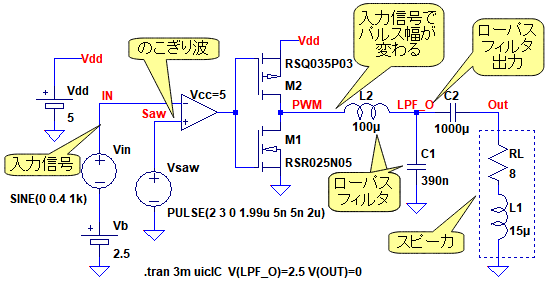

図3は,最も基本的なD級パワーアンプをシミュレーションするための回路です.入力信号とのこぎり波をコンパレータで比較することで,コンパレータ出力は,入力信号によってパルス幅の変わる矩形波になります.コンパレータ出力はMOSトランジスタによるインバータにより,低出力インピーダンスのPWM出力となります.L2とC1によるローパス・フィルタは,PWM出力の高周波信号を取り除くためのものです.

また,ローパス・フィルタ出力は,1/2Vddを中心とした信号となるため,直流成分を取り除くために大容量のカップリング・コンデンサ(C2)も必要になります.入力信号はピーク電圧0.4Vで1kHzの正弦波です.なお,使用しているコンパレータは,内部回路を電圧制御電圧で構成しており,Vccという変数で電源電圧を指定できるようにしています.

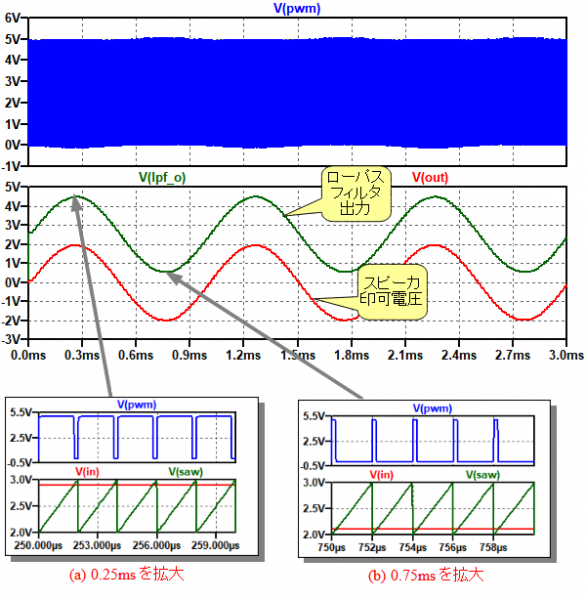

図4は,図3のシミュレーション結果です.上段がPWM出力で,下段がローパス・フィルタ出力[V(LPF_O)]とスピーカ印加電圧[V(Out)]を表示しています.スピーカ印加電圧は,ピーク電圧2Vの正弦波となっており,入力信号のピーク電圧が0.4Vなので,ゲイン5倍のパワーアンプとして動作していることが分かります.

スピーカ印加電圧はピーク電圧2Vの正弦波となっている.

また,(a)と(b)に,時間軸を拡大した,PWM出力と+端子電圧(Saw),入力端子電圧[V(in)]の波形も表示しています.(a)は入力信号が上側に振れた0.25ms部分を拡大したものです.また,(b)は入力電圧が下側に振れた,0.75ms部分を拡大したものです.(a)の入力信号波形が上側に振れているとき,パルス幅が大きく,(b)の入力信号波形が下側に振れているとき,パルス幅が小さくなっています.

●最大電力を4倍とするD級パワーアンプ

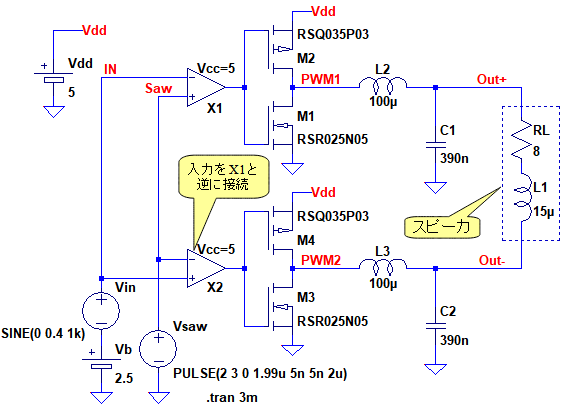

図5は,ブリッジ出力型D級パワーアンプをシミュレーションするための回路です.図3の通常のD級パワーアンプは,直流成分をカットするために大容量のコンデンサが必要でした.しかし,図5のブリッジ出力型D級パワーアンプとすることで,このコンデンサを省略できます.また,ブリッジ出力型D級パワーアンプは,同じ電源電圧で,図3の通常のD級パワーアンプの2倍の電圧出力が得られ,スピーカで発生する最大電力を4倍とすることができます.

コンパレータ(X2)の入力端子の接続は,コンパレータ(X1)とは逆になっている.

図3と同様な回路を2組使用し,それぞれの出力(Out+とOut-)にスピーカを接続しています.無信号時のOut+とOut-の直流電圧は等しいため,スピーカを直結することが可能です.下側の回路のコンパレータ(X2)の入力端子の接続は,上側の回路のコンパレータ(X1)とは逆になっています.接続を逆にすることで,Out-端子のオーディオ出力の位相が,Out+端子とは逆位相となり,スピーカに印加される電圧が,図3の回路の2倍になります.

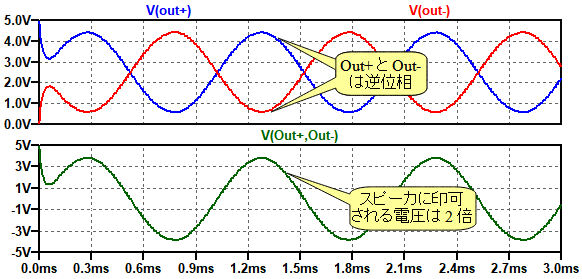

図6は,図5のシミュレーション結果です.Out+端子とOut-端子のオーディオ出力は,逆位相となっています.そのため,スピーカに印加される電圧(Out+とOut-の差電圧)は,Out+端子とOut-端子それぞれの出力電圧の2倍になっています.消費電力は,電圧の2乗に比例するため,スピーカで発生する電力は,図3の回路の4倍になります.

Out+端子とOut-端子のオーディオ出力は逆位相となっている.

図7は,図5の入力信号が0Vのとき,PWM1端子とPWM2端子の波形の時間軸を拡大したものです.のこぎり波の周波数と同じ500kHzの矩形波となっています.インバータ出力のPWM1とPWM2の出力電圧は,互いに逆位相となっていることが分かります.そのため,PWM1端子とPWM2端子に直接スピーカを接続すると,2倍の振幅の500kHzの矩形波がスピーカに加わることになります.そこで,矩形波がスピーカに加わらないようにするには,それぞれの出力に,LCローパス・フィルタを入れる必要があります.

PWM1とPWM2の出力電圧は,互いに逆位相となっている.

●LCフィルタを省略できるD級パワーアンプ

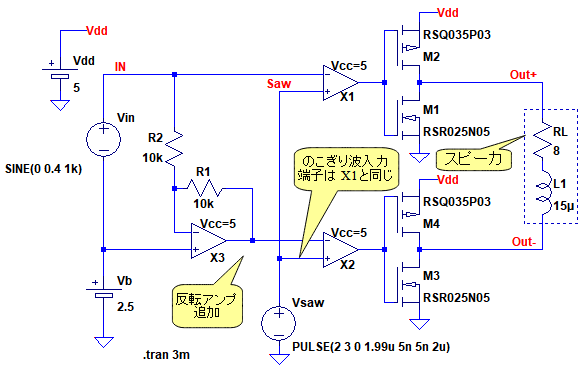

図8は,図1のフィルタレス・ブリッジ出力型D級パワーアンプをシミュレーションするための回路です.図8は,図5の回路で必要だった出力LCフィルタを省略するために考えられました.

ゲイン1の反転アンプが追加されている.

図8は,図5の回路とは異なり,のこぎり波信号は,コンパレータ(X1),コンパレータ(X2)ともに+入力端子に入力されています.オペアンプ(X3)によるゲイン1の反転アンプが追加されており,その出力はコンパレータ(X2)の-入力端子に接続されています.

このように接続すると,入力信号が0Vのとき,コンパレータ(X1)とコンパレータ(X2)の出力は全く同じ500khzの矩形波になります.Out+端子とOut-端子の信号も全く同じになるため,スピーカに印加されるOut+とOut-の差電圧は0Vとなります.そのため,無信号時に関してはLCローパスフィルタは省略しても全く問題ありません.ただし,信号を入力した場合は,500kHzの矩形波信号がスピーカに印加されることになります.しかし,スピーカのインダクタンスにより,高周波電流が小さくなるため,用途によってLCローパスフィルタを省略することができます.

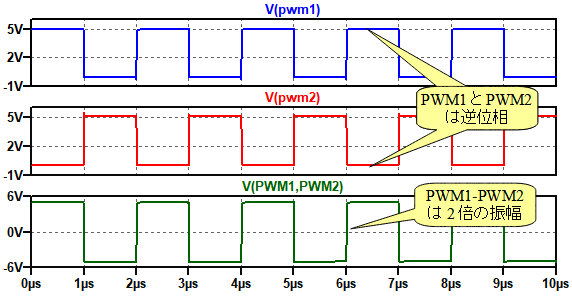

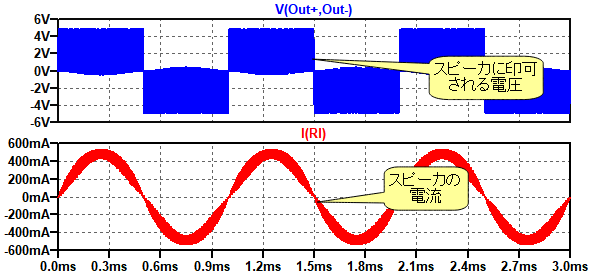

図9は,図8のシミュレーション結果です.上段がスピーカに印加されている電圧波形で,下段がスピーカに流れる電流波形です.

スピーカに流れる電流は高周波電流が少なく,オーディオ信号が主体となっている.

スピーカに印加される電圧(Out+とOut-の差電圧)は,オーディオ信号が+の場合は+5Vで,オーディオ信号が-の場合は-5Vとなっています.スピーカに流れる電流は,スピーカのインダクタンスの効果で高周波電流が少なく,オーディオ信号が主体となっています.

●入力信号のレベルごとに波形を確認する

入力信号のレベル(入力信号が0V,上側に振れたとき,下側に振れたとき)ごとに,Out+とOut-および,スピーカ印加電圧[V(Out+,Out-)]の波形がどのようになっているかを確認するため,時間軸を拡大したものが,図10から図12になります.

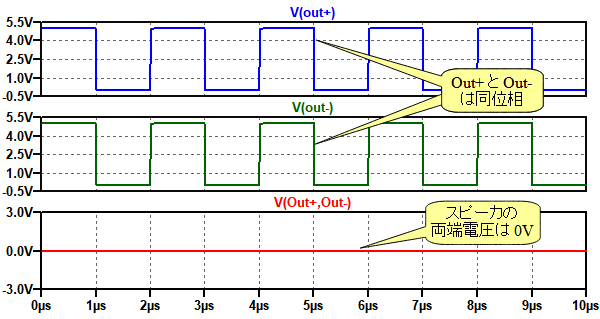

図10は,入力信号が0VのときのOut+,Out-,スピーカ印加電圧の波形です.入力信号が0のときは,スピーカの両端電圧も0Vとなっていることが分かります.

入力信号が0のときは,スピーカの両端電圧も0Vとなっている.

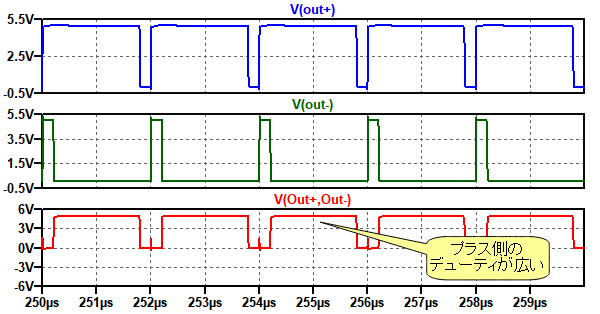

図11は,入力信号が上側に振れたとき(0.25ms部分)のOut+,Out-,スピーカ印加電圧の波形です.スピーカ印加電圧は,+側のデューティが広い,振幅5Vの矩形波になっています.

スピーカ印加電圧は+側のデューティが広い,振幅5Vの矩形波

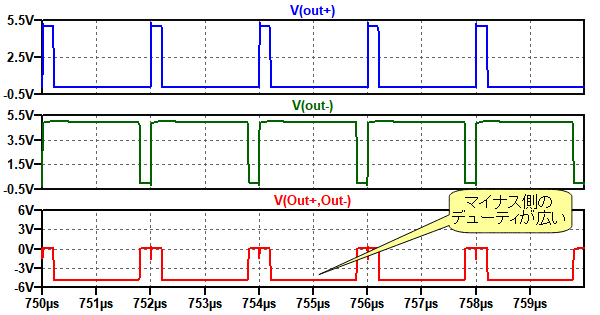

図12は,入力信号が下側に振れたとき(0.75ms部分)のOut+,Out-,スピーカ印加電圧の波形です.スピーカ印加電圧は,-側のデューティが広い,振幅5Vの矩形波になっています.

スピーカ印加電圧は-側のデューティが広い,振幅5Vの矩形波

以上,フィルタレス・ブリッジ出力型D級パワーアンプの動作について解説しました.フィルタレスという名前になっていますが,無信号時以外は高周波信号がスピーカに印加されるため,スピーカ・ケーブルが長い場合や出力電圧が大きい場合は,LCフィルタ等を追加する必要があります.また,実際のフィルタレス・ブリッジ出力型D級パワーアンプICでは,出力の貫通電流防止回路やひずみ低減回路など,さまざまな改善回路が追加されています.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice8_014.zip

●データ・ファイル内容

PWM_PW.asc:図3の回路

LimitAmp.asy:コンパレータのシンボル

LimitAMP.asc:コンパレータの内部回路

PWM_PW_BG.asc:図5の回路

FL_PWM_PW.asc:図8の回路

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs