PCバス・データ転送の基礎知識

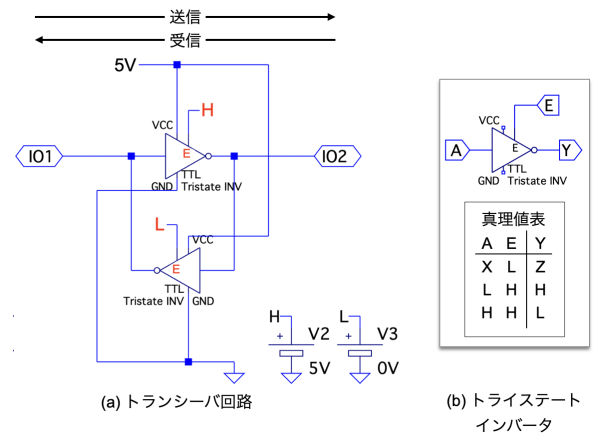

図1(a)は,出力が"H","L","Z"(切断)の3つの状態を持つTTLのトライステート・インバータを使った,ディジタル信号のトランシーバ回路です.

トランシーバ回路は,トライステート・インバータのE端子の論理レベル[図1(b)]により,図1(a)のIO1とIO2間でディジタル信号の送信と受信の状態が変わります.

図1(a)の上側のトライステート・インバータのE(Enable)端子は"H",下側のトライステート・インバータのE端子は"L"のとき,送信と受信の正しい状態は,(a)~(d)のどれでしょうか.ここで,トライステート・インバータの真理値表は図1(b)になります.

(a) トランシーバ回路

(b) トライステート・インバータの真理値表

"L"はLow論理レベルを示す.

"H"はHigh論理レベルを示す.

"X"は"L"レベルまたは"H"レベルのいずれかを示す.

"Z"はハイ・インピーダンスを示す.

(a) IO1からIO2へディジタル信号を送信する

(b) IO2からIO1へディジタル信号を受信する

(c) IO1とIO2のディジタル信号を同時に送受信する

(d) IO1とIO2のディジタル信号の送受信を停止する

図1(a)では,IO1からIO2にディジタル信号を送信,IO2からIO1にディジタル信号を受信します.図1(b)の真理値表を元に,図1(a)のディジタル信号の伝わり方を調べると分かります.出力(Y)が"Z"のハイ・インピーダンスになると,電気的にどのように見えるかがヒントです.

図1(b)の真理値表より,トライステート・インバータは,E端子の論理レベルが"L"なると,出力は"Z"のハイ・インピーダンスになります.ハイ・インピーダンスになると,出力(Y)は,"H","L"のどちらでもない,回路から電気的に切断された状態になります.

図1(a)でハイ・インピーダンスになるのは,E端子の論理レベルが"L"となる下側のトライステート・インバータなので,IO2からIO1へディジタル信号を受信しません.上側のトライステート・インバータのE端子は"H"なので,図1(b)の真理値表よりインバータとして動作し,IO1からIO2へディジタル信号を送信します.以上の検討より,(a) IO1からIO2へディジタル信号を送信するが正解になります.

●出力(Y)が3つの状態になるトライステート・インバータ

図1(a)で使っているトライステート・インバータは,入力(A)とE端子の論理レベルにより,出力(Y)が3つの状態になることから,このように呼ばれます.出力(Y)の3つの状態は,図1(b)の真理値表のように,"H"レベル,"L"レベル,"Z"(ハイ・インピーダンス)になります.ハイ・インピーダンスは,ディジタル信号の論理レベルではなく,出力(Y)は電源とGNDのどちらとも接続されず,回路から電気的に切断された状態を表しています.

●バスへのデータ転送に使われるトライステート・インバータ

トライステート・インバータの出力をハイ・インピーダンスにすると,回路から切り離されて,ディジタル信号を転送しない状態を作れます.これを利用して,コンピュータ・システムのバス(データをやり取りする共有した信号線)にデータを転送するときの経路の選択に使われています.

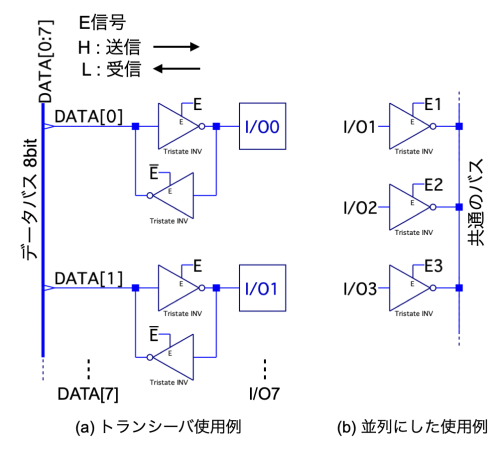

トライステート・インバータの使用例として,図2(a)のトランシーバと図2(b)の並列にした使用例があります.

(a) データ・バスとI/Oデバイス間のディジタル信号を送受信するトランシーバ使用例

(b) 並列に接続して,共通のバスにディジタル信号を転送する使用例

図2(a)は,図1(a)をデータ・バスの数だけ用いた例です.8bitのデータ・バスから8個のI/Oデバイスへディジタル信号を送受信するとき,E端子の論理レベルで送信と受信の方向を変えてデータ転送しています.

次に図2(b)は,1つの共通のバスへデータ転送する例で,I/O1が送信するときは,他はハイ・インピーダンスになるようにE1~E3の論理レベルで制御します.このようにハイ・インピーダンスの状態を使って,データ転送する方向や経路を制御する目的で使われています.

●トライステート・インバータの回路動作

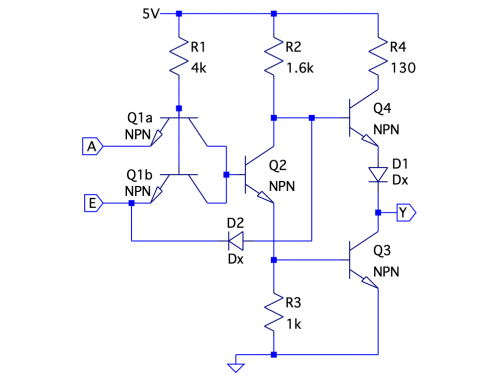

図3は,TTLのトライステート・インバータ回路で,入力(A),出力(Y),ハイ・インピーダンスの制御はE端子になります.ここで,図3の回路について,出力(Y)がインバータとして動作するときと,ハイ・インピーダンスになるときの回路動作について解説します.

"H"レベルは5V,"L"レベルは0Vとする.

●インバータとして動作するときの回路動作

図3のE端子が"H"レベルの5Vのとき,D2に逆バイアス電圧がかかり,ダイオードがOFFになって,E端子とQ4ベースの接続は,切り離された状態になります.このとき,入力(A)が"H"レベルの5VになるとQ2とQ3がONし,Q4がOFFになって,出力(Y)は"L"レベルの0Vに近い電圧になります.

逆に入力(A)が"L"レベルの0VになるとQ2とQ3がOFFし,Q4がONになって,出力(Y)は"H"レベルの5Vに近い電圧になります.

このようにE端子が"H"レベルの5Vのときは,入力(A)のディジタル信号を反転して,出力(Y)に伝えるインバータになります.

●出力がハイ・インピーダンスになるときの回路動作

図3のE端子が"L"レベルの0VのときはD2がON,また,Q2がOFFの2つの状態になります.

先ずD2がONになると,入力(A)の論理レベルに関係なくQ4ベース電圧は約0.7Vで固定されます.Q4がONになるベース電圧は約4V以上であり,その電圧より低い0.7Vの電圧で固定されるので,Q4はOFFになります.

次にQ2がOFFになると入力(A)の論理レベルに関係なくQ3はOFFになります.

このようにE端子が"L"レベルの0Vのときは,出力(Y)につながるQ3とQ4の両方がOFFになります.このときの出力(Y)は,Q3とQ4の両方がOFFなので,電源の5VとGNDのどちらとも接続されず,回路から電気的に切断されたハイ・インピーダンスの状態になります.

●トライステート・インバータの動作をシミュレーション

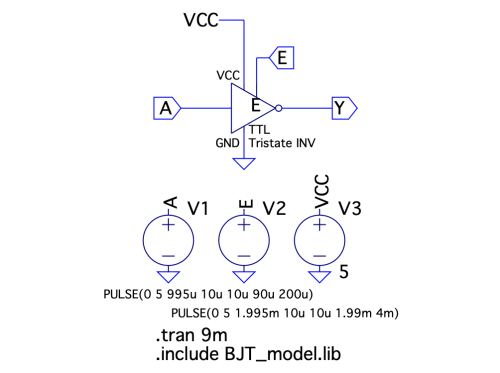

図4はトライステート・インバータの真理値をシミュレーションで確認する回路です.トライステート・インバータはサブ・サーキット化しており,図4のシンボルの中身は図3になります.図4では入力(A)に"H"論理レベルが5V,"L"レベルが0Vのディジタル信号を加え,E端子の論理レベルの変化で出力(Y)の真理値をトランジェント解析で調べます. 図3のトライステート・インバータはバイポーラ・トランジスタを用いているので,そのモデル・パラメータが入ったライブラリ・ファイル「BJT_model.lib」を読み込んでいます.

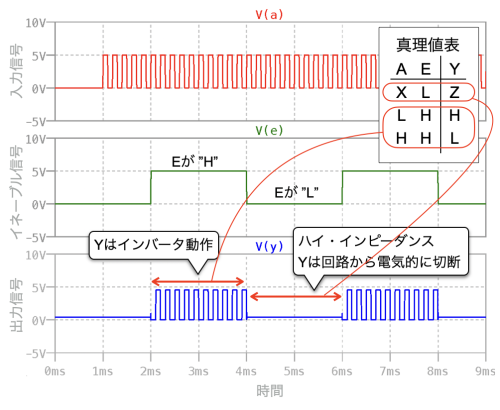

図5は図4のトランジェント解析の結果で,上段は入力(A)の入力信号,中段はE端子の制御信号,下段は出力(Y)の出力信号をプロットしました.図4には分かりやすいように,真理値表とコメントを記入しています.

上段は入力(A)の入力信号,中段はE端子の制御信号,下段は出力(Y)の出力信号.

図5より,E端子が"H"のときは,出力(Y)は入力(A)を反転した信号になり,インバータとして動作します.E端子が"L"のときは,入力(A)に関係なく出力(Y)はハイ・インピーダンスになり,回路から電気的に切断された状態なので,入力(A)のディジタル信号は伝わりません.このように真理値表の動作と同じになるのが確認できます.

●トランシーバ使用例のシミュレーション

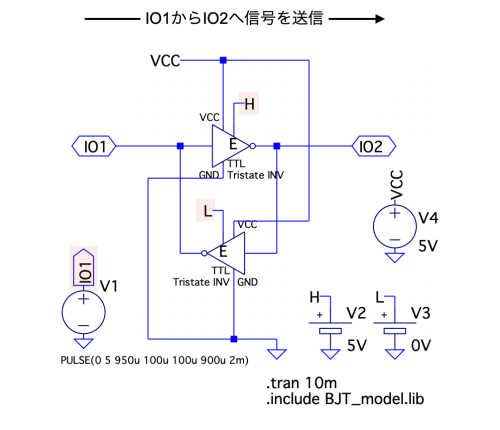

図1(a)のディジタル回路で使うトランシーバ回路の動作をシミュレーションで確認します.図6は図1(a)のトランシーバと同じ回路で,上側のトライステート・インバータのE端子は"H"レベルでインバータ動作になる状態,下側のトライステート・インバータのE端子は"L"レベルでハイ・インピーダンスの状態をシミュレーションします.データの転送はIO1からIO2の送信になるので,V1のディジタル信号はIO1側へ接続しています.

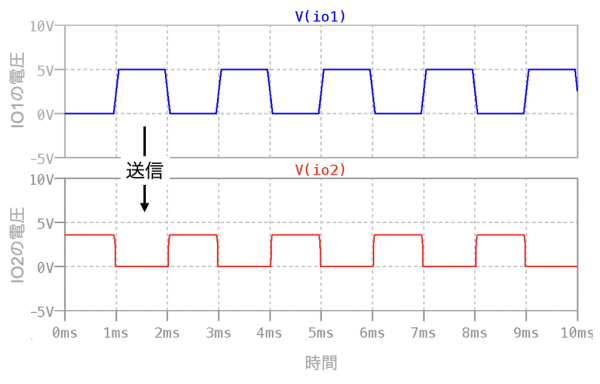

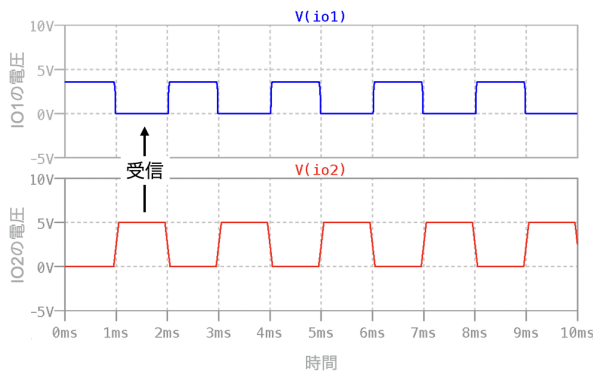

図7は図6のIO1とIO2をプロットしました.IO1はV1のディジタル信号になり,IO2は上側のトライステート・インバータで送信したディジタル信号になります.このように解答「(a) IO1からIO2へディジタル信号を送信する」がシミュレーションでも確認できます.

IO1(上段)からIO2(下段)へディジタル信号を送信している.

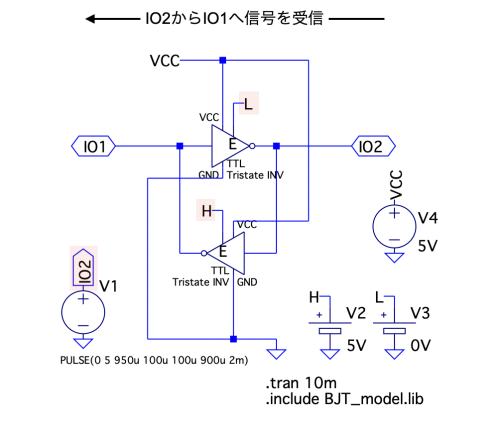

次に図8は,E端子の論理レベルを逆に設定し,上側のトライステート・インバータのE端子は"L"レベルでハイ・インピーダンスの状態,下側のトライステート・インバータのE端子は"H"レベルでインバータ動作になる状態をシミュレーションする回路です.このようにE端子の論理レベルを設定すると,データの転送はIO2からIO1の受信になるので,V1のディジタル信号はIO2側へ接続しています.

図9は,図8のIO1とIO2をプロットしました.IO2はV1のディジタル信号になり,IO1は下側のトライステート・インバータで受信したディジタル信号になります.このようにE端子の論理レベルを変えることにより,データ転送は受信の方向に変化します.

IO2(下段)からIO1(上段)へディジタル信号を受信している.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice8_007.zip

●データ・ファイル内容

Tristate inverter Tran.asc:図4の回路

Tristate inverter Tran.plt:図4のプロットを指定するファイル

Tristate inverter transceiver.asc:図6の回路

Tristate inverter transceiver.plt:図6のプロットを指定するファイル

Tristate inverter transceiver2.asc:図8の回路

Tristate inverter transceiver2.plt:図8のプロットを指定するファイル

tristate_inverter.asc:トライステート・インバータのサブ・サーキット

tristate_inverter.asy:トライステート・インバータのシンボル

BJT_model.lib:バイポーラトランジスタのモデルファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs