LTspiceでディジタル回路入門

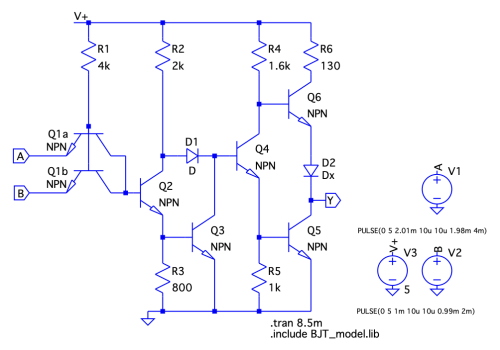

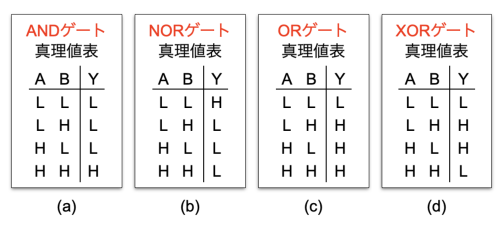

図1は,TTL(Transistor-transistor logic)の回路で,AとBが2つの入力,Yが出力になる論理ゲートです.TTLは,0Vがディジタル信号の"L"(Low),5Vがディジタル信号の"H"(High)に相当します.入力のAとBの信号の組み合わせは4通りになります.その,真理値表は図2のANDゲート,ORゲート,NORゲート,XORゲートのいずれかになります.図1の回路の真理値表は,図2の(a)~(d)どれでしょうか.

AとBが入力,Yが出力

(a)ANDゲート (b)NORゲート (c)ORゲート (d)XORゲート

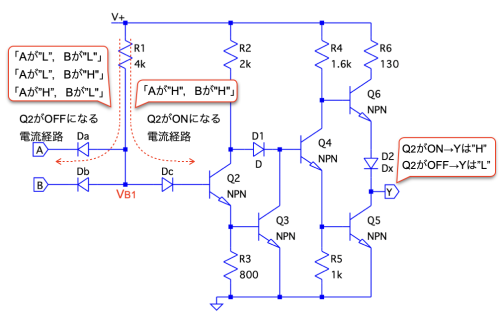

TTLは,バイポーラ・トランジスタと抵抗で構成したディジタル回路です.図1のQ1aとQ1bのNPNトランジスタをPN接合のダイオードに置き換えると回路が分かりやすくなります.置き換えた回路で4通りの信号のときYの論理(0Vまた5V)を検討すると分かります.

図1のNPNトランジスタをダイオードに置き換えて,入力AとBが"H”と"L"の4つの組み合わせを考えます.

4つの入力の組み合わせは,「Aが"L",Bが"L"」と「Aが"L",Bが"H"」,「Aが"H",Bが"L"」,「Aが"H",Bが"H"」となります.

「Aが"L",Bが"L"」と「Aが"L",Bが"H"」,「Aが"H",Bが"L"」の3つの状態のYは"L"になります.「Aが"H",Bが"H"」の状態のYは"H"になります.

よって,Yが"L","L","L","H"となるので,解答は,(a)ANDゲートになります.

●NPNトランジスタをダイオードに置き換える

図3は,Q1aとQ1bのNPNトランジスタをダイオードに置き換えた回路です.NPNトランジスタは,ベースがP型,エミッタとコレクタがN型の半導体です.なので,図3のようにP型のアノードが共通で,N型のカソードがAとB,Q2ベースに繋がる3つのダイオード(Da,Db,Dc)で表すことができます.

ダイオードは,アノードの電圧がカソードの電圧より約0.7V高いときにONとなり,電流がアノードからカソードに流れます.その逆で,アノードの電圧がカソードより低いときや等しいときは,OFFとなって電流は流れません.このようにダイオードは,アノードとカソードに掛かる電圧により,一方向にしか電流を流さないスイッチになります.

次に,Q2がONからOFFになる切り替えは,Da,Db,Dcのアノードの電圧(VB1)で決まります.具体的には,Q2とQ3のベース・エミッタ電圧約0.7VとDcの順方向電圧約0.7Vを加えた,約2.1V付近がしきい値となります.ここでは,図3を使って,図1の真理値表がどうなるのか検討します.

●入力AとBの"H"と"L"でダイオードがON/OFFする

図3のAが"L"のとき,Daのカソードが0Vになります.そのとき,ダイオードのアノードの電圧が,カソードの電圧より高い状態になるので,DaはONします.

逆に,Aが"H"のときはDaのカソードが5Vになります.そのとき,ダイオードのアノードの電圧が,カソードの電圧より低い状態になるので,DaはOFFします.

Bも同じで,Bが"L"のとき,Dbのカソードが0Vになり,DbはONします.

逆に,Bが"H"のとき,Dbのカソードが5Vになり,DbはOFFします.

●4つの組み合わせを回路に入力する

上記動作(AとBが"L"と"H)の4つの組み合わせを回路に入力と「Aが"L",Bが"L"」と「Aが"L",Bが"H"」,「Aが"H",Bが"L"」,「Aが"H",Bが"H"」となります.

「Aが"L",Bが"L"」と「Aが"L",Bが"H"」,「Aが"H",Bが"L"」の3つの状態は,AとBの両方,あるいは,AとBのどちらかが"L"に相当する0Vなので,DaとDbの両方,あるいは,DaとDbのどちらかがONになります.

Da,Dbのどちらか1つがONになると,Da,Db,Dcのアノードの電圧(VB1)は約0.7Vになります.このとき,0.7VはQ2がONになるVB1のしきい値約2.1Vより低いため,Q2はOFFになります.Q2がOFFのときは,Q3はOFF,Q4はON,Q5はON,Q6はOFFになり,Yの電圧はQ5の飽和電圧まで低くなり,ほぼ0Vとなります.この検討より,「Aが"L",Bが"L"」と「Aが"L",Bが"H"」と「Aが"H",Bが"L"」の3つの状態のYは"L"になります.

残りの「Aが"H",Bが"H"」のときはDa,Dbのカソードの両方が5Vなので,Da,DbはOFFになります.これにより,電源の5VからR1とDcを通ってQ2へベース電流が流れてQ2はONになります.Q2がONのときは,Q3はON,Q4はOFF,Q5はOFF,Q6はONになり,Yの電圧は5Vの"H"になります.

なので,この真理値になるのは(a)のANDゲートになります.

●ANDゲートの4つの内部回路

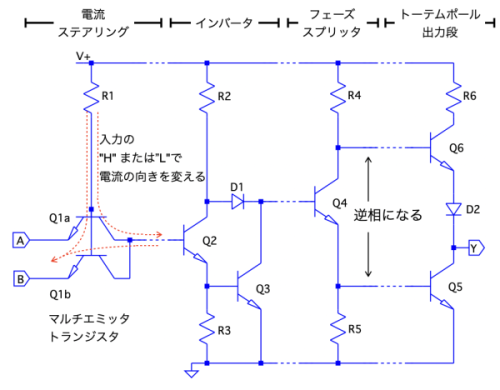

図4は,図1のTTLのANDゲートを4つのブロック(電流ステアリング,インバータ,フェーズ・スプリッタ,トーテム・ポール出力段)に分けました.

ANDゲートは「電流ステアリングがQ1a,Q1b,R1」,「インバータがQ2,Q3,D1,R2,R3」,「フェーズ・スプリッタがQ4,R4,R5」,「トーテム・ポール出力段がQ5,Q6,D2,R6」で構成されています.

ANDゲートは4段構成になっている.

図3で検討したように,電流ステアリングは,AとBの"H"と"L"の状態により電流の経路を変えてQ2をON/OFFします.インバータは,Q2ベースの信号を反転してQ4ベースへ伝えます.フェーズ・スプリッタは,Q4のON/OFFにより,コレクタ側の電圧とエミッタ側の電圧が逆相になる信号を生成します.位相が異なる2つの信号は,トーテム・ポール出力段の入力になり,Q5とQ6を交互にON/OFFさせます.

●ANDゲートを反転するとNANDゲート

図4からQ2,Q3,D1,R2,R3のインバータを取り除き,電流ステアリングとQ4のベースを接続すると,ANDゲートのYの論理を反転したNANDゲートになります.NANDゲートについては過去のメルマガ「TTLの論理ゲート」で解説していますので,そちらを参考にしてください.

●シミュレーションで答え合わせ

図1のANDゲートの真理値をシミュレーションで確かめます.AとBには,V1とV2の信号源に矩形波を入力し,"H"と"L"の4通りを加えます.トランジスタのモデルパラメータは,「.include BJT_model.lib」のコマンドでモデルファイルを読み込みます.モデルファイルは NPNトランジスタのベース・エミッタ間の逆方向飽和電流は「IS=1×10-15A」,順方向の電流増幅率は「BF=10」,順方向のアーリ電圧は「VA=50V」,逆方向の電流増幅率は「BR=0.1」,ダイオードの抵抗は「RS=10Ω」で与えます.

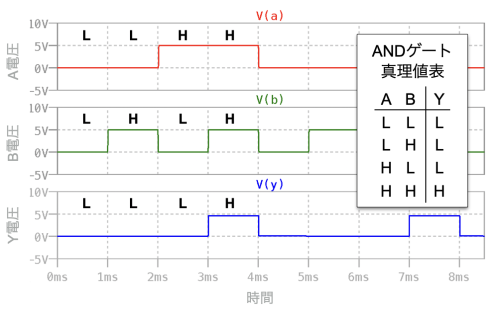

図5は,シミュレーション後のプロットです.上段はAの入力波形,中段はBの入力波形,下段はYの出力波形です.このように,AとBの入力波形とYの出力波形をみると図1の回路がANDゲートの動作になるのが分かります.

ANDゲートの真理値になるのが分かる.

●初段と最終段の間の回路でいろいろな論理ゲートに

以上,ANDゲートのTTLの内部回路について解説しました.TTLの内部回路は,初段が電流ステアリング,最終段がトーテム・ポール出力になっており,初段と最終段の間の回路でいろいろな論理ゲートになるようにしています.初段と最終段が同じことから,入出力特性は同じになり,TTLの入力レベルと出力レベルは論理ゲートが違っても同じになります.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice8_001.zip

●データ・ファイル内容

TTL AND.asc:図1の回路

TTL AND.plt:図1のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) LTspice メール・マガジン全アーカイブs

(04) ◆LTspice電子回路マラソン・アーカイブs

(05) ◆LTspiceアナログ電子回路入門アーカイブs

(06) ◆LTspice電源&アナログ回路入門アーカイブs

(07) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(08) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(09) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs

(10) ◆LTspiceドット・コマンドから学ぶアナログ回路アーカイブs