電圧制御発振回路の制御電圧と発振周波数

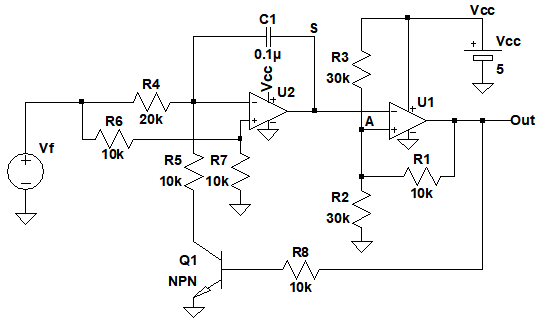

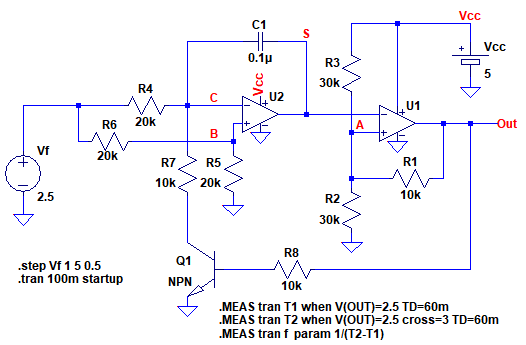

図1は,ヒステリシス・コンパレータ(しきい値の変わる比較器)と積分回路を使用した,電圧制御発振回路(VCO)です.OPアンプ(U1)でヒステリシス・コンパレータを構成し,OPアンプ(U2)が積分回路を構成しています.この回路は,制御電圧源の電圧値(Vf)によって発振周波数が変化します.Vfの値の範囲は1V~5Vとします.このVCOの発振周波数(f)を表す式として正しいのは(a)~(d)のどれでしょうか.ただし,OPアンプは理想的な入出力レール・ツー・レールOPアンプで,VCC=5V,R5=R4/2とします.

発振周波数を表す式は?

(a) f=Vf/(3*R4*C1)

(b) f=Vf/(6*R4*C1)

(c) f=Vf/(12*R4*C1)

(d) f=Vf/(24*R4*C1)

最初にヒステリシス・コンパレータのしきい値のヒステリシス(ヒステリシス幅)がいくつになるかを計算します.次に,Q1がONしているときとOFFしているとき,それぞれの場合に,C1を充電する電流がいくつになるかを計算します.C1を充電する電流が分かれば,S端子の電圧変化が計算できるので,発振周波数を計算することができます.

図1で,ヒステリシス幅(VHW)は,R1とR2が並列になったときと,R3とR1が並列になったときのA点の電圧差になり,3Vになります.また,Q1がONしているときとOFFしているときC1を充電する電流の向きは変わりますが,大きさはどちらも,Vf/(2*R4)になります.この電流とC1の値およびヒステリシス幅から発振周波数を計算すると「f=Vf/(12*R4*C1)」になります.

●ヒステリシス・コンパレータのヒステリシス幅を求める

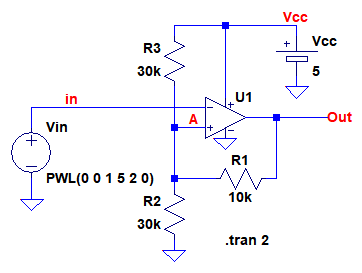

発振周波数を求めるためには,ヒステリシス・コンパレータのヒステリシス幅を知る必要があります.そこで,最初にヒステリシス幅がどのように決まるか考えてみます.図2は図1の回路から,ヒステリシス・コンパレータ部分を取り出したものです.

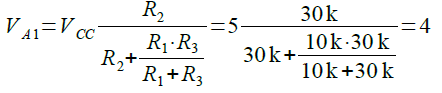

この回路は,反転型のヒステリシス・コンパレータとなっており,入力電圧はOPアンプの反転入力端子に加えられます.入力電圧が0Vの場合,出力は"H"レベルとなり,VCCと同じ電圧になります.このとき,A点の電圧(VA1)は,R2と「R1とR3の並列抵抗」でVCCを分圧したものになり,式1で計算できます.VA1が1つ目のしきい値電圧で,図2の定数を代入すると,4Vになります.

・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・(1)

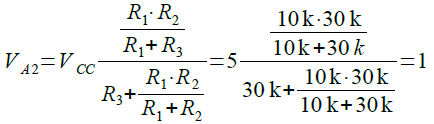

ここで,入力電圧が上昇していき,VA1の値を超えると,コンパレータは反転し,Out端子はGNDレベルになります.このときのA点の電圧(VA2)は,「R1とR3の並列抵抗」とR3でVCCを分圧したものになり,式2で計算できます.このVA2が2つ目のしきい値電圧になります.入力電圧がVA1をこえた後は,入力電圧が,VA2よりも小さくならないと,出力は反転しません.

・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・(2)

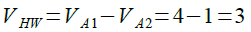

ヒステリシス幅(VHW)はVA1-VA2となり,式3のように3Vになります.

・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・(3)

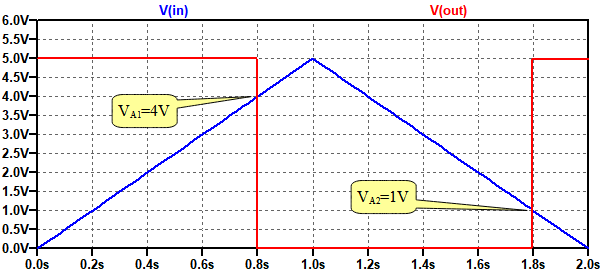

図2において,Vinを0Vから1秒後に5Vになるように変化させ,再び1秒後に0Vまで変化させるようにしてシミュレーションした結果が図3になります.Vinが4Vになったときに出力が0Vとなり,Vinが1Vよりも小さくなると,再び出力が5Vになっています.

しきい値電圧が4Vと1Vに変化していることが分かる.

●積分回路の動作を解析する

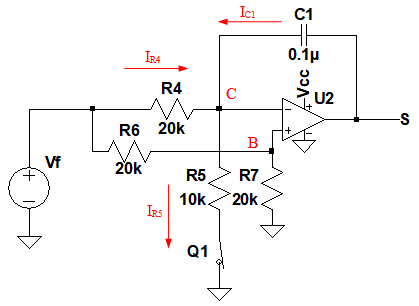

図4は,図1の積分回路部分を取り出したものです.図1のトランジスタQ1は,スイッチとして動作しており,Out端子が"H"レベルのときにONします.図4はQ1がONした状態になっています.

C1に左向きの電流が流れ,S端子の電圧は上昇していく.

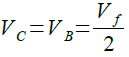

図4において,R6とR7の値が等しいため,B点の電圧(VB)はVfの電圧の1/2になっています.また,OPアンプが正常に動作している場合,プラス入力端子とマイナス入力端子の電圧は等しくなるため,C点の電圧(VC)はB点の電圧と等しくなります.これを式で表したものが,式4になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

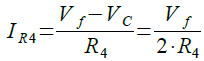

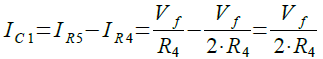

このとき,抵抗R4に流れる電流は,式5で表されます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

また,抵抗R5に流れる電流は,式6で表されます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

R5の方がR4よりも小さいので,電流値はIR4よりもIR5のほうが大きくなります.そのため,C1の電流(IC1)は左向きに流れます.その大きさはR5=R4/2とすると式7になります.

・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・(7)

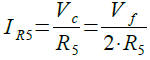

図5は,図1の発振波形です(図1をシミュレーションする回路は後出の図7).図5を見ると分かるように,図1のOut端子が"H"レベルのときは,式7の電流でC1が充電され,積分回路の出力のS端子の電圧は上昇していきます.

図1の回路で,Vf=2.5Vのときの波形を取り出したもの.

そして,S端子の電圧が,ヒステリシス・コンパレータのしきい値電圧のVA1に達するとOut端子が"L"レベルになります.S端子の電圧がVA2からVA1まで変化するために必要な時間(T1)は式8で計算できます.

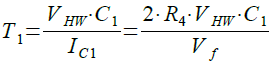

・・・・・・・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・・・・・・・(8)

次に,Out端子の電圧が"L"レベルになり,Q1がOFFした状態の動作を考えます.図6がQ1がOFFした状態の積分回路です.Q1がOFFしているため,R5には電流は流れません.そのため,C1に流れる電流(IC1)は右向きとなり,その大きさはIR4と等しくなります.C1は式5の電流で充電されていきますが,図4とは逆に,S端子の電圧は下降していきます.

C1に右向きの電流が流れ,S端子の電圧は下降していく.

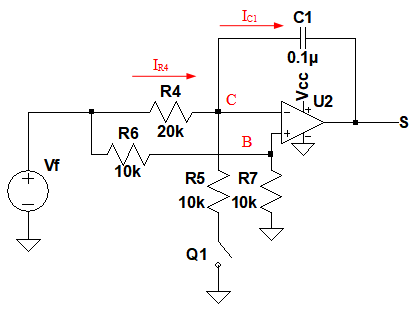

S端子の電圧がVA1からVA2まで変化するために必要な時間(T2)は式8と同じになります.S端子の電圧がVA2からVA1に変化し,再びVA2になる時間が発振の1周期(T)で,その逆数が発振周波数になります.ヒステリシス幅(VHW)を3Vとすると,発振周波数(f)は式9で表されます.

・・・・・・・・・・・・・・・(9)

・・・・・・・・・・・・・・・(9)

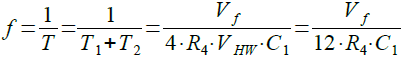

●電圧制御発振回路の制御特性をシミュレーションする

図7は,図1の回路をシミュレーションするための回路です.「.STEPコマンド」を使用して,Vfの値を1Vから5Vまで0.5Vステップで変化させます.そして,それぞれのVfの値のときの発振周波数を「.MERSコマンド」で計算します.

1行目の「.MEAS tran T1 when V(OUT)=2.5 TD=60m」では,解析開始60ms以降でV(OUT)が2.5Vになったときの時間をT1という変数に代入します.

2行目の「.MEAS tran T2 when V(OUT)=2.5 cross=3 TD=60m」では,解析開始60ms以降でV(OUT)が3回目に2.5Vになったときの時間をT2という変数に代入します.

T2とT1の差が発振の1周期の時間になるため,3行目の「.MEAS tran f param 1/(T2-T1)」で周波数を計算し,fという変数に代入します.

Vfの値を1Vから5Vまで0.5Vステップで変化させ,.MERSコマンドで周波数を計算する.

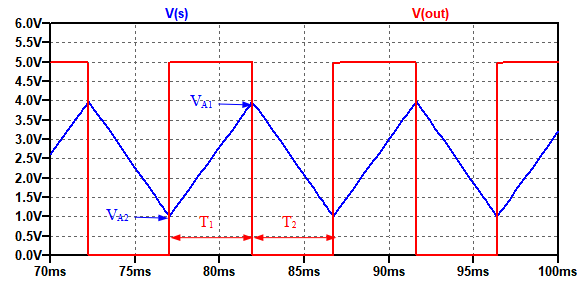

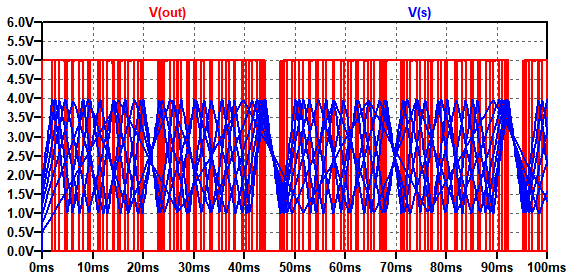

図8は,図7のシミュレーション結果です.S端子とOut端子の電圧を表示しています.7種類のVfの値のシミュレーション結果が重ねて表示されています.

7種類のVfの値のシミュレーション結果が重ねて表示されてる.

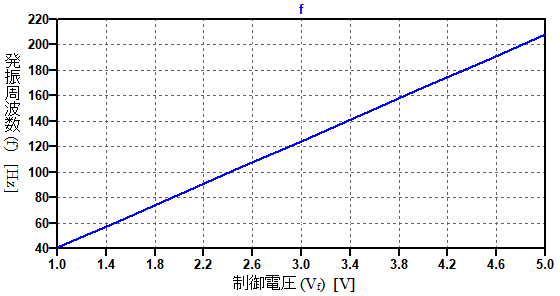

次に,制御電圧(Vf)と発振周波数の関係をグラフにします.「.MERS」の計算結果はエラー・ログに記録されています.Ctrl+Lキーを押してエラー・ログを表示し,そのエラー・ログの中で右クリックして,[Plot .step'ed .meas data]を選択します.

そして表示されウィンドウで[Plot Settings],[Add Trace]コマンドを選択して表示された画面でfを選択し,OKボタンを押します.すると,図9のように,横軸が制御電圧(Vf)で縦軸が発振周波数(f)のグラフが表示されます.

発振周波数は式9で計算した値とほぼ一致している.

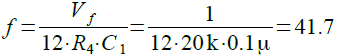

Vfが1Vから5Vまで変化すると,発振周波数は40Hzから210Hzまで変化していることが分かります.式9でVfを1Vとしたときの周波数を計算すると,式10のように41.7Hzとなり,シミュレーション結果とほぼ一致していることが分かります.

・・・・・・・・・・・・・・・・・・・(10)

・・・・・・・・・・・・・・・・・・・(10)

以上,電圧制御発振回路の制御電圧と発振周波数の関係を解説しました.図1の回路は,発振周波数が高くなると,コンパレータやトランジスタの応答速度が誤差となり,発振周波数が計算式よりも低くなることに注意が必要です.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice7_039.zip

●データ・ファイル内容

his.asc:図2の回路

VCO/asc:図7の回路

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) トランジスタ技術公式サイト LTspiceの部屋はこちら

(04) LTspice メール・マガジン全アーカイブs

(05) ◆LTspice電子回路マラソン・アーカイブs

(06) ◆LTspiceアナログ電子回路入門アーカイブs

(07) ◆LTspice電源&アナログ回路入門アーカイブs

(08) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(09) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(10) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs