出力のSN比が高くなる抵抗ネットワークの選択

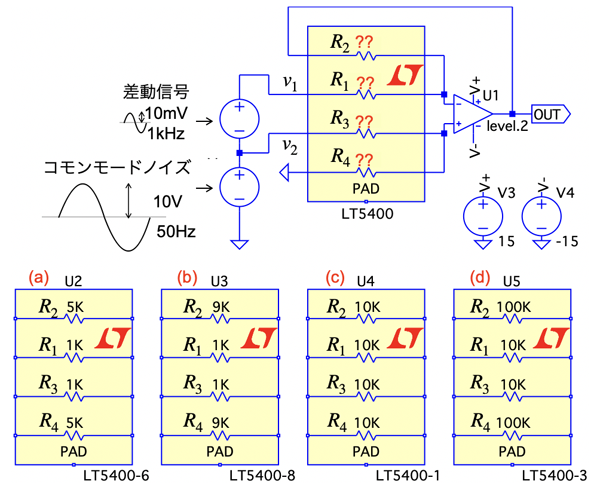

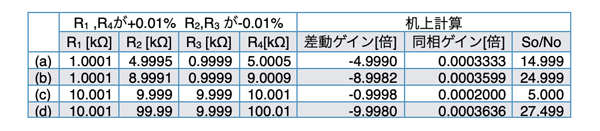

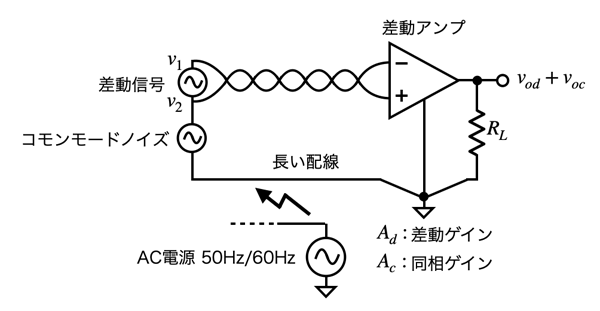

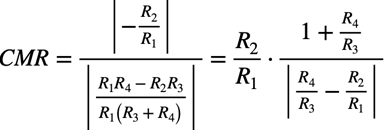

図1は,差動信号に商用電源のコモン・モード・ノイズが加わった電圧を差動アンプで増幅する回路です.差動アンプは,OPアンプと整合したクワッド抵抗ネットワーク(LT5400)を使用しています.実際のLT5400は,4本の抵抗間の整合がカタログ値で±0.01%で,(a)~(d)の異なった組み合わせの抵抗値があります.

図1で,出力の信号対雑音比(出力のSN比:So/No)が最も高くなる(良くなる)抵抗ネットワークは,(a)~(d)のどの抵抗ネットワークはどれでしょうか.ただし,OPアンプは理想とします.

LT5400を入れ替えたとき出力のSN比が最も高くなるのはどれ?

(a)の抵抗ネットワーク

(b)の抵抗ネットワーク

(c)の抵抗ネットワーク

(d)の抵抗ネットワーク

差動アンプの入力信号は,「v1-v2」の差動信号と,v2のコモン・モード・ノイズになります.コモン・モード・ノイズは,回路の近くにある商用電源などから容量結合で図1の配線に伝わる外来のノイズです.差動アンプの出力には差動信号を差動ゲインで増幅した電圧「So」と,コモン・モード・ノイズを同相ゲインで増幅した電圧「No」が現れます.差動ゲインと同相ゲインはクワッド抵抗ネットワークの整合に関係するので,4本の抵抗が±0.01%で変化した最悪の組み合わせのときの出力のSN比「So/No」を検討すると分かります.

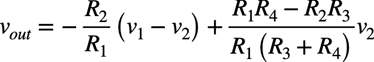

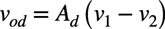

図1の差動アンプの出力電圧は,差動信号を「v1-v2」,コモン・モード・ノイズを「v2」とすると,式1になります.

・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・(1)

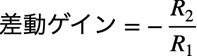

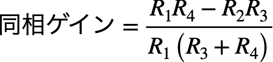

式1より差動ゲインは,差動信号にかかる項なので式2になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

同様に,同相ゲインは,コモン・モード・ノイズにかかる項なので式3になります

・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・(3)

抵抗間の整合が0%(理想)のときは,式3の分子が「R1R4-R2R3=0」となり,同相ゲインがゼロになるので,コモン・モード・ノイズは,出力に現れません.反対に抵抗間の整合が有るときは同相ゲインが生まれて出力にコモン・モード・ノイズが現れます.「R1R4-R2R3=0」の関係を分かりやすいように抵抗比に書き直すと式4になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

次に抵抗間の整合で出力の同相ゲインが最大になる条件について検討します.式4の抵抗間の整合が±0.01%のとき,R2/R1とR4/R3のズレが最大になる抵抗は,R1とR4が+0.01%,R2とR4が-0.01%になります.

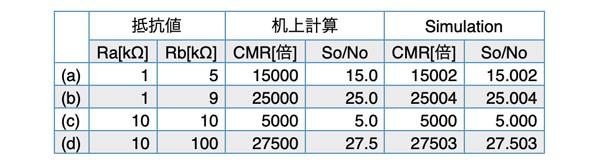

表1は,(a)~(d)の抵抗ネットワークでR1とR4が+0.01%,R2とR3が-0.01%になる抵抗値を入れました.次にその抵抗値を使い,式2の差動ゲイン,式3の同相ゲインを机上計算しました.

最後に図1の差動信号の振幅10mVを差動ゲインで増幅した電圧と,コモン・モード・ノイズの振幅10Vを同相ゲインで増幅した電圧より,出力のSN比「So/No」を机上計算しました.表1のSo/Noより,出力のSN比が最も高いのは「So/No=27.499」であり,この抵抗ネットワークは(d)になります.

R1とR4が+0.01%,R2とR3が-0.01%とした.

●差動アンプ出力のSN比はCMRに依存する

図2は,差動信号源と差動アンプの距離が離れていて,長い配線で接続しているときを表しました.配線が長いと,回路の近くにある商用電源等の高い電圧線から容量結合により外来のコモン・モード・ノイズが加わることがあります.このようなとき,差動アンプの出力には「v1-v2」の差動信号を増幅したvodと,v2のコモン・モード・ノイズを増幅したvocが現れ,「vod/voc」が出力のSN比になります.

周囲にある回路からの外来ノイズがコモン・モード・ノイズになる

vodとvocの出力のSN比について詳しく調べます.差動アンプの差動ゲインをAdとすると,vodは式5になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

差動アンプの同相ゲインをAcとすると,vocは式6になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

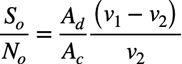

コモン・モード・ノイズが加わった差動アンプ出力のSN比は式7になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

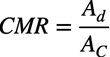

ここで,式7のAd/Acの項は,式8に示す差動アンプのCMR(同相信号除去比)になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

式7と式8より,差動信号とコモン・モード・ノイズが同じ振幅の条件なら,差動アンプのCMRを高くすると出力のSN比も高くなります.CMRは差動ゲインと同相ゲインの比なので,CMRを高くするには,式2の差動ゲインを高くするか,あるいは式3の同相ゲインを低くするかの2通りになります.先程の表1に示した同相ゲインをみると,(a)~(d)の抵抗ネットワークでは0.0002~0.00036の範囲となり大きな変化はありません.このようなときは差動ゲインが最も高い(d)の抵抗ネットワークを選ぶとCMRが高くなり,出力のSN比も高くなります.

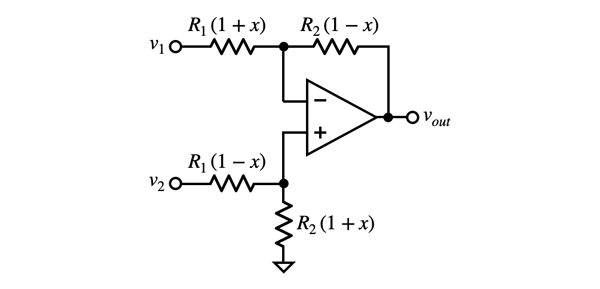

●差動アンプのCMRは抵抗の整合で決まる

ここでは,CMRと抵抗の整合の関係を検討し,抵抗間の整合から差動アンプのCMRを求めます.差動アンプのCMRは式8なので,式2の差動ゲインと式3の同相ゲインを使うと,CMRは式9になります.CMRは極性が無いので絶対値を使います.式9より「R2/R1=R4/R3」になれば抵抗の整合によるCMRは無くなり,OPアンプのCMRまで近づくことになります.しかし,実際は抵抗間の整合が有るので差動アンプのCMRは抵抗の整合で決まることになります.

・・・・・・・・・・・・・・・・(9)

・・・・・・・・・・・・・・・・(9)

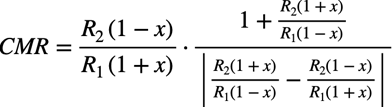

図3は,抵抗間の%で表した整合を少数に直したxを用い,出力の同相ゲインが最大になる条件にしました.そして図1の設計値は「R1=R3,R2=R4」であることから,回路の抵抗はR1とR2のみで表しました.

図3のCMRは式10になります.

・・・・・・・・・・・・・・・(10)

・・・・・・・・・・・・・・・(10)

計算が長くなるので省きますが,式10を近似すると式11になり,差動アンプの抵抗の整合xとR2/R1の比からCMRが計算できます.

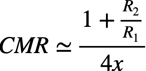

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(11)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(11)

先程の式7と式8より,式11のCMRを使って出力のSN比を表すと式12になります.式11と式12を使うと,表1の検討より計算がシンプルになります.この計算の具体的な使用例は,次の章で解説します.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(12)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(12)

●机上計算とシミュレーションを比較する

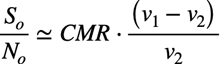

図4は,図1の(a)~(d)の抵抗ネットワークが±0.01%の整合のときの差動アンプのCMRをシミュレーションで求める回路です.RaとRbの抵抗値と,xの整合は「.param」で数値を入れます.「.param」はユーザ定義変数へパラメータを渡します.具体例を一つ挙げると「.param x=0.0001」は「x」の変数は「0.0001」という意味になります.CMRの求め方は過去のメルマガ「OPアンプの誤差が分かる場所」に解説しましたので,そちらを参考にしてください.

「.param」を入れ替えてシミュレーションする.

図4で使用したドット・コマンドは「.dc V2 0 10 0.1」です.これは,v2の電圧を0Vから10V間を0.1Vステップで変化させたDC解析を実行するという意味になります.「.MEAS」コマンドは,シミュレーション値を直読します.具体的には,次のようになります.

「.MEAS DC Vo1 FIND V(OUT) AT 0」

v2が0VのときのOUTの電圧を探し,Vo1に入れます.

「.MEAS DC Vo2 FIND V(OUT) AT 10」

v2が10VのときのOUTの電圧を探し,Vo2に入れます.

「.MEAS DC CMR PARAM (10*(Rb/Ra))/abs(Vo1-Vo2)」

v2が0Vと10Vのときの出力電圧Vo1とVo2を用い,CMRを計算して.MEASステートメントのCMRに入れます.

「.MEAS DC So/No PARAM CMR*0.01/10」

この計算は先程の式12になります.先程の「.MEAS」で計算したCMRを使い,差動信号が10mV,コモン・モード・ノイズが10Vのときの出力のSN比を計算してSo/Noへ入れます.

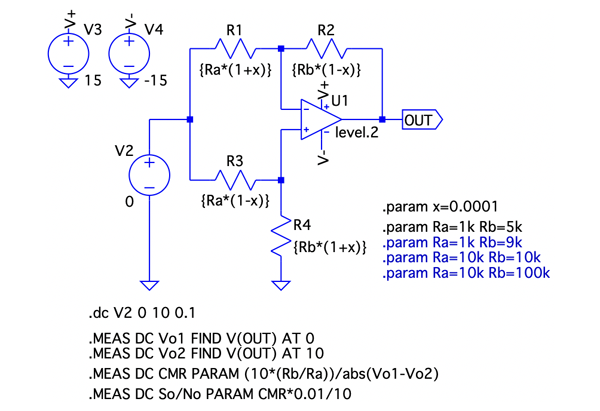

図5は,図4のシミュレーション終了後,「.MEASコマンド」の結果を表示しました.「.MEAS」の結果はログ・ファイルに記録されます.ログ・ファイルは,メニュー・バーから[View]→[SPICE Error Log]で表示する方法と,ショート・カット・キーの「Crtl+L」を用いる方法があります.

測定した値はログ・ファイルにある.

表2は図4の「.param Ra=1k Rb=5k」~「.param Ra=10k Rb=100k」を入れ替えて,図1の(a)~(d)の抵抗ネットワークについて,机上計算とシミュレーションした結果をまとめた表になります.表2より,式11の近似式で求めたCMRと式12の出力のSN比は,シミュレーション値と一致することが分かります.そして表1と表2の「So/No」は同じ結果となり,(a)~(d)の抵抗ネットワークの中でコモン・モード・ノイズによる出力のSN比が最も高くなるのは(d)であることが分かります.

出力のSN比が最も高くなるのは(d)の抵抗ネットワークになる.

●出力のSN比が最も低くなる回路を確認

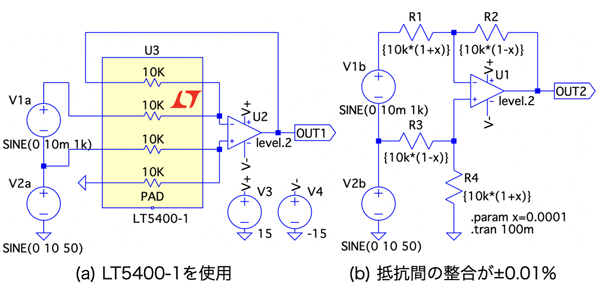

図6は,トランジェント解析を用いて,出力のSN比が最も低くなる,図1の(c)の抵抗ネットワークの波形をシミュレーションする回路です.使用したドット・コマンドは「.tran 100m」です.これは0ms~100ms間のトランジェント解析を実行するという意味になります.図6(a)はLT5400-1を使い,抵抗間の整合が0%(理想)のときのトランジェント解析,図6(b)は抵抗間の整合が±0.01%(実際)のときのトランジェント解析です.

(a)抵抗間の整合が0%(理想),(b)抵抗間の整合が±0.01%(実際)

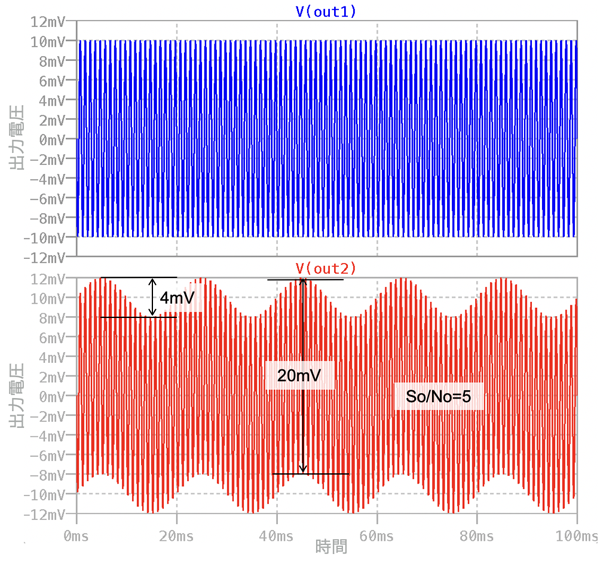

図7の上段が図6(a), 下段が図6(b)のプロットです.上段は抵抗の整合が0%なので,出力にコモン・モード・ノイズは現れません.下段の抵抗間の整合が±0.01%のときのプロットは,大きなうねりが50Hzのコモン・モード・ノイズを増幅した波形,時間の細かな振幅が1kHzの差動信号を増幅した波形です.トランジェント解析で目視すると出力のSN比は悪いのが分かります.図6(b)のプロットのピークtoピークで測定した出力のSN比は「So/No=5」となり,表2(c)と同じになります.

上段は抵抗間の整合が0%(理想),下段は±0.01%(実際)

●出力のSN比が最も高くなる回路を確認

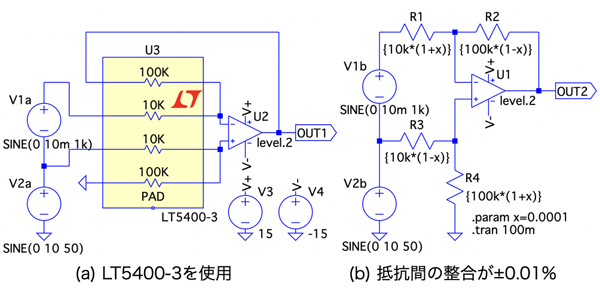

次に,図8は出力のSN比が最も高くなるときの図1の(d)の波形をシミュレーションする回路です.図8(a)はLT5400-3を使い,抵抗間の整合が0%(理想)のとき,図8(b)は抵抗間の整合が±0.01%(実際)です.使用したドット・コマンドは図6と同じです.

(a)抵抗間の整合が0%(理想) (b)抵抗間の整合が±0.01%(実際)

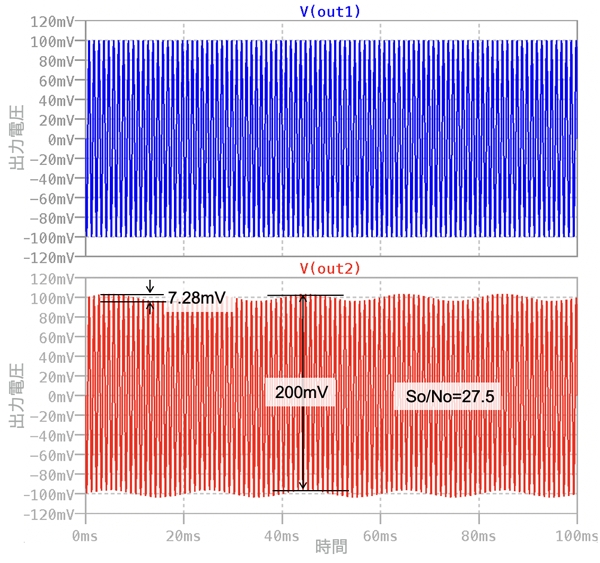

図9の上段が図8(a), 下段が図8(b)のプロットです.上段の抵抗間の整合が0%のときは,図7と同様に出力にコモン・モード・ノイズは現れません.下段の抵抗間の整合が±0.01%のときのプロットは,大きなうねりが50Hzのコモン・モード・ノイズを増幅した波形,時間の細かな振幅が1kHzの差動信号を増幅した波形です.図7と比べると一目で出力のSN比が高くなっているのが分かります.下段のプロットのピークtoピークで測定した出力のSN比は「So/No=27.5」となり,表2(d)と同じになります.

上段は抵抗間の整合が0%,下段は±0.01%

以上,解説したように,差動信号とコモン・モード・ノイズが同じ振幅の条件なら,差動アンプのCMRを高くすると出力のSN比も高くなります. ここでは検討しませんでしたが,信号源の出力抵抗は差動アンプのR1とR3に直列になります.このため見かけ上の抵抗の整合が悪くなってCMRが低くなり,コモン・モード・ノイズの出力のSN比も低下するので注意してください.

なお,LT5400は,抵抗の絶対値と抵抗比の組み合わせで8種類あります.使用例は負帰還アンプの入力バイアス電流による誤差を抑えるときや高精度な抵抗分圧回路,そして今回のような差動アンプです.ゲインは回路の要求で決まるので,それに見合った抵抗比を選んだり,同じ抵抗比でもノイズを抑えるときは絶対値が小さいものというように使い分けます.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice7_032.zip

●データ・ファイル内容

Differential Amplifer CMR.asc:図4の回路

Differential Amplifer Tran1.asc:図6の回路

Differential Amplifer Tran1.plt:図7のプロットを指定するファイル

Differential Amplifer Tran2.asc:図8の回路

Differential Amplifer Tran2.plt:図9のプロットを指定するファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) トランジスタ技術公式サイト LTspiceの部屋はこちら

(04) LTspice メール・マガジン全アーカイブs

(05) ◆LTspice電子回路マラソン・アーカイブs

(06) ◆LTspiceアナログ電子回路入門アーカイブs

(07) ◆LTspice電源&アナログ回路入門アーカイブs

(08) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(09) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(10) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs