CMOSアナログ・スイッチの動作

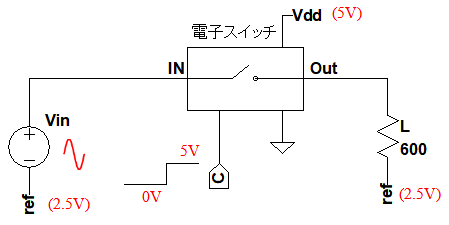

図1は,電子スイッチを使用して,信号のON/OFFを行う回路です.この回路の仕様を,Vddが5V,ref電圧が2.5V,Vinがピーク電圧2Vで1kHzの正弦波と考えています.C端子には,制御信号を入力しますが,制御信号が0Vのとき信号を遮断し,5Vのときに通過するようにします.この電子スイッチに,CMOSを使用したアナログ・スイッチで構成する場合,意図した動作となる回路は図2の(a)~(d)のどれでしょうか.

C端子が0Vのとき信号を遮断し,5Vのとき通過させたい.

図1に使用する回路として適切なものはどれ?

(a)の回路 (b)の回路 (c)の回路 (d)の回路

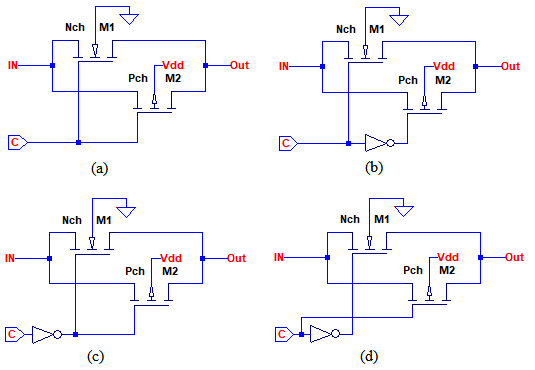

図2の回路には,PチャネルのMOSトランジスタとNチャネルのMOSトランジスタが使用されています.それぞれの極性のMOSトランジスタが,どのようなゲート電圧のときにONするのかを考えれば,答えは簡単に分かります.

図2の(a)と(c)の回路は,PチャネルのMOSトランジスタとNチャネルのMOSトランジスタのゲートが接続されています.そのため,C端子の電圧が0Vのときも5Vのときも,どちらかのMOSトランジスタがONするため,信号が遮断できません.なので(a)と(c)は,スイッチとして機能しません.

(b)の回路は,C端子の電圧が0Vのとき,NチャネルのM1はOFFになります.そのときPチャネルのM2のゲート電圧はインバータによって5Vになるため,M2もOFFになり,信号を遮断します.次にC端子の電圧が5Vになると,M1とM2が両方ともONし,信号を通過させます.これは,図1の意図した動作なので,正解は(b)ということになります.

なお,(d)の回路は,(b)の回路とは逆に,C端子の電圧が0Vのときに信号が通過します.つまりON/OFFが逆になります.

●Nチャネル単独のMOSトランジスタを使用したアナログ・スイッチ

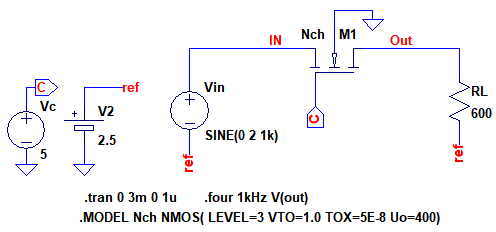

MOSトランジスタは,ゲート電圧によって,ON/OFFをコントロールできるため,アナログ・スイッチとして使用することができます.図3は,NチャネルのMOSトランジスタのみで構成したアナログ・スイッチです.ゲートに5Vを印加して,信号通過モードのシミュレーションを行います.また,「.FOURコマンド」を使用し,OUT端子のひずみ率を表示できるようにしています.「.FOURコマンド」は「.FOUR 解析周波数 解析出力」というように指定します.

ゲートに5Vを印加して,信号通過モードのシミュレーションを行う.

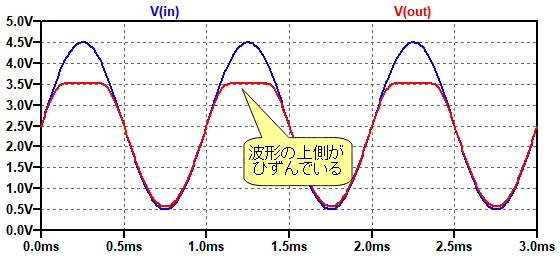

図4は,図3のシミュレーション結果です.出力の上側の振幅が小さくなっており,波形がひずんでいることが分かります.これは,IN端子の電圧が高くなると,NチャネルMOSトランジスタのソース電圧が高くなるためゲート・ソース間電圧が小さくなり,MOSトランジスタのON抵抗が大きくなってしまうためです.

出力の上側の振幅が小さくなっており,波形がひずんでいる.

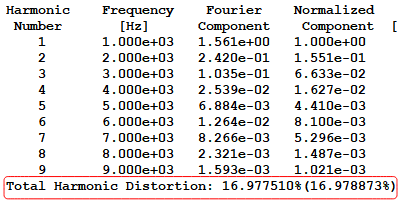

図5は「.FOURコマンド」のひずみ率(THD:Total Harmonic Distortion)です.図3の回路図もしくは図4のグラフの状態で「Ctrl+L」キーを押して表示されるエラー・ログの中にあります.ひずみ率は,17%となっています.

ひずみ率(THD)は17%となっている.

●Pチャネル単独のMOSトランジスタを使用したアナログ・スイッチ

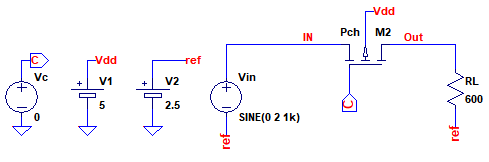

図6は,PチャネルMOSトランジスタのみで構成したアナログ・スイッチです.ゲート電圧を0Vとして,信号通過モードのシミュレーションを行います.

ゲート電圧を0Vとして,信号通過モードのシミュレーションを行う.

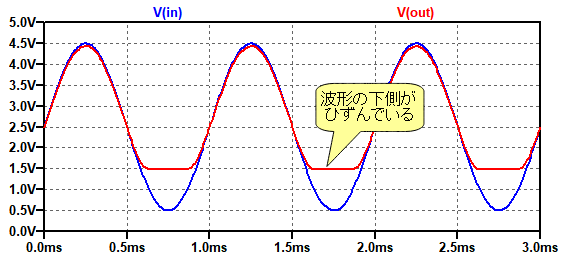

図7は,図6のシミュレーション結果です.Nチャネルのときとは逆に,Out端子の下側の振幅が小さくなっており,波形がひずんでいることが分かります.これは,IN端子の電圧が低くくなると,PチャネルMOSトランジスタのソース電圧が低くなるためゲート・ソース間電圧が小さくなり,MOSトランジスタのON抵抗が大きくなってしまうためです.

出力の下側の振幅が小さくなっており,波形がひずんでいる.

●NチャネルとPチャネル組み合わせでMOSトランジスタを使用したアナログ・スイッチ

MOSトランジスタを1つだけ使用したアナログ・スイッチでは,入力振幅が大きなときに,波形がひずんでしまいます.しかし,NチャネルMOSトランジスタとPチャネルMOSトランジスタを組み合わせて使用すると,この問題を解決することができます.

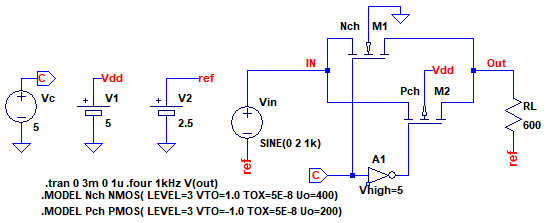

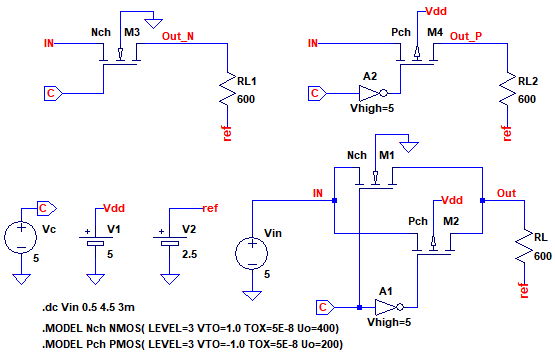

図8がNチャネルMOSトランジスタとPチャネルMOSトランジスタを組み合わせたアナログ・スイッチ回路です.C端子を5Vとすることで,NチャネルMOSトランジスタと,PチャネルMOSトランジスタの両方がONします.

C端子の電圧を5Vとして,通過モードのシミュレーションを行う.

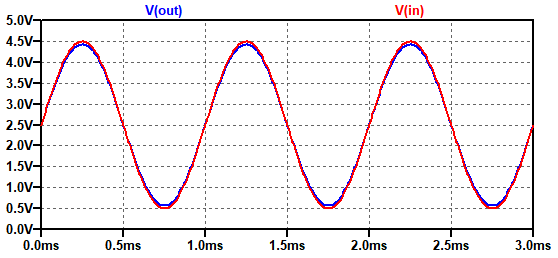

図9は,図8のシミュレーション結果です.単一のMOSトランジスタのときのような,出力のひずみはありません.

単一のMOSトランジスタのときのような,出力のひずみは無い.

図10は,図5と同様のやり方で表示したエラー・ログの中にある,「.FOUR解析」のひずみ率(THD)です.ひずみ率は,0.2%と大幅に改善していることが分かります.

ひずみ率(THD)は0.2%となっている

●Nチャネル単独,Pチャネル単独,NチャネルとPチャネル組み合わせの3種類を同時に確認

図11は,Nチャネル単独,Pチャネル単独,NチャネルとPチャネル組み合わせの3種類のアナログ・スイッチのON抵抗をシミュレーションするための回路です.Vinを0.5Vから4.5Vまで変化させます.

Vinを0.5Vから4.5Vまで変化させる.

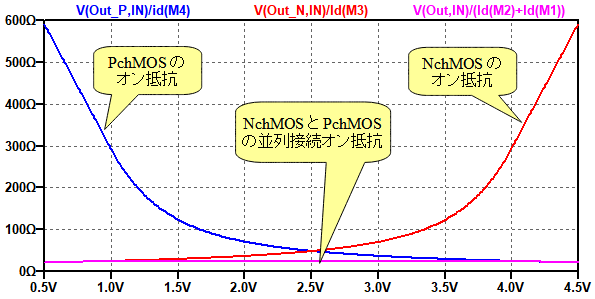

図12がON抵抗のシュミレーション結果です.各スイッチの出力端子と入力端子の電圧差を,スイッチに流れる電流で割ることで,ON抵抗を求めています.

各スイッチの出力端子と入力端子の電圧差をスイッチに流れる電流で割ったものを表示.

図12を見ると分かるように,PchMOSトランジスタを使用したアナログ・スイッチは,入力電圧が低いときのON抵抗が大きく,NchMOSトランジスタを使用したアナログ・スイッチは,入力電圧が高いときのON抵抗が大きくなっています.

一方,NchMOSトランジスタとPchMOSトランジスタ並列接続したアナログ・スイッチは,入力電圧によるON抵抗の変化が小さいことが分かります.

●NチャネルとPチャネル組み合わせアナログ・スイッチの接続による違い

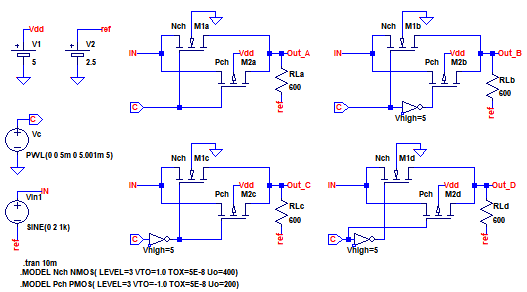

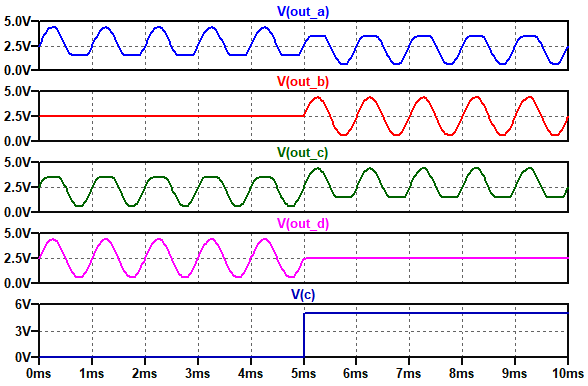

最後に,図13の回路図で,問題の(a)~(d)のアナログ・スイッチ回路のコントロール特性をシミュレーションします.C端子の電圧は最初は0Vで,5msec後に5Vにします.

C端子の電圧は最初は0Vで,5msec後に5Vになる.

図14は,図13のシミュレーション結果です.問題文のように,「C端子の電圧が0Vのとき信号を遮断し,5Vのとき通過させる」という動作をしているのは,(b)の回路のV(out_b)です.(a)の回路のV(out_a)と(c)の回路のV(out_c)は,信号が遮断できません.なのでスイッチとして機能しません.(d)の回路のV(out_d)は,(b)の回路とは逆に,C端子の電圧が0Vのときに信号が通過します.つまりON/OFFが逆になります.

C端子の電圧が0Vのときは信号を遮断し,5Vのときに通過させているのはV(out_b).

以上,CMOSアナログ・スイッチについて解説しました.CMOSアナログ・スイッチを使用した信号切り替え回路で,さらに低ひずみにしたいときは,OPアンプを使用した反転増幅回路の,反転入力端子側にCMOSアナログ・スイッチを挿入する,といった工夫が必要になります.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice7_025.zip

●データ・ファイル内容

AnalogSW_Nch.asc:図3の回路

AnalogSW_Pch.asc:図6の回路

AnalogSW.asc:図8の回路

AnalogSW_Ron.asc:図11の回路

AnalogSW_Ron.plt:図12のグラフを描画するためのPlot settinngsファイル

AnalogSW_CTRL.asc:図13の回路

AnalogSW_CTRL.plt:図14のグラフを描画するためのPlot settinngsファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) トランジスタ技術公式サイト LTspiceの部屋はこちら

(04) LTspice メール・マガジン全アーカイブs

(05) ◆LTspice電子回路マラソン・アーカイブs

(06) ◆LTspiceアナログ電子回路入門アーカイブs

(07) ◆LTspice電源&アナログ回路入門アーカイブs

(08) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(09) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(10) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs