周辺回路で用途が変わる555タイマIC

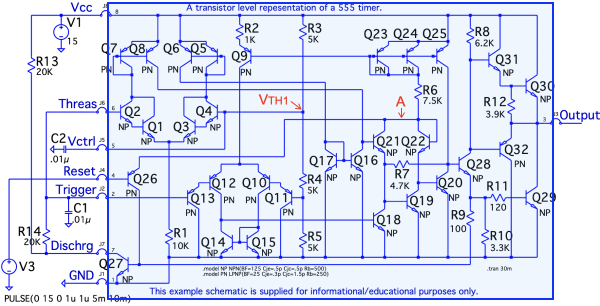

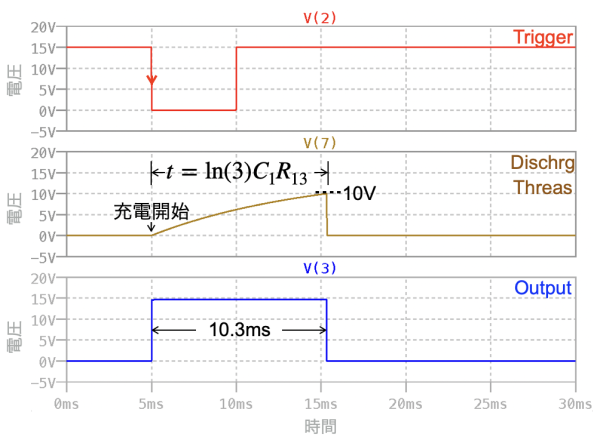

図1は,555タイマICに周辺回路を接続した無安定モードの発振回路です.青色で囲った部分が,555タイマICの内部回路です.その左側に抵抗(R13,R14)やコンデンサ(C1,C2),電圧源(V1,V3)がつながった周辺回路がありその端子には,Vcc,Threas,Vctrl,Reset,Trigger,Dischrge,GND,Outputと名前が記載されています.

(a)~(d)は,回路の端子の特性を表しています.1つは正しく,残り3つは間違えています.正しいのはどれでしょうか.

ドキュメント\LTspiceXVII\examples\Educational\NE555.asc

(a) VctrlとGND間にあるC2の電圧は5Vとなる

(b) Resetが0VになるとOutputはHighとなる

(c) OutputとDischrgのHighとLowは逆相になる

(d) OutputのLowの電圧は約0Vである

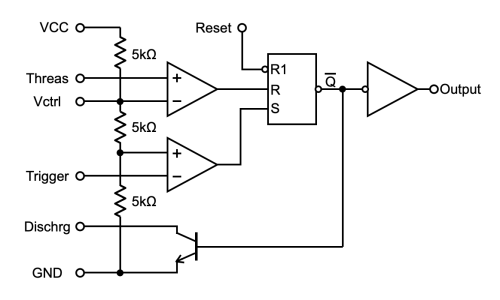

555タイマICの内部は,2つのコンパレータ,しきい値を生成する抵抗,フリップ・フロップ,出力段からなる回路で,周辺回路により「双安定モード」,「単安定モード」,「無安定モード」が作れます.

(a)は,電源電圧(V1)が15Vですので,内部回路で決まるVTH1の電圧を検討すると分かります.

(b)は,Resetが0VのときのA点の電圧を検討すると分かります.A点の電圧はQ20をONあるいはOFFのどちらかにします.

(c)は,Q27とQ29のON/OFFのタイミングの関係を検討すると分かります.

(d)は,OutputがLowのとき,どのトランジスタがONしているかを検討すると分かります.

(a)のC2の電圧は,内部回路のVTH1の電圧です.VTH1の電圧は「R3=5kΩ」と「R4+R5=10kΩ」の分圧です.電源電圧が「Vcc=15V」より,C2の電圧は,10Vとなります.これより(a)は,間違いです.

(b)の555タイマICのOutputは,ThreasやTriggerの信号により,Q20がONするとOutputがHigh,逆に,Q20がOFFするとOutputがLowになります.Q20がONするには,A点の電圧が「VBE20+VBE22」必要となります.しかし,Resetが0VになるとQ26がONとなり,A点の電圧が「VBE26」となるので,「VBE20+VBE22」より低く,Q20は,ONの条件になりません.この回路動作により,ThreasやTriggerの信号よりReset信号が優先になるので,Resetが0VになるとOutputはLowとなります.これより(b)は間違いです.

(c)のOutputとDischrgのHighとLowは,Q28のON/OFFで決まります.Q28がONしたときのエミッタ電流は,Q27とQ29のベース電流となりONします.Q28がOFFするとQ27とQ29はOFFとなります.これより同相でHighとLowになるので,(c)は間違いです.

(d)のOutputがLowのとき,Q29がON,Q30がOFFとなります.Outputの電圧は,Q29のコレクタ・エミッタ間の飽和電圧となり0Vに近づくので(d)が正解となります.

●555タイマICの内部回路

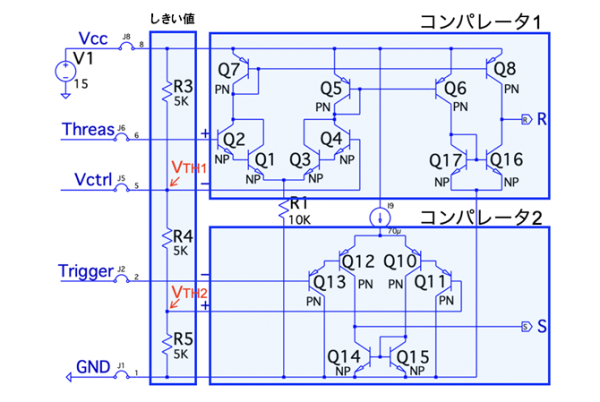

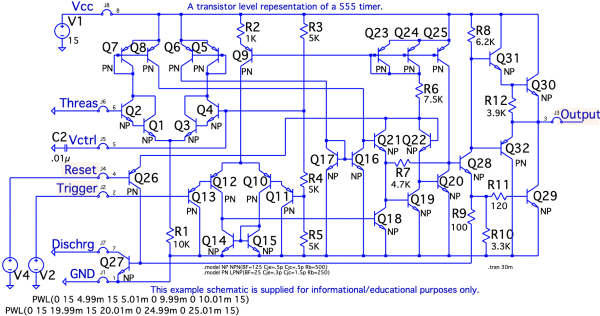

555タイマICは,周辺回路により,フリップ・フロップ動作や遅延時間の発生,発振回路として使われています.図1の555タイマICの内部回路は,図2のコンパレータ1とコンパレータ2としきい値の生成,そして図3のフリップ・フロップと出力回路からなります.ここでは,まず,図2と図3を使い,555タイマICの内部回路について解説します.

図2は,図1の2つのコンパレータを書き直した回路です.コンパレータ1,コンパレータ2の入力は,ダーリントン接続した差動アンプです.ダーリントン接続は,Q2,Q4とQ11,Q13のベース電流が低くなるので,高い抵抗値や小さなコンデンサ等を接続しても誤差が少なくなり,外部に繋がる素子の選択範囲を広げます.

2つのコンパレータは,同じ抵抗値からなるR3,R4,R5の抵抗分圧で生成したしきい値を用います.具体的に,コンパレータ1は,Threasの電圧と「VTH1=2/3*Vcc」のしきい値電圧を比較します.コンパレータ2は,Triggerの電圧と「VTH2=1/3*Vcc」のしきい値電圧を比較します.コンパレータ1は「R」から後段へ,コンパレータ2は「S」から後段へデジタル信号を伝えます.VctrlとGND間には,VTH1とVTH2のしきい値を安定にするためコンデンサを接続します.しきい値電圧を変えたいときはVctrlに外部から電圧を加えて調整します.

VTH1(Threasの電圧)とVTH2(Triggerの電圧)を比較して,後段に信号を伝える.

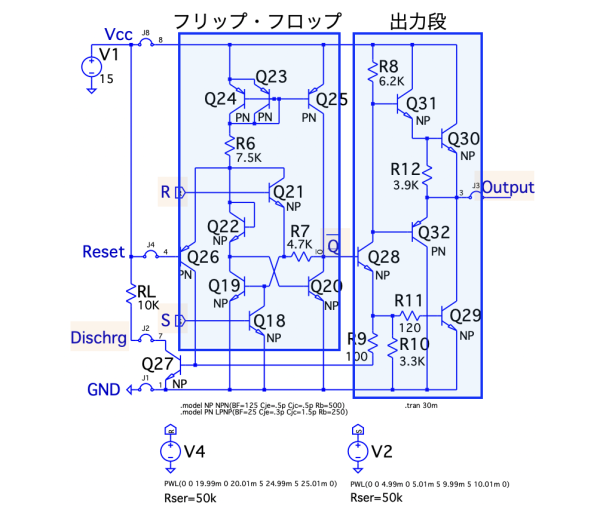

図3は,図2の後段回路となるフリップ・フロップと出力段を書き直した回路です.コンパレータの出力である「R」と「S」の信号はQ21とQ18を通り,たすき掛けしたQ19とQ20のフリップ・フロップに伝わります.フリップ・フロップの出力は,Q20のコレクタとなり,出力段の入力となるQ28のベースにデジタル信号を伝えます.Q28のON/OFFは,OutputとDischrgへ同相で伝わります.

Dischrgには負荷抵抗10kΩを接続している.

図3のResetは,Vccへ接続しています.この接続のとき,Q26がOFFとなり「R」や「S」に応じたフリップ・フロップの信号が出力段に伝わります.Resetが0VになるとQ26がONして「R」や「S」より優先になりOutputとDischrgはLowとなります.OutputのLowの電圧は,Q29の飽和電圧で決まります.図1のようにOutputに負荷がついていないときは飽和電圧が低くなるので0Vに近づきます.

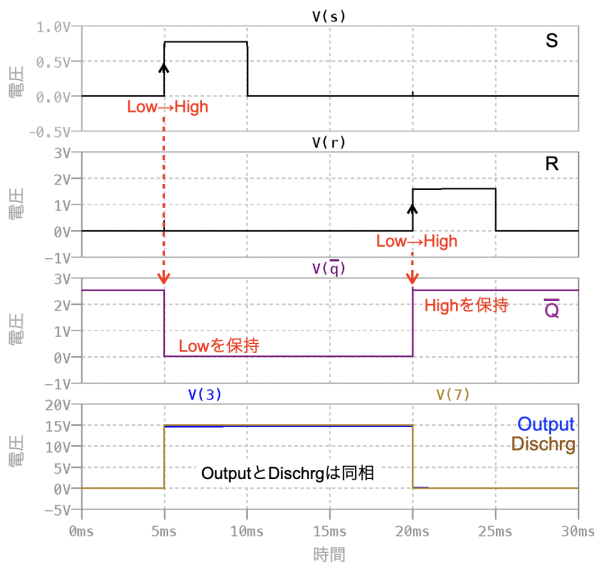

図4は,図3のフリップ・フロップと出力段をシミュレーションした波形になります.上からSの波形,Rの波形,フリップ・フロップの出力波形,OutputとDischrgの波形となります.「S」がLowからHighにセットするとフリップ・フロップの出力は,Lowを保持します.その後「R」をLowからHighにするとフリップ・フロップの出力は,Highを保持することが分かります.また,OutputとDischrgは同相で動いていることが分かります.

図5は,555タイマICのブロック図です.コンパレータ1,コンパレータ2,しきい値電圧を作るR3,R4,R5の直列抵抗,フリップ・フロップ,出力段と端子(Vcc,Threas,Vctrl,Trigger,Dischrg,GND)をまとめました.

555タイマICの動作は,周辺回路により「双安定モード」,「単安定モード」,「無安定モード」の3つの回路動作を作れます.次に,3つのモードについて,シミュレーション後の波形を用いながら解説します.

●双安定モードの回路動作

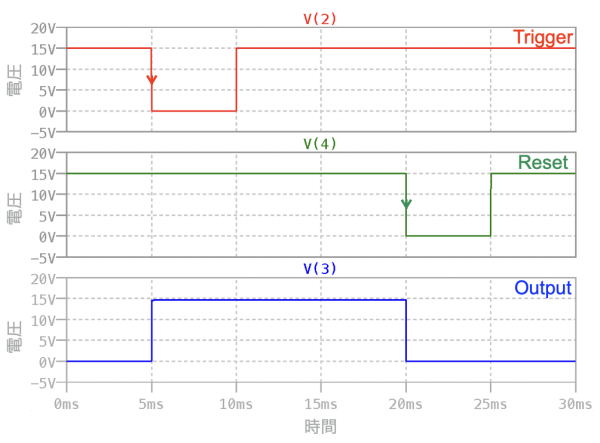

図6は,555タイマICの双安定モードをシミュレーションする回路です.双安定モードはTriggerとResetを入力としたフリップ・フロップとして動作します.コンパレータ1は,Outputに影響しないようにThreasをGNDに接続します.Vctrlは,コンデンサ(ここではC2=0.01μF)を接続してコンパレータのしきい値電圧を安定にします.Dischrgはオープンにして使いますが,シミュレーションではオープンにできないのでGNDに接続しています.

Reset,Trigger,Outputの波形を確認する.

図7は,図6のシミュレーション結果です.上段がTrigger,中段がReset,下段がOutputの波形です.TriggerをHighからLowにセットするとOutputはHighを保持します.そしてResetをHighからLowにするとOutputはLowを保持するフリップ・フロップとなります.

Triggerを0VにセットするとOutputがHigh,Resetを0VにセットするとOutputがLow.

●単安定モードの回路動作

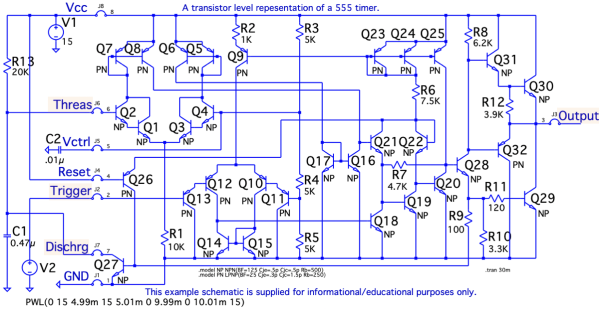

図8は,555タイマICの単安定モードをシミュレーションする回路です.

単安定モードは,式1のC1とR13の時定数で決まる時間だけ遅延時間を発生します.周辺回路は,ThreasとDischrgがC1に接続します.

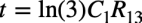

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

図9は,図8のシミュレーション結果です.上段がTrigger,中段がDischrg(Threasと同じ),下段がOutputの波形です.「t=0ms」では,コンデンサに充電されなので,Dischrgは,0Vです.また,,「t=0ms」では,Triggerが15Vで,Resetが回路上でVccの15Vに接続しているので,図7の双安定モードの「t=0ms」と同じ状態となり,OutputはLowとなります.

Dischrgは,Outputと同相なので,C1を放電するモードとなりLowを保持します.この状態から「t=5ms」でTriggerを0VにセットするとOutputは,Highとなり,Dischrgからの放電が停止します.そして中段の波形のように「t=5ms」からC1へ充電が始まり,Threas(Dischrgと同じ)の電圧は上昇します.

C1の充電電圧が「2/3*Vcc=10V」と交差するとコンパレータ1の出力が切り替わり,OutputとDischrgは,再びLowになるのでC1が放電となります.この動作によりOutputは,式1で決まる時間だけHighとなるタイマ動作になります.具体的な遅延時間は「C1=0.47μF」,「R13=20kΩ」なので,式1より「t=10.3ms」となります.

式1で決まる時間だけOutputはHighになる.

●無安定モードの回路動作

図10は,555タイマICの無安定モードをシミュレーションする回路です.

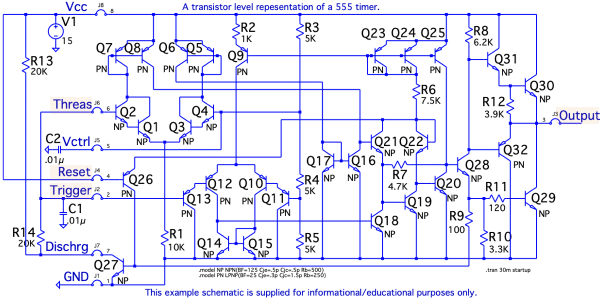

無安定モードは,Outputが式2の発振周波数で矩形波の発振波形となります.

・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・(2)

矩形波のHighの時間は式3となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

Lowの時間は式4となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

ThreasとTriggerは,C1に接続します.DischrgはR14を介してC1を放電します.

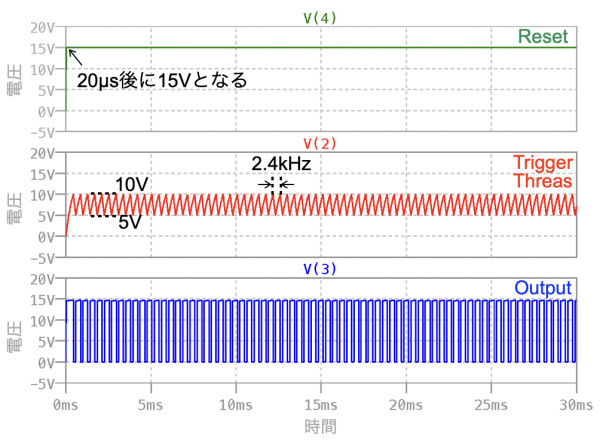

図11は,図10のシミュレーション結果です.上段がReset,中段がTrigger(Threasと同じ),下段がOutputの波形です.過渡解析は「.tran 30m startup」であり,startupオプションがあると電源電圧は,20μs後に15Vとなります.

中段のC1の電圧は5Vと10V間で充放電を繰り返す.

上段のResetは,Vccに接続しているので電源電圧の立ち上がりと同じになります.コンパレータ1のしきい値は「2/3*Vcc=10V」,コンパレータ2のしきい値は「1/3*Vcc=5V」となります.

中段のTrigger(Threasと同じ)の波形は,C1の電圧です.電源電圧が立ち上がるとR13とR14を介してC1へ充電します.C1の電圧が高くなってコンパレータ1のしきい値である10Vと交差するとOutputはLowとなります.このとき,Dischrgは,Outputと同相なのでR14を介してC1から放電を開始します.放電の電圧は,Triggerの電圧となり,C1の電圧が低くなってコンパレータ2のしきい値である5Vと交差するとOutputはHighとなりDischrgは放電を停止して再びC1へ充電を始めます.このようにC1は5Vと10Vの間で充放電を繰り返す発振となり,その発振に同期してOutputは矩形波の発振になります.具体的な発振周波数は,「C1=0.01μF」,「R13=20kΩ」,「R14=20kΩ」ですので式2より「f=2.4kHz」となります.OutputのHighの時間は式3より「tH=277μs」,Lowの時間は式4より「tL=139μs」になります.

●無安定モードの発振回路のシミュレーション

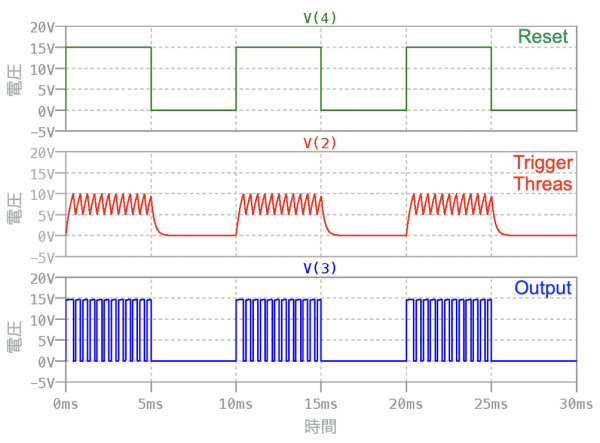

図1は,Educationalフォルダにある「NE555.asc」(ドキュメント\LTspiceXVII\examples\Educational\NE555.asc)です.図1の回路は,無安定モードの発振回路で,図10の回路にReset信号を加えたものです.Reset信号は,5ms間をHigh,その後,5ms間をLowと繰り返します.

図12は,図1のシミュレーション結果です.Reset信号をLowにするとOutputは,ThreasやTriggerより優先されて,Lowになります.なので,Reset信号のHigh区間は発振し,Low区間は発振が停止します.この動作によりOutputは発振している区間と停止する区間がある間欠の発振波形となります.

OutputはResetに同期して発振と停止を繰り返す.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice6_044.zip

●データ・ファイル内容

NE555.asc:図1の回路

NE555.plt:図1のプロットを指定するファイル

555_FF_OutputStage.asc:図3の回路

555_FF_OutputStage.plt:図3のプロットを指定するファイル

NE555_Bistable.asc:図6の回路

NE555_Bistable.plt:図6のプロットを指定するファイル

NE555_Monostable.asc:図8の回路

NE555_Monostable.plt:図8のプロットを指定するファイル

NE555_Astable.asc:図10の回路

NE555_Astable.plt:図10のプロットを指定するファイル

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs

(8) オームの法則から学ぶLTspiceアナログ回路入門アーカイブs