ひずみが少ない正弦波発振回路

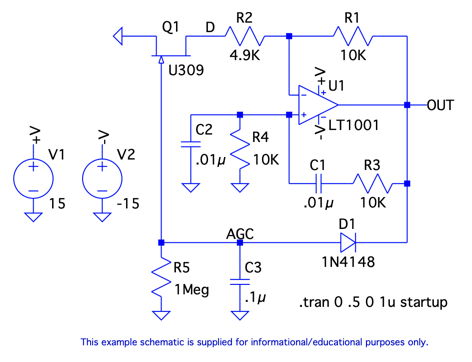

図1は,AGC(Auto Gain Control)付きのウィーン・ブリッジ発振回路です.この回路は発振が成長して落ち着くと,正側と負側の発振振幅が一定になります.そこで,発振振幅が一定を表す式は,次の(a)~(d)のうちどれでしょうか.

(a) ±(VGS-VD1)

(b) ±VD1

(c) ±(1+R2/R1)VD1

(d) ±(1+R2/(R1+RDS))VD1

ここで,VGS:Q1のゲート・ソース電圧,VD1:D1の順方向電圧,RDS:Q1のドレイン・ソース間の抵抗

図1のD1は,OUTの電圧が負になったときダイオードがONとなるスイッチです.D1がONのときのOUTの電圧を検討すると分かります.

図1は,LTspice EducationalフォルダにあるAGC付きウィーン・ブリッジ発振回路です.この発振回路は,Q1のゲート・ソース電圧によりドレイン・ソース間の抵抗が変化して発振を成長させたり抑制したりします.また,AGCにより,Q1のゲート・ソース電圧をコントロールして発振を継続するために適したゲインへ自動調整します.発振が落ち着いたときのQ1のゲート・ソース電圧は,コンデンサ(C3)で保持され,ドレイン・ソース間の抵抗は一定になります.

負側の発振振幅の最大値は,ダイオード(D1)がONしたときで,Q1のゲート・ソース間電圧からD1の順方向電圧を減じた「VGS-VD1」となります.正側の発振振幅の最大値は,D1がOFFのときです.しかし,C3によりQ1のゲート・ソース間は保持され,発振を継続するために適したゲインと最大振幅の条件を保っています.この動作により正側の発振振幅の最大値は負側の最大値の極性が変わった「-(VGS-VD1)」となります.以上より,発振が落ち着いたときの振幅は,(a) ±(VGS-VD1)となります.

●ウィーン・ブリッジ発振回路について

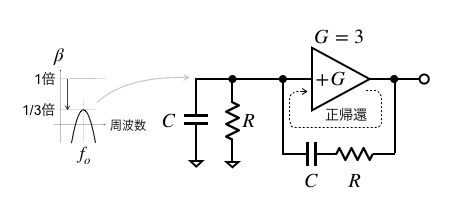

図2は,ウィーン・ブリッジ発振回路の原理図を示します.ウィーン・ブリッジ発振回路は,コンデンサ(C)と抵抗(R)からなるバンド・パス・フィルタ(BPF)とG倍のゲインを持つアンプで正帰還ループを構成した発振回路となります.

CとRによる帰還率(β)は,式1のBPFの中心周波数(fo)でゲインが1/3倍になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

正帰還の発振を継続させるための条件は,ループ・ゲインが「Gβ=1」です.なので,アンプのゲインは「G=3」に設定します.図1ではQ1のドレイン・ソース間の抵抗(RDS)を約100ΩになるようにAGCが動作し,OPアンプ(U1)やR1,R2,RDSからなる非反転アンプのゲインが「G=1+R1/(R2+RDS)=3」になるように動作しています.発振周波数や帰還率の詳しい計算は「LTspiceアナログ電子回路入門 ―― ウィーン・ブリッジ発振回路が適切に発振する抵抗値はいくら?」を参照してください.

●AGC付きウィーン・ブリッジ発振回路のシミュレーション

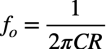

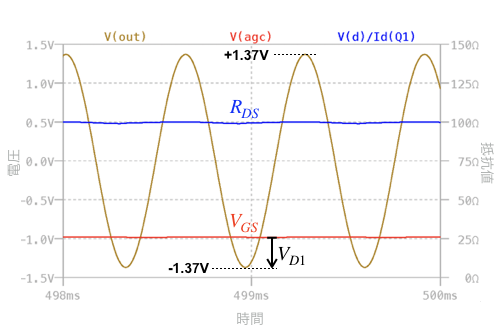

図3は,図1を過渡解析でシミュレーションした結果です.図3は時間0sからのOUTの発振波形の推移,Q1のVGSの推移(AGCラベルの電圧),Q1のドレイン電圧をドレイン電流で除算したドレイン・ソース間の抵抗(RDS)の推移をプロットしました.

図3の0s~20ms付近までQ1のVGSは,0Vです.Q1は,NチャネルJFETなので「VGS=0V」のときONとなり,ドレイン・ソース間の抵抗が「RDS=54Ω」となります.このとき,回路のゲインは「G=1+R1/(R2+RDS)=3.02」となり,発振条件のループ・ゲインが1より大きい「Gβ>1」となるため発振が成長します. 発振が成長するとD1がONし,VGSはC3とR5で積分した負の電圧になります.VGSが負の電圧になるとNチャネルJFETに流れる電流が小さくなりRDSが大きくなります.この動作により回路のゲインが「G=3」になる「RDS=100Ω」の条件に落ち着き,負側の発振振幅の最大値は「VGS-VD1」となります.正側の発振振幅のときD1はOFFとなり,C3によりQ1のゲート・ソース間は保持されて発振を継続するために適したゲインと最大振幅の条件を保ちます.このため正側の発振振幅の最大値は「-(VGS-VD1)」となります.

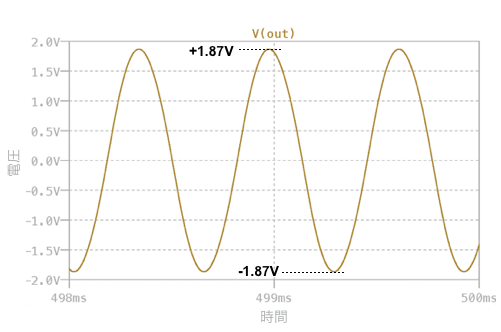

図4は,図3の時間軸を498ms~500ms間の拡大したプロットです.

図4は,時間軸を拡大したプロットのため,OUTの発振波形が正弦波になっています.負側の発振振幅の最大値は,約「VGS=-1V」からD1がONする順方向電圧「VD1=0.37V」だけ下がった電圧となります.正側の最大振幅は,負側の電圧の極性が変わった値なので,発振振幅が「±(VGS-VD1)=±1.37V」となります.

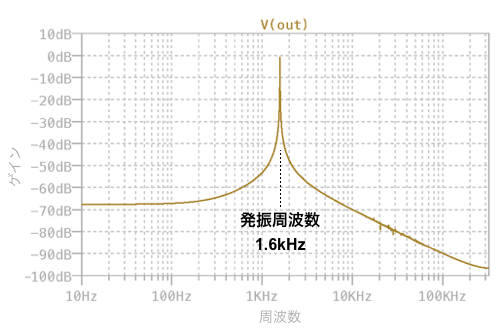

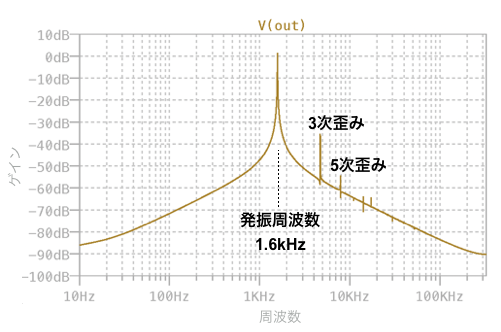

図5は,図3のOUTの発振波形をFFTした結果です.発振周波数は式1の「R=10kΩ,C=0.01μF」としたときの周波数「fo=1.6kHz」となり,高調波ひずみが少ない正弦波の発振であることが分かります.

●AGCにコンデンサやJFETを使わない回路

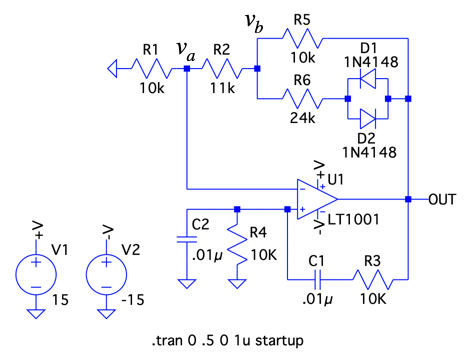

図1のAGCは,コンデンサやNチャネルJFETが必要でした.しかし,図6のようにダイオード(D1とD2)のON/OFFを使って回路のゲインを「G=3」に自動で調整するウィーン・ブリッジ発振回路も使われています.ここでは,この回路のゲイン設定と発振振幅について検討します.

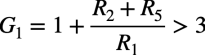

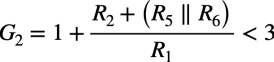

図6の回路でD1とD2がOFFとなる小さな発振振幅のときは,発振を成長させるために回路のゲインを「G1>3」にします.これより式2の条件が成り立ちます.図6では回路の抵抗値より「G1=3.1」に設定しました.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

発振が成長してD1とD2がONするOUTの電圧になると,発振振幅を抑制するために回路のゲインを「G2<3」にします.D1とD2のオン抵抗を0Ωと仮定して計算を簡単にすると式3の条件となります. 図6では回路の抵抗値より「G2=2.8」に設定しました.

・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・(3)

次に発振振幅について検討します.発振を継続させるには「G=3」の条件なので,OPアンプの反転端子の電圧をvaとすると,発振振幅voutとの関係は式4となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

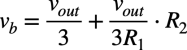

また,R2とR5の接続点の電圧をvbとすると,その電圧はvaにR2の電圧効果を加えた電圧なので,式5となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

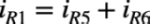

発振が落ち着いているとき,R1の電流は,R5とR6の電流を加えた値なので式6となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

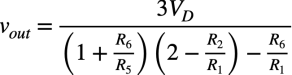

iR1,iR5,iR6の各電流を式4と式5の電圧と回路の抵抗からオームの法則で求め,式6へ代入して整理すると発振振幅は式7となります.ここでVDはD1とD2がONしたときの順方向電圧です.

・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・(7)

図6のダイオードと図1のダイオードは,同じダイオードなので,順方向電圧を図4から求まる「VD=0.37V」とし,回路の抵抗値を用いて式7の発振振幅を求めると「±1.64V」と概算できます.

●AGCにコンデンサやJFETを使わない回路のシミュレーション

図7は,図6のシミュレーション結果で,OUTの電圧をプロットしました.OUTの発振振幅は正弦波の発振で出力振幅は「±1.87V」となり,式7を使った概算に近い出力電圧となります. 実際の回路では,R2の構成に可変抵抗を加えた抵抗とし,発振振幅を調整すると良いと思います.

発振振幅は±1.87V.

図8は,図7のOUTの発振波形をFFTした結果です.発振周波数は式1の「R=10kΩ,C=0.01μF」としたときの周波数「fo=1.6kHz」となります.図5の結果と比べると3次高調波や5次高調波のクロスオーバひずみがありますが,図1のコンデンサとNチャネルJFETを使わなくても実用的な正弦波発振回路となります.

ウィーン・ブリッジ発振回路は,発振振幅を制限する回路を入れないと電源電圧付近まで発振が成長して,波の頂点がクリップしたような発振波形になります.図1や図6のようにAGCを用いた回路で発振振幅を制限すると,ひずみが少ない正弦波発振回路となります.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice6_026.zip

●データ・ファイル内容

Wien.asc:図1の回路

Wien.plt:図1のプロットを指定するファイル

Wein2.asc:図6の回路

Wein2.plt:図6のプロットを指定するファイル

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs

(8) オームの法則から学ぶLTspiceアナログ回路入門アーカイブs