弛張発振回路

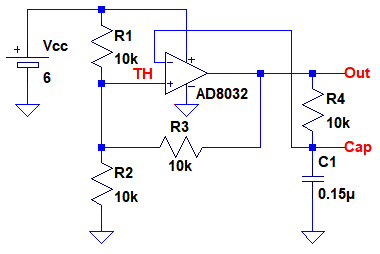

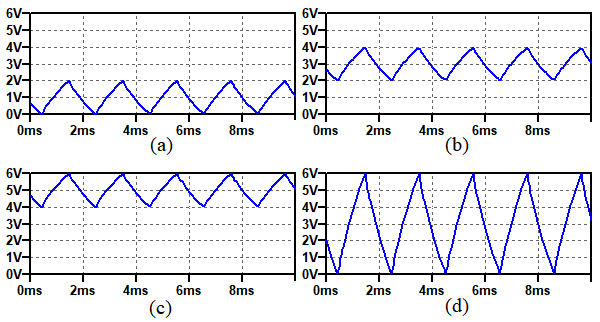

図1は,電源電圧からGNDレベルまでフル・スイング可能な,レール・トゥ・レール出力OPアンプを使用した,弛張発振回路です.電源は6Vの単電源となっています.この発振回路のCap端子の波形として正しいのは,図2の(a)~(d)のどれでしょうか.

電源電圧は6Vとなっている.

(a)の波形 (b)の波形 (c)の波形 (d)の波形

図1のOPアンプは+入力端子に出力から帰還がかけられているため,ヒステリシス付きのコンパレータとして動作します.そのスレッショルド電圧がいくつになるかを考えれば,どの波形が正しいかが分かります.

図1のOPアンプの+入力端子の電圧は,R1~R3で決まり,OPアンプの出力電圧によって変化します.OPアンプの出力が電源電圧と同じとき,+入力端子の電圧は4Vになります.また,出力がGND電圧と同じとき,+入力端子の電圧は2Vになります.つまり,ヒステリシス・コンパレータとして動作するときのスレッショルド電圧は4Vと2Vです.Cap端子の電圧が2Vになったときと4Vになったときに状態が変化します.そのような波形となっているのは(b)なので,正解は(b)となります.

●ヒステリシス・コンパレータの動作

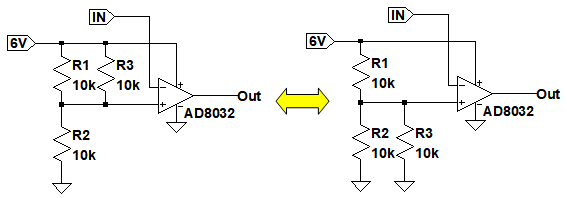

図1のOPアンプはヒステリシス・コンパレータとして動作し,2つのスレッショルド電圧があります.一方,出力から+入力に帰還する抵抗(R3)が無い場合は,通常のコンパレータとして動作し,そのスレッショルド電圧はR1とR2の分圧比で決まります.図1の場合はR1,R2ともに10kΩのため,電源電圧の半分の3Vになります.

図3は,ヒステリシス・コンパレータの動作を説明するための模式図です.

入力電圧によって,左と右の状態に変化する.

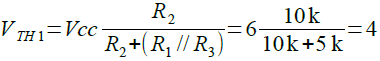

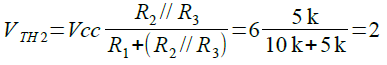

入力端子(IN)の電圧が低いとき,出力はハイ・レベルとなり,電源電圧と同じ電圧になります.そのため,図3の左側の等価回路となり,スレッショルド電圧は式1のように,4Vになります.

・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・(1)

入力電圧が4Vを越えると出力はGNDレベルとなるため,図3の右側の等価回路となります.このときのスレッショルド電圧は式2のように2Vになります.

・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・(2)

そのため,入力電圧が2Vに下がるまでは出力はGNDのままです.そして入力電圧が2Vよりも小さくなると出力がハイレベルとなり,再び図3の左の状態になります.

●ヒステリシス・コンパレータのシミュレーション

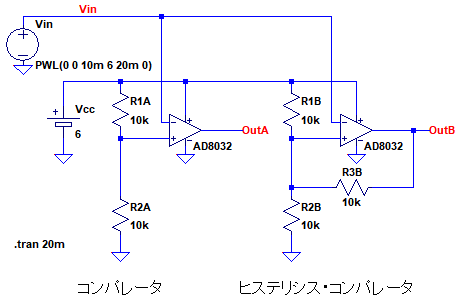

図4は,OPアンプを使用したコンパレータとヒステリシス・コンパレータの動作をシミュレーションするための回路です.どちの回路も-入力端子はVinに接続されています.Vinは0Vから電圧が上昇し,10msec後に6Vになった後,20msec後に再び0Vになるように設定されています.

Vinは0Vから電圧が上昇し,10msec後に6Vになった後,20msec後に再び0Vになる.

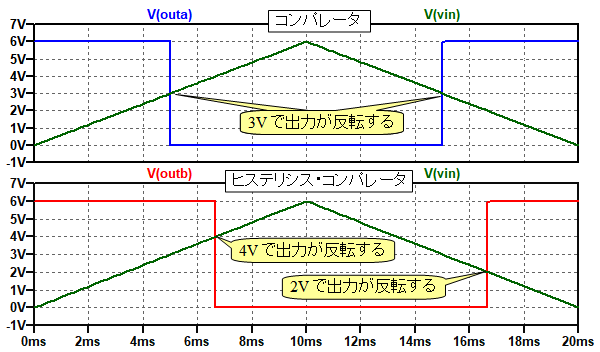

図5がコンパレータとヒステリシス・コンパレータのシミュレーション結果です.上段がコンパレータのシミュレーション結果で,下段がヒステリシス・コンパレータのシミュレーション結果です.

ヒステリシス・コンパレータの出力が反転するのはVinが4Vと2Vのとき

コンパレータの出力(OutA)はVinの電圧が低いときはハイ・レベル(6V)となっており,Vinが3Vになるとロー・レベル(0V)になっています.Vinが小さくなっていくときも3Vで出力が反転しています.一方,ヒステリシス・コンパレータの出力(OutB)は,Vinの電圧が低いときはハイ・レベル(6V)となっています.また,出力がロー・レベル(0V)になるのは,Vinが4Vになったときです.さらに,Vinが小さくなっていくときに出力が反転するのはVinが2Vのときになっています.このように,入力電圧が上昇するときと下降するときで,スレッショルド電圧が異なることを「ヒステリシスがある」と言います.

●弛張発振回路のシミュレーション

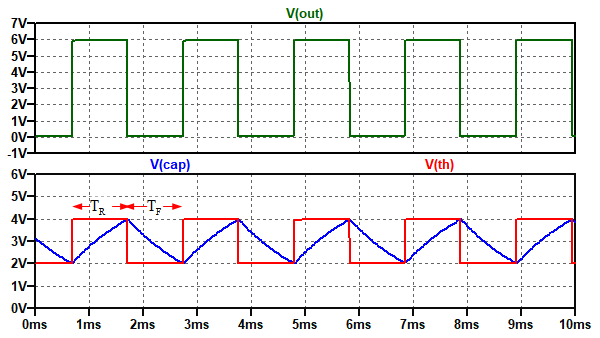

図6は,図1の弛張発振回路のシミュレーション結果です.Cap端子の電圧は,2Vと4Vの間で変化をしています.Cap端子は,OPアンプの-入力端子に接続されているため,最初にCap端子の電圧が低いとき,OPアンプ出力がハイレベルとなります.また,コンデンサ(C1)は,抵抗(R4)で充電されます.そのため,Cap端子の電圧は,上昇していきます.

Cap端子の電圧が4Vに達するとOPアンプの出力は,GNDレベルになります.また,スレッショルド電圧は,2Vに変化します.OPアンプの出力がGNDになるため,C1がR4によって放電されるため,電圧は,下降していきます.そして,Cap端子の電圧が2Vになると再びOPアンプの出力は,ハイレベルになります.これを繰り返すことで発振することになります.

Cap端子の電圧は2Vと4Vの間で変化している.

●弛張発振回路の発振周波数

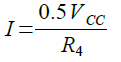

C1は,抵抗により充放電されます.なので,Cap端子の電圧波形は直線ではありません.直線とみなすことで,簡易的に発振周波数を計算することができます.Cap端子の電圧が電源電圧(Vcc)の半分(3V)のとき,C1の充放電電流(I)は,その電圧をR4で割ったものになります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

その電流でC1が充電されるとすると,Cap端子電圧の立ち上がり時間(図6のTR)は式4で計算することができます.

・・・・・(4)

・・・・・(4)

TFも同じ時間になるため,1周期の時間は2msecとなり発振周波数は500Hzと計算できます.図6のシュミレーション結果も,式4とほぼ一致しています.

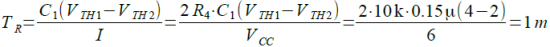

●正負電源を使用した弛張発振回路

図7は,LTspiceのサンプルファイル(ドキュメント\LTspiceXVII\examples\Educational\relax.asc)です.中点電圧を作る必要がないため,単電源を使用した図1の回路よりも抵抗が1つ少なくなっています.

単電源を使用した図1の回路よりも抵抗が1つ少ない.

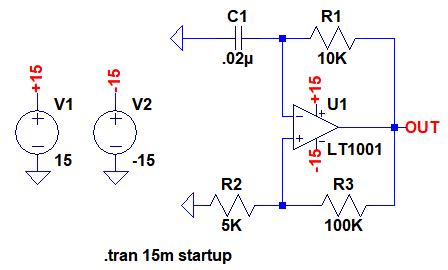

図8は,図7のシミュレーション結果です.発振周波数が高いため,OPアンプの出力スルー・レートの影響を受けて出力が三角波となっています.これはC1を大きくして周波数を下げることで矩形波に近づいていきます.

OPアンプの出力スルー・レートの影響で出力が三角波となっている.

以上,弛張発振回路について解説しました.正負電源を使用した弛張発振回路の発振周波数に関しては,LTspiceアナログ電子回路入門・アーカイブs「弛張発振回路の発振周波数が最も低くなる抵抗値はいくつ?」を参照してください.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice6_021.zip

●データ・ファイル内容

Relax_SPS.asc:図1の回路

comparator.asc:図4の回路

relax.asc:図7の回

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs

(8) オームの法則から学ぶLTspiceアナログ回路入門アーカイブs