位相シフト発振回路

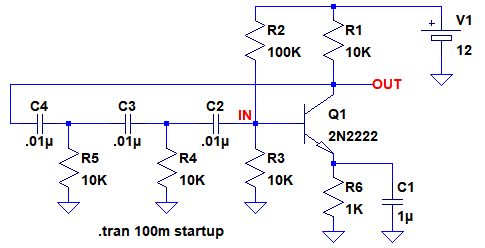

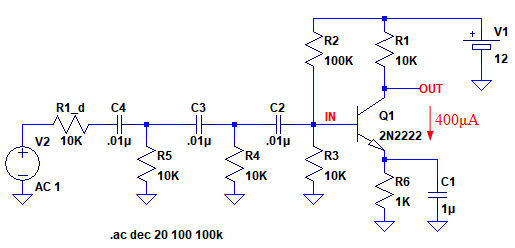

図1は,エミッタ接地増幅回路を使用した位相シフト発振回路です.コンデンサのC2,C3,C4と抵抗のR3,R4,R5で位相シフト回路を構成しています.C2,C3,C4の値(C)が0.01μFで,R3,R4,R5の値(R)が10kΩです.この回路の発振周波数[1/(2πCR)]の説明として正しいのは次の(a)~(d)のどれでしょうか.

(a) 位相シフトの段数が足りないため発振しない

(b) 発振周波数は1/(2πCR)と同じ

(c) 発振周波数は1/(2πCR)よりも高い

(d) 発振周波数は1/(2πCR)よりも低い

エミッタ接地増幅回路は,出力の位相が入力とは反転します.そのため,図1の回路が発振するためには,入力に帰還される信号の位相が,出力とは180°ずれている必要があります.位相シフト回路に使用している,抵抗とコンデンサを組み合わせたハイパス・フィルタの,周波数と位相の関係を考えれば,答えが分かります.

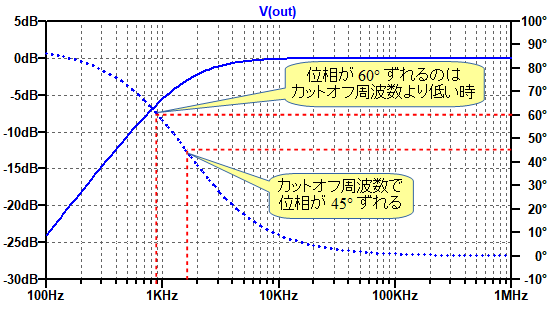

抵抗(R)とコンデンサ(C)を組み合わせた1次のハイパス・フィルタは,入力周波数がカットオフ周波数である1/(2πCR)と同じとき,出力信号の位相ずれは45°になります.図1の回路はこのフィルタを三段縦続接続して位相シフト回路を構成しています.そのため,位相が180°ずれるためには,一段あたり60°ずれる必要があります.1次のハイパス・フィルタで位相が60°ずれるのは,カットオフ周波数よりも低い周波数のときです.そのため,図1の回路は,カットオフ周波数の1/(2πCR)よりも低い周波数で発振します.

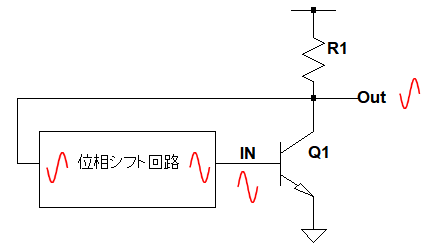

●エミッタ接地増幅回路を使用した位相シフト発振回路の原理

図2は,エミッタ接地増幅回路を使用した,位相シフト発振回路の動作を説明するための原理図です.エミッタ接地増幅回路の出力(OUT端子)の信号は,入力(IN端子)信号と位相が反転します.このOUT端子の信号を位相シフト回路に入力し,位相を180°ずらして反転します.この反転した信号を再びIN端子に入力すると,図2の回路は正帰還となり,発振することになります.

位相シフト回路で位相を180°ずらして反転する.

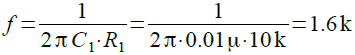

●RCハイパス・フィルタの周波数特性

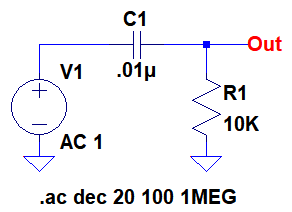

図1の位相シフト回路は,1次のRCハイパス・フィルタを3段縦続接続して構成されています.そのため,位相シフト回路で位相を180°ずらすためには,一段あたり,60°位相がずれる必要があります.図3は1次のRCハイパス・フィルタをシミュレーションするための回路です.この回路のカットオフ周波数(f)は式1で表されます.

・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・(1)

カットオフ周波数は1/(2πC1R1)で表される.

図4は,図3の1次のRCハイパス・フィルタのシミュレーション結果です.カットオフ周波数が1.6kHzのとき,位相は45°ずれていることが分かります.位相が60°ずれるのは,カットオフ周波数よりも低く,940Hz程度となっています.

位相が60°ずれるのは,カットオフ周波数よりも低い.

●位相シフト回路の周波数特性

図5は,図1の発振回路のループを切断し,位相シフト回路の周波数特性をシミュレーションするための回路図です.

R1_dは,エミッタ接地増幅回路の出力抵抗を表している.

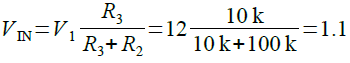

入力電圧源のV2に直列に接続されているR1_dは,エミッタ接地増幅回路の出力抵抗(負荷抵抗)を表しています.この回路でIN端子の直流電圧は式2のように,1.1Vになります.

・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・(2)

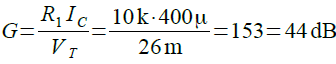

Q1のベース・エミッタ間電圧を0.7Vとすると,R6の電圧降下は0.4Vとなり,コレクタ電流は約400μAになります.エミッタ接地増幅回路のゲイン(G)は式3で計算することができます.図5の定数を代入すると44dBとなります.(VTは熱電圧で常温で26mV)

・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・(3)

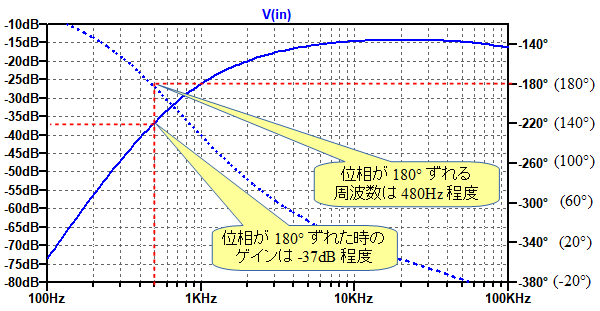

図6は,図5の周波数特性のシミュレーション結果です.右側の位相の数字が-360°加算された値となっているため,カッコ内にわかりやすい数字を記載しています.このシミュレーション結果によると,位相が180°ずれる周波数は,480Hz程度で,そのときのゲインが-37dB程度です.そのため,この回路が発振するために必要な,エミッタ接地増幅回路のゲインは37dB以上となります.式3の結果からエミッタ接地増幅回路のゲインは44dBとなっており,発振条件を満たしていることが分かります.

位相が180°ずれる周波数は480Hzでそのときのゲインは-37dB.

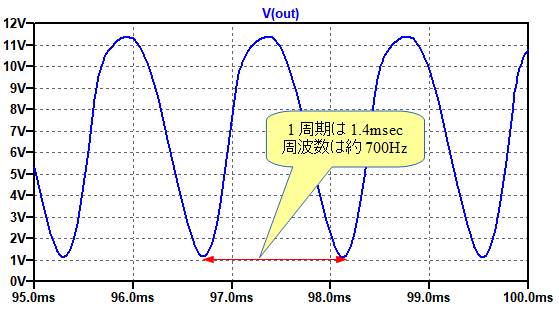

図7は,図1の回路のシミュレーション結果で最後の5msecを表示しています.発振周期は1.4msecとなっており,発振周波数は約700Hzです.図6で位相が180°ずれる周波数よりは若干高いですが,カットオフ周波数(1/(2πCR=1.6kHz)よりも低い周波数で発振していることが分かります.

カットオフ周波数(1/(2πCR=1.6kHz)よりも低い周波数で発振している.

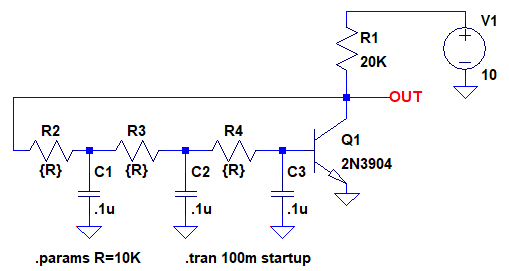

図1はLTspiceのサンプル・ファイル(ドキュメント\LTspiceXVII\examples\Educational\phaseshift.asc)です.また,図8は同じフォルダにあるサンプルファイルのphaseshift2.ascです.図1は,ハイパス・フィルタ型の位相シフト回路を使用しています.それに対し,図8は,ローパス・フィルタ型の位相シフト回路を使用しています.なお,図8の回路では一段目のローパス・フィルタのカットオフ周波数は1/(2π(R1+R2)C1)となります.ここで,R2は本来必要のない抵抗です.

ローパス・フィルタ型の位相シフト回路を使用している.

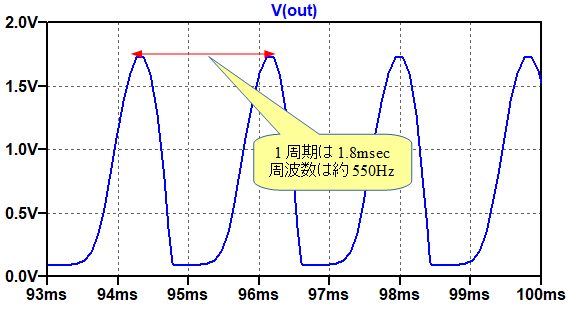

図9は,図8のシミュレーション結果です.発振周波数は550Hz程度となっています.ローパス・フィルタ型の位相シフト回路を使用した場合,位相が60°ずれる周波数は,カットオフ周波数よりも高いため,発振周波数はカットオフ周波数よりも高くなります.

発振周波数はカットオフ周波数よりも高くなる.

以上,トランジスタを使用した位相シフト発振回路を紹介しました.位相シフト発振回路は,トランジスタ1個で発振回路を構成できるため,比較的低い周波数用の発振回路として,電子工作などでよく使用されています.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice6_019.zip

●データ・ファイル内容

phaseshift.asc:図1の回路

phaseshift.plt:シミュレーション結果を表示するためのPlot settinngsファイル

phaseshift_AC.asc:図5の回路

phaseshift2.asc:図8の回路

phaseshift.plt:シミュレーション結果を表示するためのPlot settinngsファイル

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs

(8) オームの法則から学ぶLTspiceアナログ回路入門アーカイブs