パワー・オン・ディレイ回路の動作

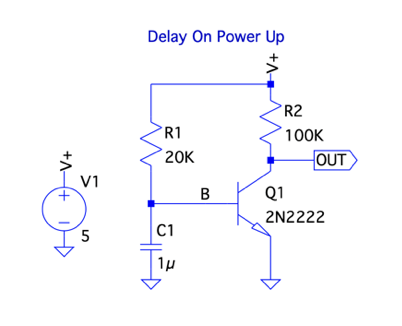

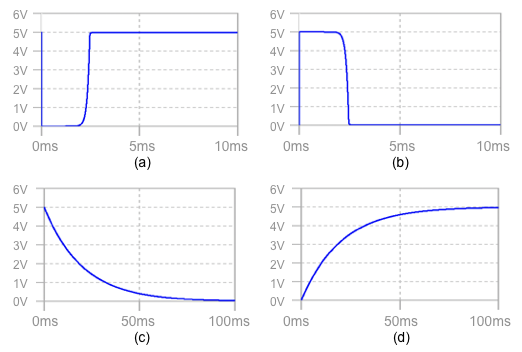

図1は,V1が通常(0s~20μsで0V~5V)に立ち上がったとき,メインの回路が落ち着くまで,立ち上がった時間から遅延させた信号をOUT端子から出力するパワー・オン・ディレイ回路です.OUT端子の波形として正しいのは図2の(a)~(d)のどれでしょうか.

(a)の波形 (b)の波形 (c)の波形 (d)の波形

図1は,V1が急峻(通常)に立ち上がるとR1に流れる電流をC1で充電します.C1の充電電圧はQ1とR2のエミッタ接地アンプの入力電圧となります.OUT端子はエミッタ接地アンプの出力です.この回路内の各電圧の時間推移を検討すると分かります.

図1の回路は以下のように動作します.

・V1が急峻に5Vまで立ち上がると,積分回路によってBの電圧が約0.6Vまで立ち上がるのに遅延時間が発生する

・Q1とR2のインバータにより,Bの電圧が約0.6V以下ならトランジスタはOFFでありOUT端子の電圧はHighに相当する5Vである

・Bの電圧が約0.6V以上ならトランジスタはONしてLowに相当する0V付近の電圧となる

インバータの出力は,HighとLowの2値が短い時間で切り替わるため,(c)と(d)の波形ではなく,(a)と(b)のどちらかです.Bの電圧は電源の立ち上がりから遅れて約0.6Vとなるため,OUT端子の電圧は電源が立ち上がるとHighの5Vです.時間が経過すると積分回路によりBの電圧は緩やかに上昇し,約0.6V以上となるとOUT端子の電圧はLowの0V付近の電圧となります.この波形は(b)となります.

●パワー・オン・ディレイ回路について

パワー・オン・ディレイ回路は,電源が立ち上がったときに回路システムが落ち着くまでメイン回路を停止させる制御信号に使われます.図1のパワー・オン・ディレイ回路はR1とC1で構成する積分回路の遅延時間を利用し,電源が立ち上がった後に設定した時間だけ回路システムを停止させる制御信号を発生します.パワー・オン・ディレイ回路は電源が立ち上がったときしか使わない回路なので,回路システムの消費電力を抑えるために低消費電流であることが求められます.

●動作をシミュレーションする

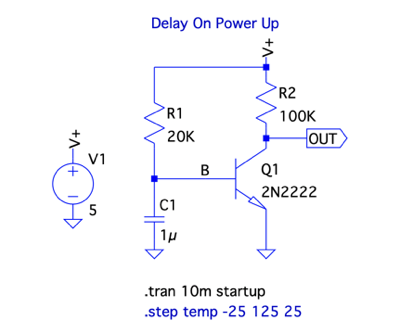

図3は,図1の電源が通常に立ち上がったとき,0sから10ms間の過渡解析をする回路です.「.tran」コマンドの最後にある「startup」は過渡解析のオプションで,このオプションがあるとV1は0s~20μsで0V~5Vへ立ち上がります.「.step」コマンドは後で使うため,ここではコメントアウトにしています.

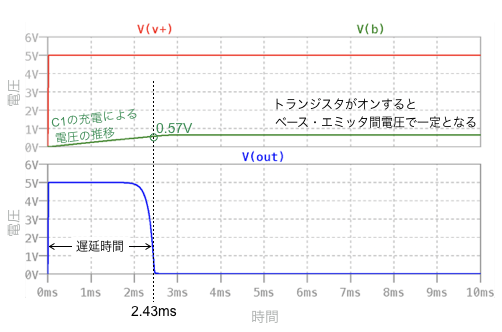

図4は,図3のシミュレーション結果です.上段は電源電圧(V+)とB電圧の時間推移のプロットしました.下段はOUT端子電圧の時間推移のプロットです.

上段は電源電圧とB電圧の時間推移.下段はOUT端子電圧の時間推移.

B電圧はR1とC1からなる積分回路の充電電圧なので,B電圧の時間推移をVB(t)とすると式1となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

ここで,V+=5V,τ=R1C1

2N2222のNPNトランジスタのコレクタ側に100kΩの抵抗負荷を接続したインバータは,ベース電圧が0.57Vを境にOUT端子の論理が切り替わります.式1を用いて図3のVB(t)=0.57Vとなる時間(t)を求めると約2.4msとなり,この時間でOUT端子の電圧は5Vから0V付近に切り替わります.この時間推移が図4のシミュレーション結果から確認できます.以上より,図3のパワー・オン・ディレイ回路は電源電圧が立ち上がった後,2.4ms後にメイン回路の動作を開始させる制御信号を発生します.

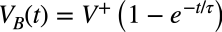

●遅延時間が短くなる温度特性

NPNトランジスタのベース・エミッタ間電圧は周囲の温度が1℃変化すると約-2mV小さくなります.このため,図3のパワー・オン・ディレイ回路は周囲温度が高くなるとQ1がオンするベース電圧が下がるため遅延時間は短くなる温度特性となります.

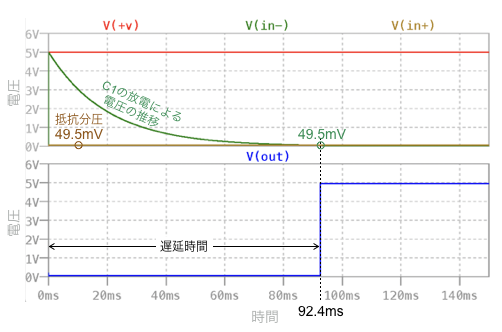

図5は,図3でコメントアウトした「.step temp -25 125 50」を有効にして-25℃,25℃,50℃,125℃の各温度でシミュレーションした結果です.上段はOUT端子電圧の時間推移,下段は消費電流の時間推移をプロットしました.OUT端子電圧は温度が高くなるほどHighからLowへ切り替わる遅延時間が短くなる欠点があり,よい回路とはいえません.

消費電流はQ1がオンするのに必要なベース電流と,そのときのコレクタ電流の合算で約260μAとなります.パワー・オン・ディレイ回路は電源が立ち上がるときしか使わない回路なのでメイン回路が動いているときは無駄な電流になります.パワー・オン・ディレイ回路の消費電流を減らすには回路の工夫が必要になります.

上段はOUT端子電圧の時間推移.下段は消費電流の時間推移.

●コンパレータを使った回路のシミュレーション

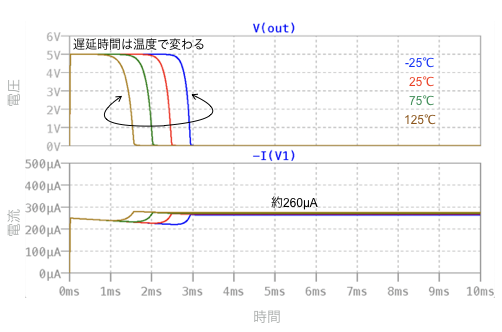

図6は,LTspiceのjigsフォルダにあるパワー・オン・ディレイ回路「1017.asc」を編集した回路です.編集したところはLT1017のデータシートにある応用回路例に合わせてR1=1kΩ,R2=100kΩとしました.部品点数を図3と比べると,トランジスタがLT1017のコンパレータに代わり,1kΩの抵抗1点が増えた回路となります.「.step」コマンドは後で使うため,ここでもコメントアウトにしています.

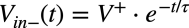

図7は,図6のシミュレーション結果で,上段は,電源電圧(+V)とIN+電圧とIN-電圧の時間推移のプロットです.下段は,OUT端子電圧の時間推移のプロットです.コンパレータの閾値となるIN+の電圧は,電源電圧5Vから100kΩと1kΩで分圧した49.5mVとなります.電源が通常に立ち上がったとき,C1からR3を通してコンデンサは放電し,IN-の電圧がIN+の閾値より小さな電圧になると,OUT端子の電圧はLowからHighへ切り替わるパワー・オン・ディレイ回路となります.

IN-端子の電圧の時間推移をVIN-(t)とすると式2となります.式2を用いてVIN-(t)= 49.5mVとなる時間tを求めると約92.3msとなり,この時間でOUT端子の電圧は0Vから5Vに切り替わります.この時間推移が図7のシミュレーション結果から確認できます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

ここで,V+=5V,τ=R3C1

上段は電源電圧とIN+電圧とIN-電圧の時間推移.下段はOUT端子電圧の時間推移.

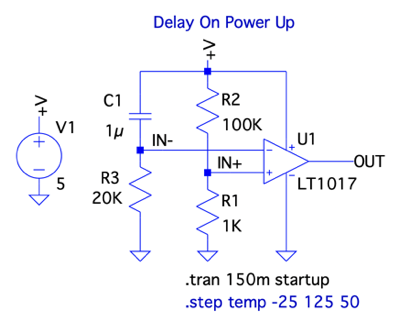

●遅延時間の変化が少ない温度特性

図8は,図6でコメントアウトした「.step temp -25 125 50」を有効にして-25℃,25℃,50℃,125℃の各温度でシミュレーションした結果です.上段はOUT端子電圧の時間推移をプロットしました.下段は消費電流の時間推移をプロットしました.抵抗分圧による閾値は温度が変化しても一定とみなすことができます.このため温度が変化しても遅延時間の変化は少なく,シミュレーションでは差はありません.また放電電圧の時間推移は5Vから49.5mVの広いダイナミックレンジとなり,図5と比べると遅延時間も長くなります.遅延時間の調整はR1とR2の分圧比を変えてIN+の閾値電圧を調整する方法と,C1とR3を調整して放電時間を調整する方法があります.

消費電流はコンパレータの消費電流と電源からR2とR1を通り流れる電流の合算となり約170μAとなります.LT1017のような消費電流が少ないコンパレータを用いれば,図3の消費電流より少なくできます.

上段はOUT端子電圧の時間推移.下段は消費電流の時間推移.

以上解説したように,コンデンサの充放電電圧の時間推移とインバータ或いはコンパレータの閾値を横切るタイミングを使って,電源投入時のパワー・オン・ディレイ回路を作ることができます.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice6_014.zip

●データ・ファイル内容

delay_on_powerup.asc:図3の回路

delay_on_powerup.plt:図3のプロットを指定するファイル

1017_mod.asc:図6の回路

1017_mod.plt:図6のプロットを指定するファイル

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs

(8) オームの法則から学ぶLTspiceアナログ回路入門アーカイブs