静特性から分かるトランジスタの特性

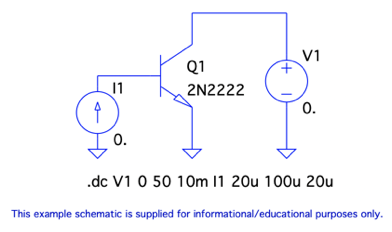

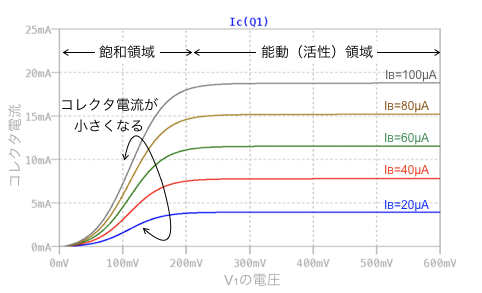

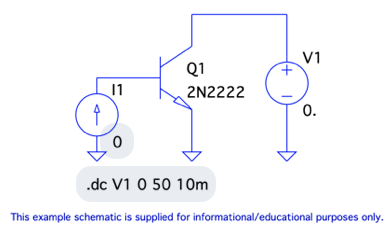

図1は,トランジスタのさまざまな特性が分かる静特性をシミュレーションする回路です.静特性は,ベース電流(I1)を一定のステップで変化させてトランジスタを駆動し,ベース電流ごとにコレクタ・エミッタ間電圧(V1)をスイープして,コレクタ電流(IC1)の変化をプロットします.

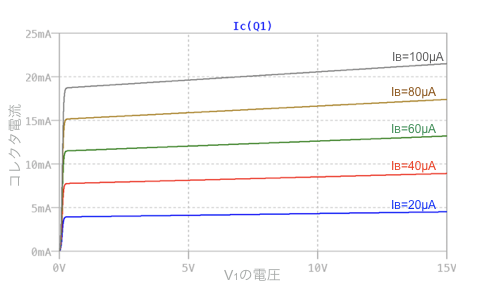

図2が図1のシミュレーションで得られた静特性です.この図2から求められないトランジスタの特性は(a)~(d)のどれでしょうか.

(a)電流増幅率 (b)出力抵抗 (c)飽和電圧 (d)コレクタとエミッタ間の耐圧

(a)電流増幅率は,ベース電流とコレクタ電流の関係です.

(b)出力抵抗は,コレクタからトランジスタ側を見たときの抵抗で,コレクタ電圧とコレクタ電流の関係です.

(c)飽和電圧は,コレクタ電圧が低くなり,電流増幅率が小さくなるときのコレクタ・エミッタ間の電圧です.

(d)コレクタとエミッタの耐圧は,ベースがオープンのときコレクタ・エミッタ間に印加できる最大の電圧です.

(a)~(d)のうち,このプロット上の数値,あるいはその値を使った計算で求められるものを探します.

(a)の電流増幅率は,「コレクタ電流とベース電流の比」ですので,プロット上の数値から計算できます.

(b)の出力抵抗は,「コレクタとエミッタ間の僅かな電圧の変化に対するコレクタ電流の変化」から求められ,オームの法則よりプロット上の数値から計算できます.

(c)の飽和電圧は通常のトランジスタ動作ができず,電流増幅率が極めて小さくなるコレクタ・エミッタ間の電圧ですので,(a)の電流増幅率を用いてコレクタ電流が急激に小さくなる箇所を探すと求まります.

(d)のコレクタとエミッタ間の耐圧は,コレクタとエミッタ間の電圧が高くなるとコレクタ電流が急激に増加する降伏現象(ブレークダウン)であり,SPICEプログラムでは再現できません.よって,解答は(d)のコレクタとエミッタ間の耐圧となります.

トランジスタの特性を調べる測定器にカーブ・トレーサがあります.カーブ・トレーサは,図1と同じ測定が実際のデバイスで測れる測定器で,図2の静特性はカーブ・トレーサのCRT(ブラウン管)にトレースさせます.今回使用する回路「curvetrace.asc」も,カーブ・トレーサをLTspiceで行うイメージだと思います.ここでは,シミュレーションの静特性から求めることができるトランジスタの特性について解説します.

●電流増幅率

トランジスタは,ベースに小さな電流が流れると,コレクタに大きな電流が流れます.コレクタ電流とベース電流の比は,直流のとき式1となり,hFEのことを直流電流増幅率と呼びます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

図2の静特性からhFEを求めるときは式1を使います.式1の分母のベース電流(IB)は,一定のステップで変化させた値なので分かっています.分子のコレクタ電流(IC)は,図2でカーソルを使って調べれば分かります.これよりhFEは計算で求まります

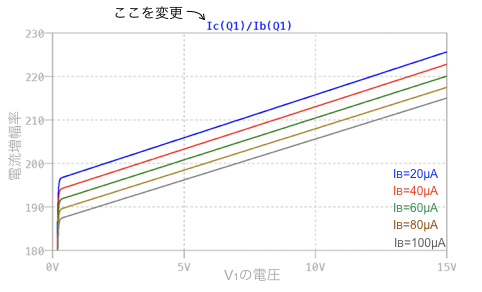

図3は,LTspiceの演算機能を使い,図2のプロットの表示を式1のように「IC(Q1)/IB(Q1)」へ変更したものです.このようにすれば,電卓で計算せずにhFEを簡単に求めることができます.

縦軸は直流電流増幅率のプロットとなる.

●出力抵抗

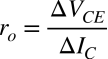

トランジスタは,コレクタ電圧が変化しても,コレクタ電流は変わらず一定になるのが理想です.実際は,図2の静特性のように,コレクタ・エミッタ間の電圧が約1V以上の領域において,プロットは僅かに右上がりになります.右上がりの傾斜は,コレクタとエミッタ間の僅かな電圧の変化でコレクタ電流が変化しているので,抵抗成分があることが分かります.これがコレクタ側からみた出力抵抗であり,オームの法則より式2となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

出力抵抗は,図2の静特性のプロットで2本のカーソルを使ってΔVCEとΔICの変化分を調べ,式2より求まります.出力抵抗はトランジスタの小信号等価回路で使われます.

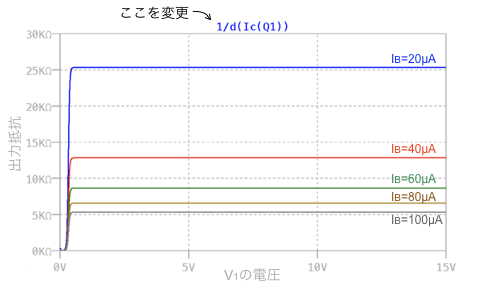

図4は,LTspiceの導関数を使い,図2のプロットの表示を「1/d(IC(Q1))」に変更したものです.d(IC(Q1))の導関数は,図2のプロットの右上がりの傾きを表しており式2の逆数です.このようにプロットの表示を変更すれば簡単に出力抵抗が分かります.

図2の静特性で,ベース電流の小さい方が,コレクタ電流の変化は少なくなります.プロットは,水平に近くなり出力抵抗が大きくなります.逆にベース電流が大きいとプロットは,右上がりの傾斜が増し,出力抵抗が小さくなります.この様子は,図4からも分かり,ベース電流が20μAから100μAに大きくなるにしたがって,出力抵抗は小さくなります.

縦軸はコレクタからみた出力抵抗のプロットとなる.

●飽和電圧

飽和電圧は,コレクタとエミッタ間の電圧が低くなり,通常のトランジスタ動作ができず,電流増幅率が極めて小さくなるときのコレクタとエミッタ間の電圧です.データ・シートの飽和電圧は,VCEsatの記号で表します.

図5は,図2の静特性の横軸を0V~600mV付近を拡大したプロットです.図5では約200mVより低い電圧でコレクタ電流が小さくなり,ベース電流は一定ですから電流増幅率が極端に下がります.この領域を飽和領域と呼び,横軸のコレクタ・エミッタ間電圧が飽和電圧となります.データ・シートでは,電流増幅率が下がるコレクタ電流とベース電流の値を測定条件で決めて,そのときの飽和電圧を記載しています.

●コレクタとエミッタ間の耐圧

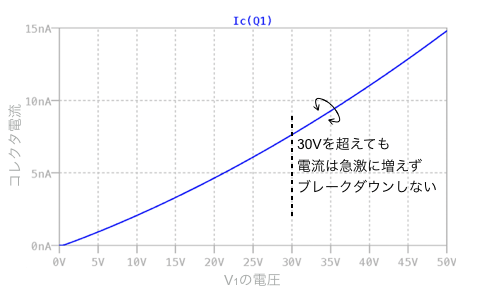

コレクタとエミッタ間の耐圧は,ベースがオープンの状態で,コレクタとエミッタ間の電圧が高くなるとコレクタ電流が急激に増加する降伏現象(ブレークダウン)のことです.データ・シートでは,VCEOの記号で表します.コレクタとエミッタ間の耐圧は,カーブ・トレーサでは測れますが,SPICEプログラムは再現できません.これをシミュレーションで確かめます.

図6は,図1の回路の直流解析の指定を変えた回路です.ベースをオープンとするため,I1の電流源は0Aとします.そうすると,電流源の出力抵抗は無限大で,かつ,流れる電流が0ですから,等価的にベースがオープンの条件となります.また,V1の電圧は,図1のとき15Vのまでですが,更に高い50Vまでシミュレーションするように,「.dc V1 0 50 10m」へ変更しています.

図7は,図6のシミュレーション結果です.2N2222のデータ・シートより,VCEOは30Vですが,シミュレーションでは30Vを超えてもコレクタ電流は急激に増えず15nA以下の微小なコレクタ電流です.このようにシミュレーションでは,ブレーク・ダウンしないため,コレクタとエミッタ間の耐圧は再現できないことが分かります.

30Vを超えてもコレクタ電流は急激に増えず,ブレークダウンしない.

以上,解説した通り,シミュレーションで得た静特性より,電流増幅率,出力抵抗,飽和電圧は,求められますが,コレクタ・エミッタ間の耐圧は再現できません.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice6_002.zip

●データ・ファイル内容

curvetrace.asc:図1の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs

(8) オームの法則から学ぶLTspiceアナログ回路入門アーカイブs