トランジスタの飽和を防止する回路の動作

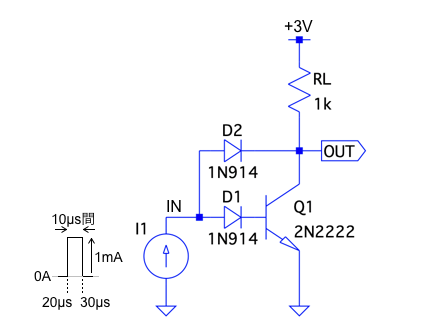

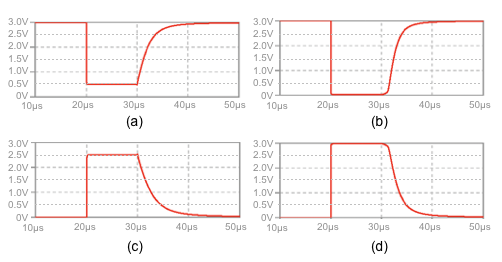

図1は,NPNトランジスタ(Q1)と2つのダイオード(D1,D2)を組み合わせ,負荷抵抗(RL)を接続したトランジスタ飽和防止回路です.この回路は,ディジタル回路で,I1の電流により,OUTの電圧が変わります.I1は,10μs間の振幅が1mAとなる矩形波を入力し,OUT端子の波形をプロットしました(図2).

Q1のベース・エミッタ間電圧を0.7V,D1の順方向電圧を0.4V,D2の順方向電圧を0.6Vとしたときの波形が正しいのは,図2の(a)~(d)のどれでしょうか.

I1は,10μs間の振幅が1mAとなる矩形波を入力する.

正しい波形はどれでしょうか?

(a)の波形 (b)の波形 (c)の波形 (d)の波形

今回は,NPNトランジスタと2つのダイオードを組み合わせ,トランジスタの飽和を防止する回路の動きから,OUTの波形を考える問題です.図2の波形の違いは,OUTの極性と振幅です.Q1がONしているときの電流の方向より,回路内部の電圧を検討すると分かります.

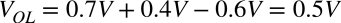

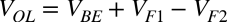

図1は,NPNを使ったインバータ回路なので,I1からQ1のベースへ電流が流れると,OUTの電圧は下がります.この論理になっているのは図2の(a)と(b)です.次にQ1がONのときの回路の電流は,I1の一部の電流がD1を通ってQ1のベース電流となり,残りはD2を通ってQ1のコレクタに流れます.このとき,INの電圧は,Q1のベース・エミッタ電圧とダイオード(D1)の順方向電圧を加えた値となり,OUTの電圧はINの電圧からダイオード(D2)の順方向電圧を減じた値となります.OUTの電圧が低いときの記号をVOLとすれば式1の電圧となり,図2の(a)の波形が正解となります.

・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・(1)

図1のようにトランジスタが飽和しないようにOUTの電圧を固定するトランジスタ飽和防止回路を,ベーカー・クランプ(Baker Clamp)回路と言います.この名前は,考案者のRichard H.Baker氏にちなんで名付けられました.

●トランジスタが飽和したときの動作

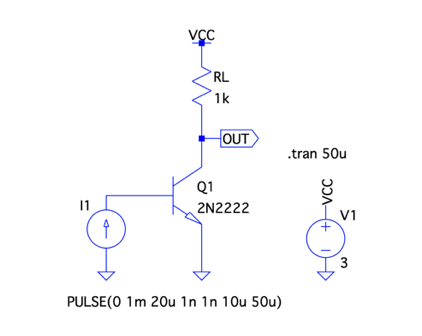

図3は,トランジスタ(Q1)と負荷抵抗(RL)で構成したエミッタ接地回路です.トランジスタをスイッチのように使い,OUTの電圧が電源電圧に近い状態をディジタル信号のHigh,逆に,GNDに近い状態をLowとするインバータ回路です.この回路で,図1と同じ入力電流を加えたとき,OUTの波形がどうなるのか確認してみます.

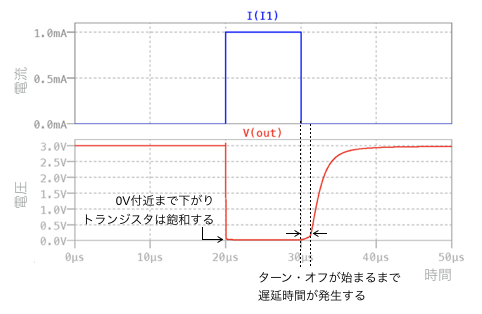

図4は,シミュレーション結果です.上段にI1の電流,下段にOUTの電圧をプロットしました.I1から電流が流れないとき,トランジスタがOFFになっているので,OUTの電圧は,3VのHighの状態となります.I1から電流が流れるとき,トランジスタのベースへ流れてQ1のコレクタ電圧は,0V付近まで下がり,Lowの状態となります.この状態は,トランジスタの増幅機能が極端に低下するので,飽和と呼びます.

トランジスタが飽和すると,OUTの電圧がONからOFFに切り替わるときの,スイッチングの特性が低下します.これはI1の電流が無くなっても,ベースに蓄えられた電荷により,トランジスタがターンオフする切り替わりの時間が遅くなるからです.このようなスイッチング特性の低下は,ディジタル回路としてあまり良くありません.

●ベーカー・クランプ回路の動作

図5は,ベーカー・クランプ回路の動作を解説するため,図1を書き直して電圧と電流を記入しました.IINが流れないときは,ベース電流(IB)が流れないためトランジスタはOFFします.IINが流れるとベース電流(IB)となりトランジスタはONします.IINの電流が,トランジスタがONするのに必要なベース電流以上となると,余った電流(IIN-IB)は図5の経路へ分流し,トランジスタのコレクタへ流れます.このときのOUTの電圧をVOLとすれば式2となり,トランジスタが飽和しない電圧へ固定します.式2へVBE,VF1,VF2の具体的な値を入れたのが式1となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

ベーカー・クランプ回路は,トランジスタが飽和しないようにOUTの電圧を固定するため,スイッチングの特性が低下するのを防ぎます.

回路内部の電圧と電流を記載した.

●ベーカー・クランプ回路をシミュレーションする

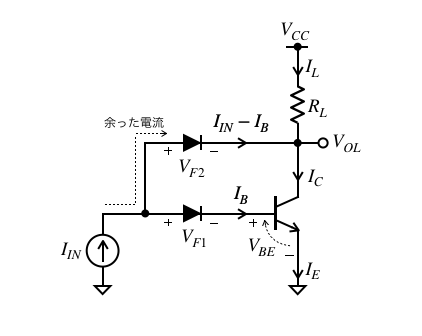

図6は,図1をシミュレーションする回路です.I1の電流源から20μs~30μs間で1mAを流し,0μs~50μs間の過渡解析を行います.

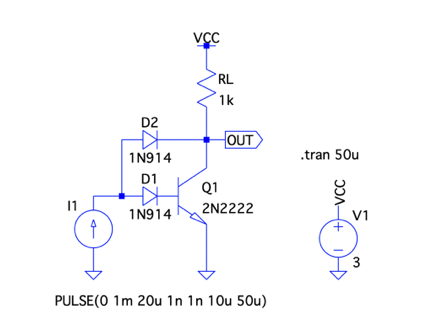

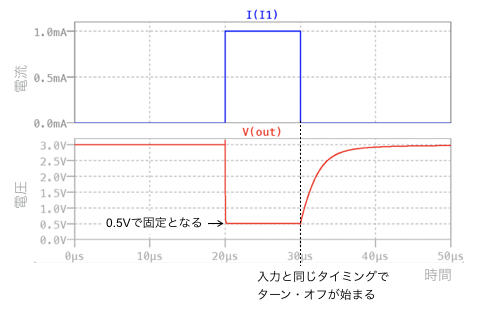

図7は,図6のシミュレーション結果です.上段にI1の電流,下段にOUTの電圧をプロットしました.図7のOUTがLowの状態となる電圧は,ベーカー・クランプ回路により,式1の0.5Vに固定され,トランジスタは飽和しません.飽和をしないことから,I1の電流が無くなったと同時にターンオフしており,図4の結果と比べると,スイッチング特性は改善することが分かります.

アナログ回路では,トランジスタが飽和しないように使いますが,ディジタル回路ではトランジスタを飽和させてLowの電圧とすることがあります.このとき,スイッチングの特性が低下するため,対策案の1つとしてベーカー・クランプ回路を用い,トランジスタの飽和を防ぎます.ベーカー・クランプ回路の有無でLowの電圧が異なりますので注意が必要です.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice5_028.zip

●データ・ファイル内容

Inverter_NPN.asc:図3の回路

Baker_Clamp_NPN.asc:図6の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs

(8) オームの法則から学ぶLTspiceアナログ回路入門アーカイブs