自励発振型D級パワーアンプの動作

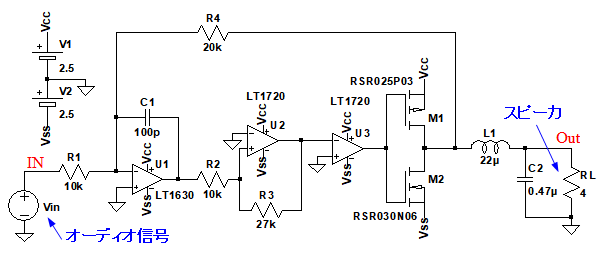

図1は,出力段にパワーMOSFETを使用したオーディオ用のD級パワーアンプです.U1はOPアンプで,U2とU3はコンパレータです.電源電圧は±2.5Vで,パワーMOSFETが約300kHzの周波数でスイッチングしています.そして,4Ωのスピーカを駆動します.このD級パワーアンプのIN端子からOUT端子までの1kHzのオーディオ信号に対するゲインの絶対値は,次の(A)~(D)のどれでしょうか.

このD級パワーアンプのIN端子からOUT端子までのゲインは?

(A)1倍 (B)2倍 (C)2.7倍 (D)10倍

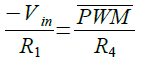

図1の回路は,自励発振型のD級パワーアンプです.パワーMOSFETの出力をR4で積分回路に帰還することで,約300kHzで発振しています.また,入力信号は,R1を介して同じ積分回路に入力されています.これらのことを考えると,IN端子からOUT端子までのゲインを計算できます.

図1のD級パワーアンプのオーディオ信号に対するゲインの絶対値は,R1とR4で決まり,R4/R1で計算することができます.R4が20kΩでR1が10kΩのため,ゲインは,2倍となります.また,L1とC2でハイパス・フィルタを構成していますが,カットオフ周波数が50kHzなので,1kHzのオーディオ信号は減衰しません.したがって正解は(B)ということになります.

●無信号時のD級パワーアンプの動作

図2は,図1の自励発振型D級パワーアンプの動作を検証するための回路です.この回路のシミュレーション結果を使用して,自励発振型D級パワーアンプの動作を解説します.

入力直流電圧を変えた時の動作をシミュレーションする.

図2において,U2は,シュミット・トリガ回路を構成しています.そのため,このコンパレータは,ヒステリシスを持ち,そのスレッショルド電圧は,「Vcc*R2/R3」と「Vss*R2/R3」で計算できます.図2の定数を代入すると,それぞれ約1V,-1Vになります.U3は,U2のコンパレータ出力の極性を反転します.そしてU3の出力でパワーMOSFETのM1,M2をドライブします.M1,M2で再び極性が反転するので,結局U2出力(CMP)とパワーMOSFETのドレイン出力(PWM)の極性は同じになります.U1は出力と反転入力端子の間にC1が接続されているため,積分回路として動作し,入力電流を積分して電圧として出力します.

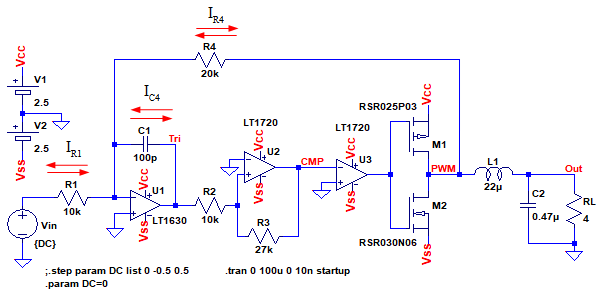

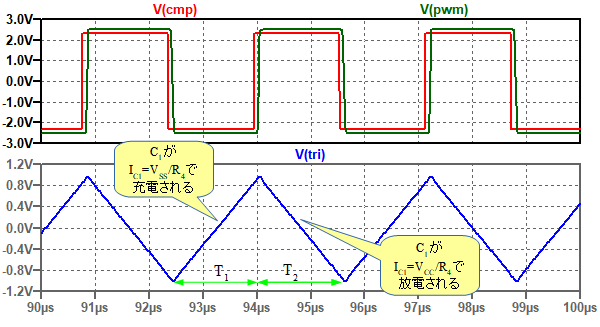

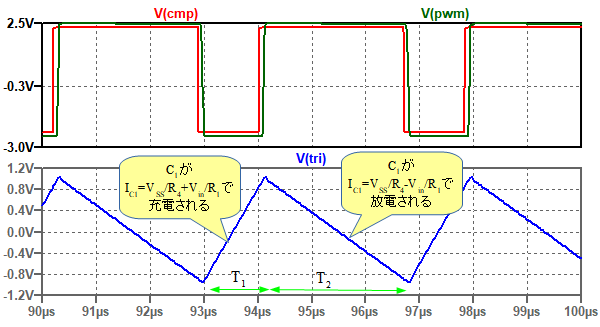

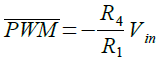

図3は,図2のVinの直流電圧が0Vのときのシミュレーション結果です.PWMとCMPは,同じ極性になっていることが分かります.なお,PWMのほうが若干遅れているのは,M1,M2のゲート容量の充放電時間によるものです.U1の反転入力端子は,GNDと同じ電圧になります.また,Vinの電圧が0Vのため,R1には電流が流れません.PWMがロー・レベルのとき,R4にはPWM端子方向に電流(IR4)が流れます.その電流値はVss/R4です.C1にもIR4と同じ電流が流れ,TRI端子の電圧が高くなる方向に充電されて行きます.

PWM端子の波形のデューティ比は50%になり,その平均電圧は0V.

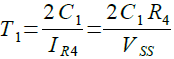

TRI端子の電圧が1Vに到達するとコンパレータが反転し,PWM端子の電圧はハイ・レベルになります.コンパレータが反転するまでの時間(図3のT1)は式1で表されます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

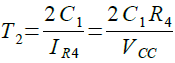

すると,R4の電流の向きが変わりU1の反転入力端子に向かって電流が流れます.その電流値は,Vcc/R4です.C1にもIR4と同じ電流が流れ,今度はTRI端子の電圧が低くなる方向に放電されて行きます.そして,TRI端子の電圧が-1Vに到達するとコンパレータが反転し,PWM端子の電圧はロー・レベルになります.再び,コンパレータが反転するまでの時間(図3のT2)は式2で表されます.この動作を繰り返すことで発振することになります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

Vccの電圧とVssの電圧が等しい場合,C1の充電時間と放電時間は同じになります.その結果,PWM端子の矩形波のデューティ比は50%になり,その平均電圧は0Vになります.つまり,入力電圧が0Vのときは出力電圧の平均値も0Vになることが分かります.

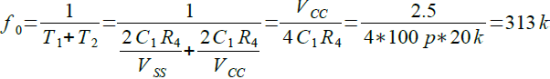

TRI端子の発振振幅は±1Vです.その発振周波数(f0)は,発振周期がT1+T2であることから,式3で計算することができます.

・・・・・(3)

・・・・・(3)

●-0.5V入力時のD級パワーアンプの動作

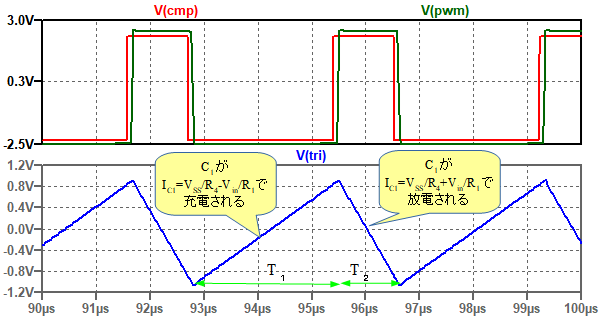

図2の入力直流電圧(Vin)を-0.5Vとしたときのシミュレーション結果が図4になります.

PWM端子の波形のオン・デューティ比は大きく,その平均値はVinを-R4/R1倍したもの.

R1には「IR1=Vin/R1」という電流が信号源に向かって流れます.そのため,PWM端子がロー・レベルのときはC1にはIR1とIR4を加算した電流が流れます.それで,TRI端子の電圧の傾きは図3よりも大きく,コンパレータのスレッショルドに達するまでの時間(T1)が短くなります.PWMがハイ・レベルになったときに,C1に流れる電流はIR4からIR1を引いた電流になります.なので,TRI端子の電圧の傾きは図3よりも小さく,コンパレータのスレッショルドに達するまでの時間(T2)が長くなります.その結果,PWM端子の矩形波は,ハイ・レベルの時間が長くなり,オン・デューティ比は50%よりも大きくなります.一方,OPアンプ(U1)の出力であるTRI端子の平均電圧は0Vになります.つまり,IR1とIR4の平均電流は式4のように等しいことになります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

IR4の平均値は,PWM端子の電圧の平均値をR4で割ったものなので,式5が成立します.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

式5を変形して,VinとPWM電圧の平均値の関係を求めると,式6のようになります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

つまり,入力電圧を-R4/R1倍したものが,PWM電圧の平均値ということになり,このアンプのゲインは-R4/R1である,ということができます.図2ではR1が10kΩでR2が20kΩなので,ゲインの絶対値が2倍の反転増幅回路になります.

●0.5V入力時のD級パワーアンプの動作

図5は,図2に入力直流電圧(Vin)を0.5Vとしたときのシミュレーション結果です.

PWM端子の波形のオン・デューティ比は小さく,その平均値はVinを-R4/R1倍したもの.

R1には「IR1=Vin/R1」という電流がU2の反転入力端子に向かって流れます.そのため,PWM端子がロー・レベルのときはC1にはIR4からIR1を引いた電流が流れます.そのため,TRI端子の電圧の傾きは,図3よりも小さく,コンパレータのスレッショルドに達するまでの時間(T1)が長くなります.PWMがハイ・レベルになったときに,C1に流れる電流はIR4とIR1を足した電流になります.そのため,TRI端子の電圧の傾きは図3よりも大きく,コンパレータのスレッショルドに達するまでの時間(T2)が短くなります.その結果,PWM端子のオン・デューティ比は50%よりも小さくなります.アンプのゲインに関しては,-0.5V入力のときと同等になります.

●オーディオ信号を入力したときのD級パワーアンプの動作

図6は,入力信号として1kHzでピーク電圧0.5Vの正弦波を加えたときの出力をシュミレーションするための回路図です.

入力に1kHzでピーク電圧0.5Vの正弦波を加えてシュミレーションする.

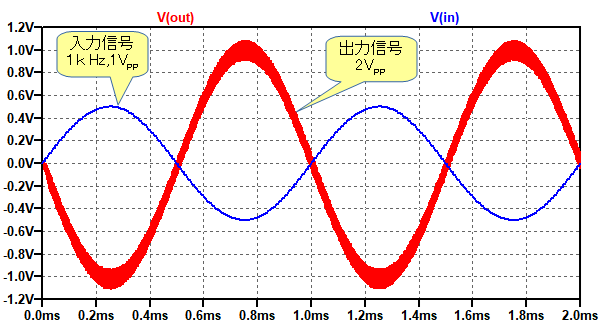

図7が図6のシミュレーション結果です.入力信号は1VPPで1kHzの正弦波です.OUT端子の信号はPWM出力をL1とC2からなるローパス・フィルタを通したものです.若干スイッチング信号が残っていますが,入力信号を位相反転した,2VPPの正弦波となっています.

OUT端子の信号は入力を位相反転した2VPPの正弦波となっている.

このことから,図6のD級パワーアンプはゲイン2倍の反転増幅回路として動作していることが分かります.

以上,自励発振型D級パワーアンプの動作を解説しました.回路をシンプルにするため,出力MOSFETは単純なインバータ接続となっていますが,実用回路では,2つのMOSFETが同時オンしないよう,ゲート駆動波形に工夫が必要になります.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice4_045.zip

●データ・ファイル内容

DclassAmp_DC.asc:図2の回路

DclassAmp_SIN.asc:図6の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs