位相同期回路の基本動作

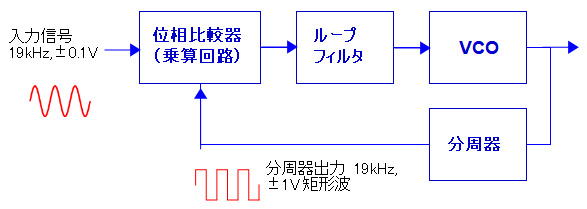

図1は,アナログ・タイプの位相比較器(乗算回路)を使用した,位相同期(PLL:Phase Locked Loop)回路の基本的なブロック図です.入力信号は,19kHz,±0.1Vの正弦波です.分周器の出力信号は,19kHz,±1Vの矩形波です.このPLL回路が位相ロックして定常状態にあるとき,入力信号と分周器出力の位相の関係として正しいのは(A)~(D)のどれでしょうか.

ただし,ループ・フィルタは,PLLループが安定して動作するような定数に設定してあるものとします.

入力信号とVCO出力の位相差は何度?

(A) 位相差0° (B) 位相差45° (C) 位相差90° (D) 位相差180°

図1の電圧制御発振器(VCO:Voltage-controlled oscillator)は,中心周波数が38kHzですが,次の分周器で1/2の周波数に分周され出力が19kHzになります.位相比較器は,入力信号と分周器出力を乗算し,10倍した結果を出力します.図1で使用されている位相比較器が乗算回路によるアナログ・タイプであることに着目すると,答えが分かります.

乗算回路を使用した位相比較器出力の平均値は,2つの入力信号の位相差が0°のとき正の最大値となり,位相差が180°のときに負の最大値となります.2つの入力信号の位相差が90°のときは平均出力電圧は0Vとなります.PLL回路は,位相比較器の出力電圧が0VとなるようにVCOの位相を制御します.そのため,PLL回路が位相ロックして定常状態にあるとき,入力信号と分周器出力の位相差は90°となります.

●PLL回路の用途

PLL回路は,電圧によって周波数の変化する発振器の位相,または,周波数を基準となる信号と同期させる働きをします.PLL回路の使用例としては,FMステレオ放送受信機で,受信した放送波からLch信号とRch信号を分離するデコーダ回路があります.FMステレオ・デコーダ回路は,パイロット信号と呼ばれる19kHzの信号に位相同期した38kHzの信号で入力信号をスイッチングすることで,Lch信号とRch信号を分離しています.オーディオ信号に混入された19kHzのパイロット信号に同期した信号を作りだすために,アナログ位相比較器を使用したPLL回路が必要になります.

●PLL回路の動作

VCOの発振周波数は,ループ・フィルタ出力でコントロールされます.そしてVCO出力は分周回路で周波数を1/Nに下げ,その分周器出力が位相比較器に入力されます.アナログ位相比較器では,入力信号と分周器出力の乗算を行います.その乗算出力はループ・フィルタにより,高い周波数成分が取り除かれます.この高い周波数成分が取り除かれた位相比較器出力で,VCOがコントロールされることになります.

入力信号と分周器出力の位相が同位相の場合,ループ・フィルタの出力電圧が高くなり,VCO周波数も高くなります.入力信号と分周器出力の位相が逆位相の場合,ループ・フィルタの出力電圧が低くなり,VCO周波数が低くなります.入力信号と分周器出力の位相が90°のとき,ループ・フィルタの出力電圧が0Vになり,VCO周波数は初期周波数と同じになります.この状態でループが安定するため,PLL回路は入力信号と,分周器出力の位相が90°ずれた状態でロックすることになります.

●ビヘイビア・モデルを利用する

図1のPLL回路がロックしたときの,入力信号と分周器出力の位相関係をシミュレーションで確認するためにはトランジェント解析を使用する必要があります.ただし,図1のブロック図を実際の回路に置き換えてトランジェント解析を行うと,シミュレーション実行に長時間かかります.そこで図1のブロック図のVCO及び位相比較器をビヘイビア・モデルで構成することにします.

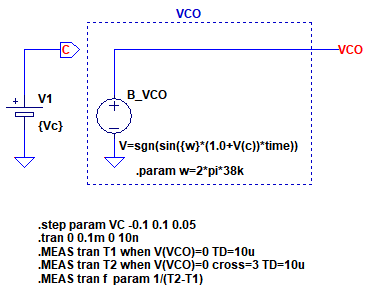

●ビヘイビア・モデルの電源でVCOを構成する

図2がビヘイビア・モデルで構成した電源(BV)で,矩形波出力のVCOです.BVは,電圧の値の指定にsin(x)のような数学関数を使用することができます.

sin(x)関数とsgn(x)関数を使用している.

C点の電圧で周波数が変化する,中心周波数38kHzの正弦波は,次のように記述することができます.

V=sin({w}*(1.0+V(c))*time)

正弦波出力を±1Vの矩形波とするため,さらにsgn(x)関数を使い,矩形波に波形整形しています.sgn(x)関数はxの値が正であれば1を,負であれば-1を出力します.

図2は,V1の電圧を「.stepコマンド」で-0.1V~0.1Vまで0.05Vステップで変化させています.そして「.MEASコマンド」を使用し,それぞれの電圧の周波数を計算しています.

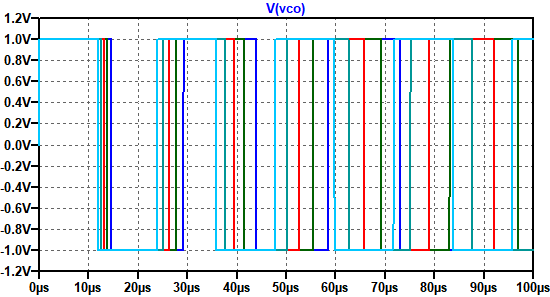

図3は,図2のVCOの出力波形のシミュレーション結果です.VCO出力は,±1Vの矩形波となっています.

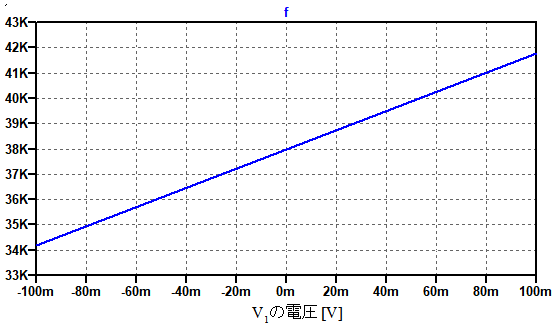

図4は,図3のVCO出力波形からV1の電圧と発振周波数の関係をグラフ化したものです.V1の電圧が±0.1V変化すると±10%発振周波数が変化していることが分かります.

±0.1Vの電圧変化で±10%発振周波数が変化している.

●ビヘイビア・モデルの電源でアナログ位相比較器を構成する

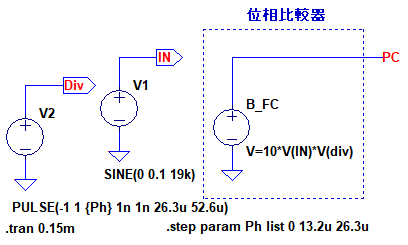

図5がBVで構成したアナログ位相比較器です.「V=10*V(IN)*V(div)」と記述することで,出力電圧はV(IN)とV(div)の乗算結果を10倍したものになります.図5は,±0.1V,19kHzの正弦波と±1V,19kHzの矩形波を入力し,矩形波の位相(実際は遅延時間)を「.stepコマンド」で0°,90°,180°と変化させたシミュレーションを行います.

2つの入力信号を係数を10で乗算した結果を出力する.

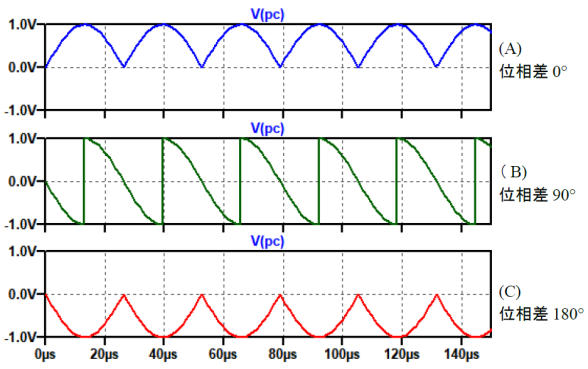

図6は,図5のシミュレーション結果です.図6(A)は,位相差が0°のときの位相比較器の波形です.入力信号を+側で全波整流した波形となり,平均電圧は637mVになります.図6(B)は,位相差が90°のときの位相比較器出力の波形で,平均電圧が0Vです.図6(C)は,位相差が180°のときの位相比較器の波形です.入力信号を-側で全波整流した波形となり,その平均電圧は,-637mVになります.

位相差により,出力平均電圧が変化している.

●ビヘイビア素子で構成したPLL回路

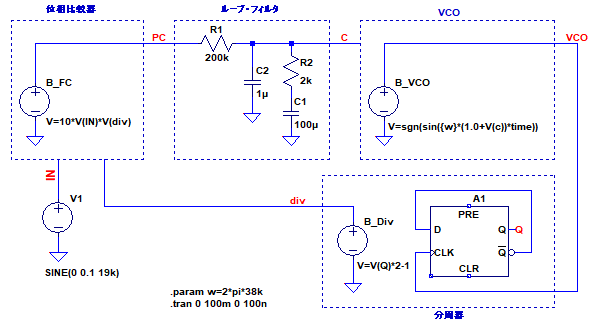

図7は,図2のVCOと図5の位相比較器を組み合わせて構成したPLL回路です.分周回路は,LTspiceのライブラリにあるDFFを使用し,出力をBVを使用して±1Vに波形整形しています.ループ・フィルタは抵抗とコンデンサを組み合わせたもので,ラグ・リードフィルタと呼ばれているものを使用しています.図7の回路で100msまでのトランジェント解析を行い,入力信号と分周器出力の位相関係を調べます.

ループ・フィルタは抵抗とコンデンサを組み合わせたラグ・リードフィルタを使用.

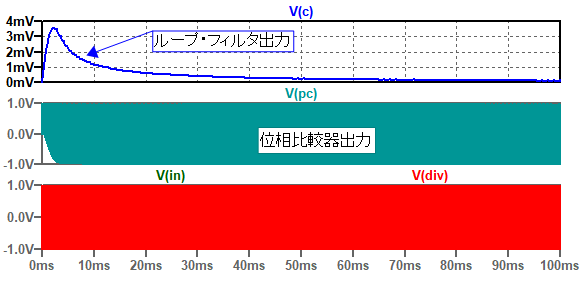

図8は,図7のシミュレーション結果です.ループ・フィルタの出力電圧は上昇を始めまが,すぐに,減少に転じ,やがて0mVに収束していきます.

ループ・フィルタ出力電圧は一端上昇し、0mVに収束していく.

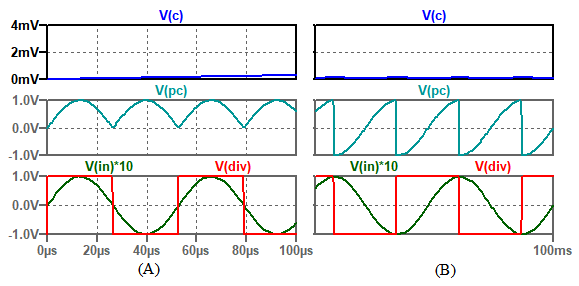

図9(A)は,最初の100μsを拡大したものです.入力信号と分周器出力は同相となっており,位相比較器出力は,+側の全波整流波形となっています.図9(B)は,最後の100μsを拡大したものです.入力信号と分周器出力の位相差は90°となっています.また,位相比較器出力の波形は0Vを中心に上下対称で,平均値は0Vです.このように,図7のPLL回路が安定した状態では入力信号と分周器出力の位相差は90°となることが分かります.

(A)最初の100μsを拡大

(B)最後の100μsを拡大

PLL回路が安定した状態では入力信号と分周器出力の位相差は90°となる.

以上,アナログ位相比較器を使用したPLL回路について解説しました.アナログ位相比較器には,周波数を弁別する機能が無いため,入力信号の周波数と分周器出力の周波数が,数パーセント以上ずれていると,PLL回路はロックできないことに,注意が必要です.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice4_038.zip

●データ・ファイル内容

VCO_BV.asc:図2の回路

FC_BV.asc:図5の回路

PLL_BV.asc:図7の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs