負帰還回路のノイズ・ゲイン制御

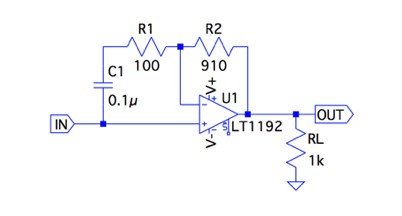

図1は,高速OPアンプ(LT1192)を使用しているにもかかわらず,INからOUTまでの信号ゲインに影響を与えず,ノイズ・ゲインで負帰還を安定させている回路です.ノイズ・ゲインはR1,R2,C1で構成し,出力が発振しないように制御しています.また,高速OPアンプは,非反転アンプで使用する場合,信号ゲインが5以上で安定します.図1の回路において,INからOUTまでの信号ゲインは,次の(a)~(d)のどれでしょうか.

(a) 0.5倍 (b) 1倍 (c) 9.1倍 (d) 10.1倍

図1の信号ゲインは,複雑な計算をしなくても解ります.低周波でC1がオープン(通電しない)の状態と高周波でC1がショート(通電する)の状態の2つの回路の接続状態から信号ゲインが解ります.この回路は,ノイズ・ゲインで負帰還を安定させるので,信号ゲインに制約がある高速OPアンプにおいて,その制約以下の固定ゲインを得ることができます.図1に使用した高速OPアンプは,非反転アンプの状態で,信号ゲインが5以上で安定(発振しない)の条件がつくOPアンプを使用しています.

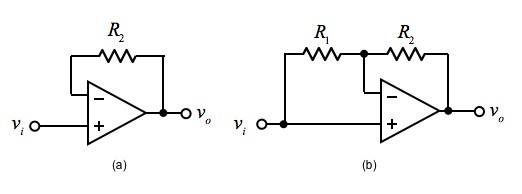

図2(a)は,図1が低周波の場合を示し,C1をオープンにした等価回路です.図2(a)は,ボルテージ・フォロワであり,信号ゲインは1倍となります.

図2(b)は,高周波の場合を示し,C1をショートにした等価回路です.図2(b)は,非反転端子と反転端子は負帰還の効果によりバーチャル・ショートなので,R1に電流は流れません.よってR2の電圧降下はゼロであり,こちらも信号ゲインは1倍となります.

R1,R2,C1で決まるノイズ・ゲインが周波数によって変化するときも図2(b)と同じであり,よって,図1のINからOUTまでの信号ゲインは解答の(b)1倍となります.

(a) C1がオープンのときの回路 (b) C1がショートのときの回路

●信号ゲインに制約がある高速OPアンプ

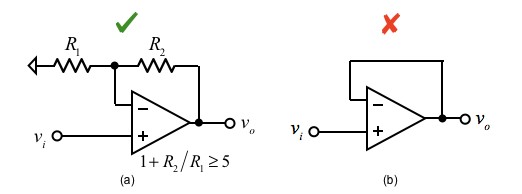

図3(a)に示す非反転アンプは,低い信号ゲインの負帰還安定性を犠牲にし,カタログに記載してある信号ゲイン以上に設定すれば,高速/広帯域アンプとなります.このタイプの高速OPアンプは,図3(b)の信号ゲインが1倍のボルテージ・フォロワにすると出力が発振するため,バッファ回路として使用できません.しかし,図1のような負帰還を施した回路にして,ノイズ・ゲインを適切に制御することにより,信号ゲインが1倍でも発振しない回路を作ることができます.

ノイズ・ゲインは帰還率(β)の逆数で表します.負帰還の安定性を調整するのはノイズ・ゲインです.信号ゲインとノイズ・ゲインを別に設定できれば,この制約は,無くなります.

(a) 信号ゲインが5倍以上で負帰還が安定するアプリケーション例

(b) 信号ゲインが1倍だと負帰還が不安定になり,カタログに使用不可の記載がある

●信号ゲインが5以上で安定するOPアンプの過渡特性

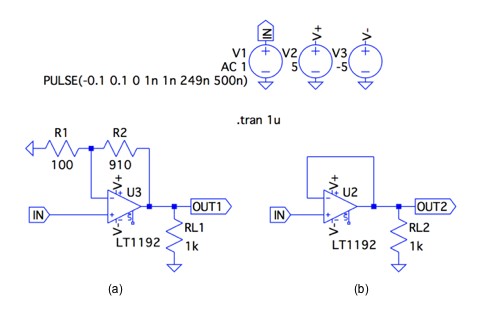

図4は,信号ゲインが5倍以上で安定する高速OPアンプのアプリケーション回路です.図4(a)は,非反転アンプの信号ゲインを10.1倍にした回路です.図4(b)は,使用不可のボルテージ・フォロワにしたものです.負荷抵抗は,2つの回路とも1kΩとしました.入力には立ち上がりが1ns,振幅±0.1Vの高速なパルスを印加し,過渡解析で出力発振の有無を調べます.

(a) 信号ゲインが10倍の非反転アンプ

(b) ボルテージ・フォロワ

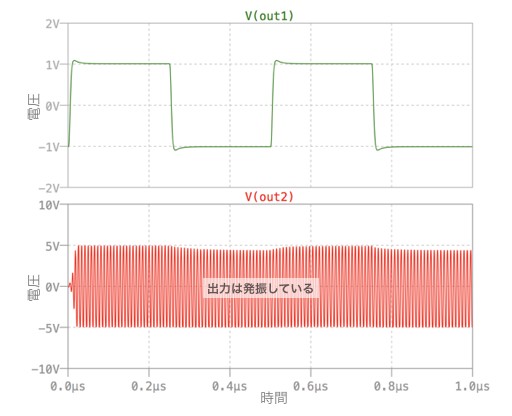

図5は,図4のシミュレーション結果です.上段が図4(a),下段が図4(b)の出力をプロットしました.信号ゲインが10.1倍だと,カタログ推奨の信号ゲイン5倍以上となり,出力は発振せず,入力に比例した高速なパルス応答となります.しかし,ボルテージ・フォロワにすると出力は発振し,ゲインが1倍のバッファ回路として機能しません.

上段:図4(a)の信号ゲインが10.1倍の非反転アンプ 過渡解析結果

下段:図4(b)のボルテージ・フォロワ 過渡解析結果,発振している

●ボルテージ・フォロワで発振する原因

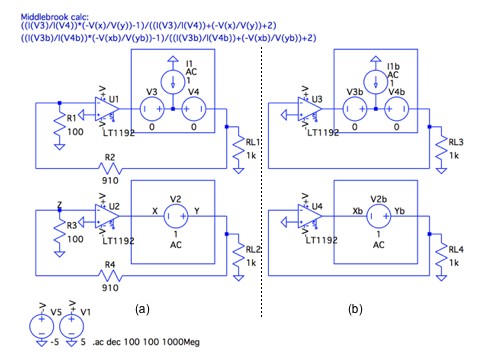

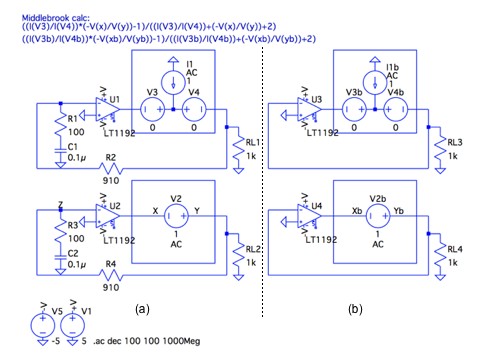

図6は,図4(a)と(b)のループ・ゲインを評価するMiddlebrook法の回路です.図6(a)が図4(a)のループ・ゲイン,図6(b)が図4(b)のループ・ゲインです.図4(b)はボルテージ・フォロワなので,図6(b)のループ・ゲインは,高速OPアンプのオープン・ループ・ゲインとなります.

(a) 信号ゲインが10倍の非反転アンプ

(b) ボルテージ・フォロワ

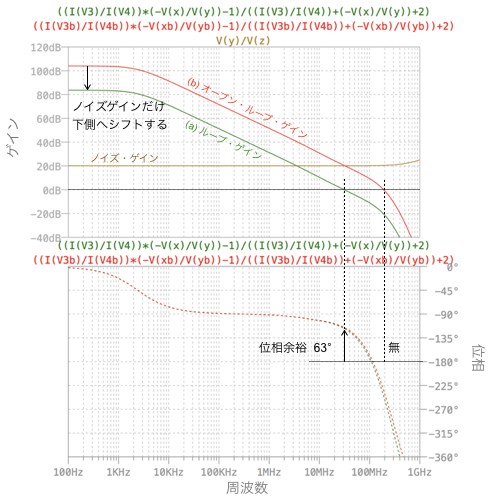

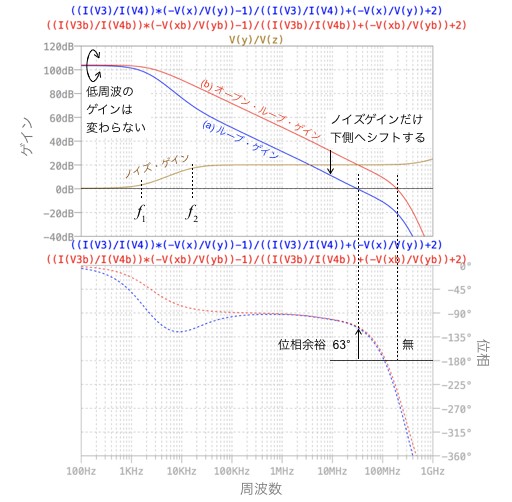

図7は,図6のシミュレーション結果です.上段がゲイン周波数特性,下段が位相周波数特性です.プロットは,Middlebrook法の計算式を用いています.非反転アンプの信号ゲインとノイズ・ゲインは等しいため,図6(a)のループ・ゲインは,OPアンプのオープン・ループ・ゲインからノイズ・ゲイン(ここでは10.1倍=約20dB)だけ減り.周波数特性が下側へシフトします.このため,図6(a)の位相余裕は63°あります.一方,ボルテージ・フォロワのループ・ゲインは位相余裕が無く,負帰還が不安定になり,出力発振となります.

上段:ゲイン周波数特性

下段:位相周波数特性

ボルテージ・フォロワの場合,位相余裕は無い

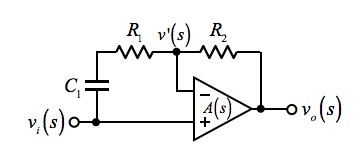

●ノイズ・ゲインと信号ゲイン

図8は,図1のノイズ・ゲインと信号ゲインを求めるため,図1にOPアンプのオープン・ループ・ゲイン「A(s)」と,反転端子の電圧「v’(s)」の記号を加えた回路です.回路の動作は解答で示しましたが,ここでは,図8を用いてノイズ・ゲインと信号ゲインを計算します.

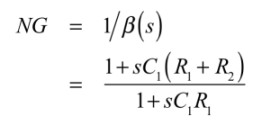

図8のノイズ・ゲイン「NG」は,帰還率「β(s)」の逆数ですので,式1となります.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

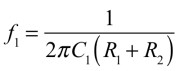

式1より,ノイズ・ゲインのゼロは式2となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

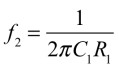

また,ノイズ・ゲインのポールは式3となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

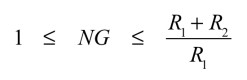

ノイズ・ゲインの範囲は式4となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

式2,式3,式4より,低周波のノイズ・ゲインは1倍で,f1の周波数付近でゲインが増えはじめ,f2の周波数より高くなると「1+R2/R1」で一定となります.

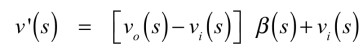

次に信号ゲインを求めます.OPアンプ反転端子の電圧は,式5となります.

・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・(5)

出力vo(s)は,OPアンプの非反転端子と反転端子の僅かな電圧差をオープン・ループ・ゲイン倍した値ですので,式6となります.

・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・(6)

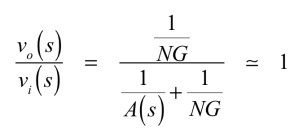

式6へ式5を代入し,帰還率「β(s)」とノイズ・ゲイン「NG」は逆数の関係であることを使って式を整理すると,信号ゲインは式7となります.

・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・(7)

ここでオープン・ループ・ゲインは「1<NG<<A(s)」であることから,信号ゲインはノイズ・ゲインに関係なく強制的に1倍となります.

以上の解析より,図1はノイズ・ゲインと信号ゲインを別々に設定できることが分かります.出力が発振しないようにするだけなら,C1はなくても動作します.しかし,C1を無くすと直流のノイズ・ゲインが大きくなるため,出力オフセット電圧と出力雑音電圧の双方が増えます.C1があると,出力オフセット電圧増えず,式1の周波数以上の帯域で,出力雑音電圧のみが増えます.これがこの回路の弱点となります.

●負帰還安定性をLTspiceで確認する

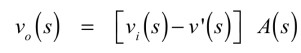

図9(a)は図1のループ・ゲインを評価するMiddlebrook法の回路です.比較のため,図9(b)へOPアンプのオープン・ループ・ゲインを調べる回路を追加しました.

(a) 図1のループ・ゲイン周波数特性を調べる回路

(b) OPアンプのオープン・ループ・ゲイン周波数特性を調べる回路

図10は,図9のシミュレーション結果で,上段がゲイン周波数特性,下段が位相周波数特性をプロットしました.図9(a)のループ・ゲインは,式2のf1より低い周波数で,図9(b)のOPアンプのオープン・ループ・ゲインと同じです.f1と式3のf2の間でノイズ・ゲインが大きくなり,f2以降の高周波側でノイズ・ゲインは一定となります.f2以降の高周波側では,ループ・ゲインはノイズ・ゲインの分だけ下がります.これにより,位相余裕は63°となり,負帰還は安定になります.

(a) ノイズ・ゲインを調整した図1のループ・ゲイン周波数特性

(b) OPアンプのオープ・ループ・ゲイン周波数特性

●周波数特性と過渡応答をLTspiceで確認する

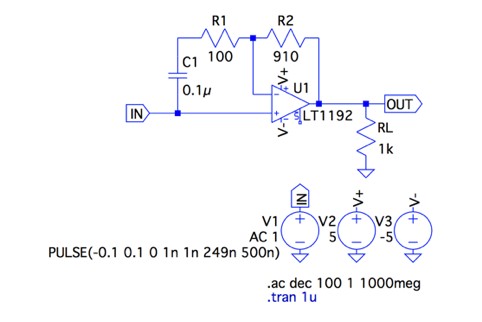

図11は,図1の信号ゲイン周波数特性と過渡応答を調べる回路です.

過渡解析ではIN端子へ高速なパルスを印加し,発振の有無を確かめる

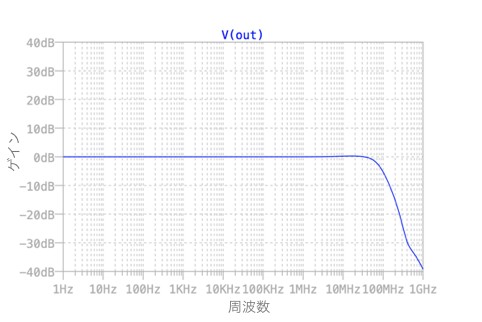

図12は,図11で解析の指定を「.ac dec 100 1 1000meg」としたときのシミュレーション結果で,10MHz以上の高い周波数までゲインが0dB(1倍)となります.

信号ゲインが1倍の広帯域バッファとして動作している.

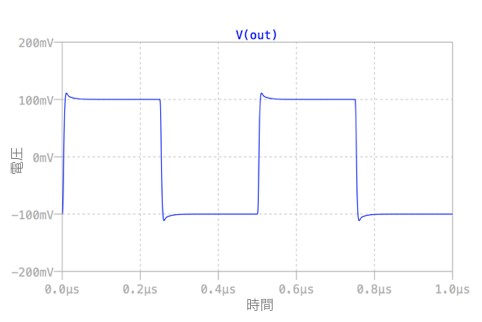

図13は,解析の指定を「.tran 1u」に変えて,振幅が±0.1V,立ち上がりが1nsの高速なパルスを印加し,過渡解析した結果です.出力の発振も無く,信号ゲインが1倍の高速バッファとして機能していることが分かります.

出力の発振は無く,信号ゲインが1倍の高速バッファとして動作している.

以上,解説したように,負帰還安定性の観点から,使用できる信号ゲインに制約がある高速OPアンプでも,ノイズ・ゲインを適切に調整することにより,信号ゲインが1倍の高速バッファ回路を作ることができます.ノイズ・ゲインと信号ゲインを別に設定するこの技法は,出力雑音電圧が増えることが弱点です.また,出力のセトリングタイムにも留意してください.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice4_037.zip

●データ・ファイル内容

Hi-speed_Amplifier.asc:図4の回路

LoopGain_Hi-speed_OPAmp.asc:図6の回路

LoopGain_with_Noise_gain_trick.asc:図9の回路

Hi-speed_follower.asc:図11の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs