応答時間を最適化する入力容量の中和回路

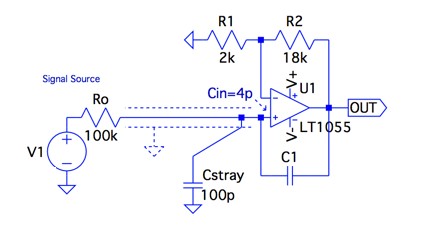

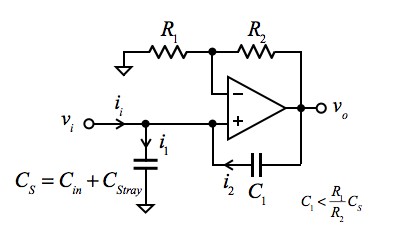

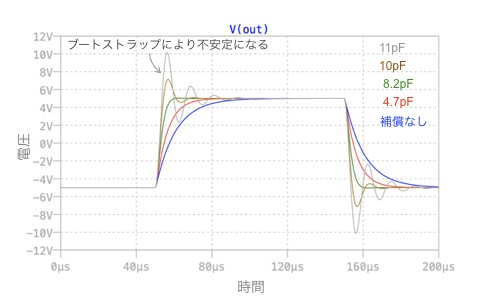

図1は,OPアンプ(U1)と抵抗(R1,R2)で構成したゲインが20dBの非反転増幅器です.信号源からOPアンプまでの配線につく浮遊容量(CStray)が100pFあり,OPアンプの非反転端子(+端子)の入力容量(Cin)はデータシートより4pFです.この2つの容量は,非反転端子とGND間にあるため「CS=Cin+CStray」とします.補償コンデンサ(C1)は,ブートストラップ(正帰還)を施し,非反転端子の浮遊容量(CS)を中和させる働きがあります.図1において,入力容量となる浮遊容量(CS)を中和する補償コンデンサ(C1)は,次の(a)~(d)のうちどれでしょうか.なお,OPアンプは理想とします.

ブートストラップを施した補償コンデンサ(C1)で浮遊容量(CS)を中和する.

(b) C1<(1+R2/R1)CS

(c) C1<(R1/R2)CS

(d) C1<(R2/R1)CS

図1の信号源(V1とRO)を外し,非反転端子から見た入力インピーダンスを計算すると,浮遊容量(CS)とブートストラップを施した補償コンデンサ(C1)の関係が導かれます.容量を中和するということは,浮遊容量(CS)を補償コンデンサ(C1)でキャンセルすることです.ブートストラップは正帰還であり,回路を不安定にしないためにC1とCSの関係を不等号で示しています.

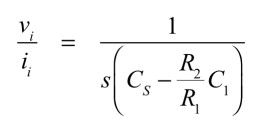

図1の信号源に相当するV1とROを外して,非反転端子から見た入力インピーダンスは式1となります.

・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・(1)

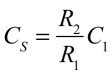

CSをC1で補償するには,式1の分母より式2の関係になります.しかし,C1はブートストラップ(正帰還)であり,この条件では回路が不安定になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

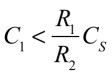

式2をC1で整理して式3の大小関係にすれば,浮遊容量(CS)を中和しながら出力が発振しない補償コンデンサ(C1)となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

●ブートストラップを施した入力容量中和回路

図2は,ブートストラップを施し,入力容量中和回路を解説する回路です.図2は,非反転増幅器の入力端子とGND間に浮遊容量(CS)があり,それをC1でキャンセルします.この関係を非反転端子の入力インピーダンスの式を使って解説します.

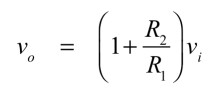

OPアンプの出力電圧は,入力電圧に非反転増幅器のゲインを乗じたものなので,式4となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

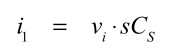

入力容量となる浮遊容量(CS)に流れる電流(i1)は式5となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

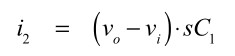

OPアンプの出力端子から補償コンデンサ(C1)を通り,非反転端子へ流れる電流(i2)は式6となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

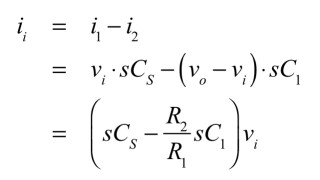

入力電圧(vi)を印加したとき,流れる電流(ii)は式7となります.

・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・(7)

式7を使い,入力インピーダンスを表す「vi/ii」としたのが解答の式1であり,CSを中和するC1は式3となります.

●入力インピーダンスのシミュレーション

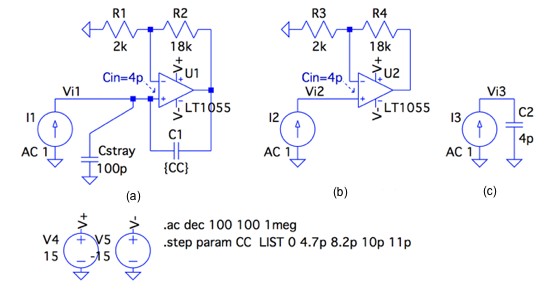

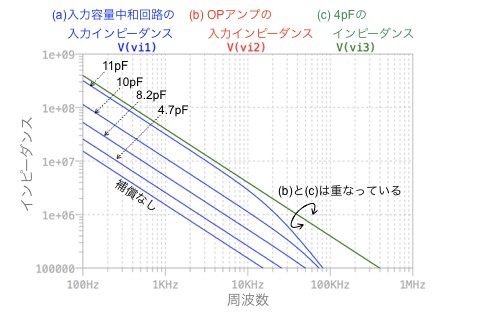

図3は,入力インピーダンスを調べる回路です.(a)は入力容量中和回路の入力インピーダンス,(b)と(c)はOPアンプの入力容量(Cin)がデータシートに記載されている4pFであるかを確かめる回路です.3つの回路とも電流源で印加していますので,Vi1,Vi2,Vi3をプロットするとインピーダンスの周波数特性になります.(a)入力容量中和回路の補償コンデンサ(C1)は「.stepコマンド」で「0pF,4.7pF,8.2pF,10pF,11pF」に変化させます.0pFは補償なしであり,11pFは「CS=Cin+CStray=104pF」を使い,式3の不等号が成り立つ境界付近です.

図4は,図3のシミュレーション結果で,入力インピーダンスをプロットしました.(b)と(c)は重なっており,OPアンプの入力容量は4pFであることが分かります.(a)の入力容量中和回路は,補償コンデンサ(C1)を大きくするとOPアンプの入力インピーダンスに近づいており,入力容量となる浮遊容量(CS)を中和しています.

(b)と(c)は重なっており,OPアンプの入力容量は4pFに等しい.

補償コンデンサ(C1)を大きくすると,入力容量(CS)が中和され,(b)に近づいていく.

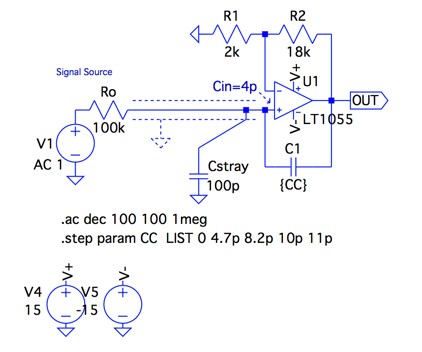

●非反転増幅器の周波数特性を調べる

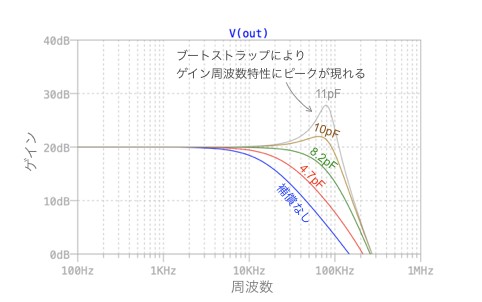

図5は,図1の周波数特性を調べる回路で,図3と同様に補償コンデンサ(C1)を変化させています.図6はゲイン周波数特性です.補償なし(C1=0pF)のときは,信号源の出力抵抗と浮遊容量(CS)の積分回路により,コーナー周波数は約15kHzにあります.補償コンデンサ(C1)を大きくしていくと,ゲイン周波数特性が改善します.式3の境界付近である11pFでは,ブートストラップの効果が顕著になり,ゲイン周波数特性にピークが現れます.これは回路が不安定になりつつあることを示しています.

補償コンデンサ(C1)を変化させ,周波数特性の変化を調べる.

C1を大きくすると,10kHz以上の周波数特性が改善する.

●非反転増幅器の応答時間の最適化

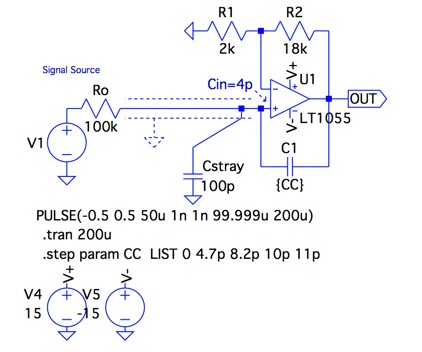

図7は,図1の回路へ,振幅±0.5V,パルスの繰り返し周波数が5kHzの矩形波を入力し,OUT端子の応答時間を調べる回路です.

C1を変化させ,応答時間の変化を調べる.

図8は,図7のシミュレーション結果です.補償コンデンサ(C1)を変化させた時のOUT端子の応答波形をプロットしました.補償なしでは,パルスの立ち上がりと立ち下がりの応答時間がなだらかです.補償コンデンサ(C1)を大きくしていくと,応答時間が改善され,パルスの立ち上がりと立ち下がりが急峻になっていきます.式3の境界に近い11pFでは,リンギングが出始め,回路が不安定に近づいていることが分かります.このように補償コンデンサ(C1)をパラメータにとり,応答時間の最適化ができます.

以上,解説したように,入力容量中和回路は,ブートストラップを施した補償コンデンサ(C1)で,浮遊容量等の入力容量を中和できます.ただしブートストラップは正帰還ですので,素子のバラツキや温度変化などを含めて,出力が発振しないように,式3の大小関係を保つことが必要です.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice4_027.zip

●データ・ファイル内容

Zin_AC.asc:図3の回路

Neutralizing_Input_Capacitance_AC.asc:図5の回路

Neutralizing_Input_Capacitance_Tran.asc:図7の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs

(7) IoT時代のLTspiceアナログ回路入門アーカイブs