反転加算回路のオフセットによる出力誤差

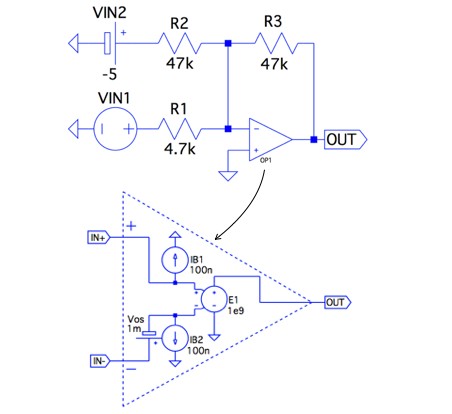

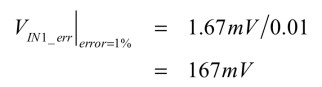

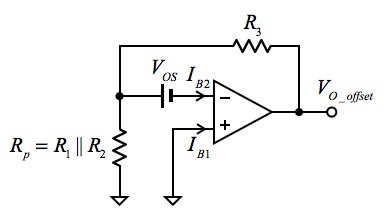

図1は,OPアンプと抵抗(R1,R2,R3)を用いた反転加算回路です.この回路には,VIN1とVIN2の2つの入力があり,VIN1から信号を入力し,VIN2から-5Vの直流を入力して増幅する直流アンプです.出力(OUT)には,オフセットによる出力誤差が発生します.また,OPアンプは,入力オフセット電圧が1mVで,非反転端子(+)の入力バイアス電流(IB1)と反転端子(-)の入力バイアス電流(IB2)が共に100nAです.この回路で,オフセットによる出力誤差が1%未満となるVIN1の最小入力電圧は,(a)~(d)のどれでしょうか.

OPアンプは,1mVのオフセット電圧(VOS)で,2つの入力バイアス電流(IB1,IB2)は100nA

図1の反転加算回路の入力オフセット電圧(VI_offset)は,OPアンプの入力オフセット電圧(VOS)と,抵抗(R1,R2,R3)に流れる入力バイアス電流(IB2)の電圧降下から求められます.反転加算回路の出力オフセット電圧(VO_offset)は,その入力オフセット電圧(VI_offset)をノイズ・ゲイン(NG)倍した値が出力に現れます.それを信号ゲイン(SG)で除算したものが,入力換算の誤差となります.入力換算の誤差より1%未満になる最小入力電圧を求めます.

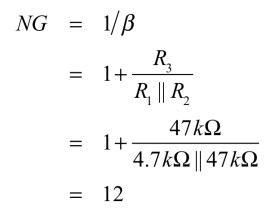

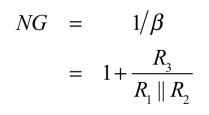

まず始めに,反転加算回路のノイズ・ゲイン(NG)と信号ゲイン(SG)を求めます.ノイズ・ゲイン(NG)は,負帰還の帰還率をβとすれば,式1となります.

・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・(1)

VIN1から出力(OUT)をみた信号ゲイン(SG)は,式2となります.

・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・(2)

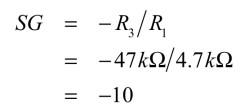

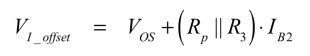

反転加算回路の入力オフセット電圧(VI_offset)は,OPアンプの入力オフセット電圧(VOS)と,抵抗(R1,R2,R3)の並列抵抗に流れる入力バイアス電流(IB2)の電圧降下より,式3となります.

・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・(3)

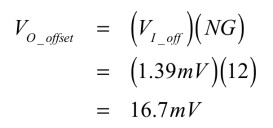

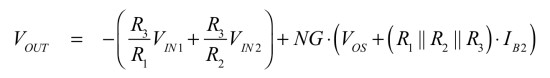

反転加算回路の出力オフセット電圧(VO_offset)は出力誤差となり,式3を式1のノイズ・ゲイン(NG)倍したものですので,式4となります.

・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・(4)

式4の出力誤差をVIN1に換算した入力誤差(VIN1_err)は,式4を式2の信号ゲイン(SG)の絶対値で除算したものであり,式5となります.

・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・(5)

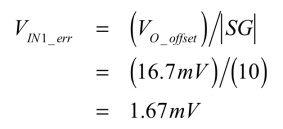

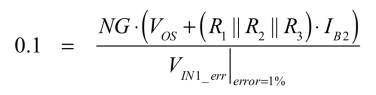

VIN1のオフセットによる誤差が1%未満となる最小入力電圧は式6となり,解答の(c)となります.

・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・(6)

直流アンプとして機能する回路は,OPアンプの入力オフセット電圧や入力バイアス電流による影響を考えなければいけません.入力オフセット電圧や入力バイアス電流は,OPアンプのデータシートに記載されています.データシートの入力オフセット電圧は,OPアンプ回路内で発生するものを,等価的に入力端子へ電圧源として出したもので,温度によってドリフトします.入力バイアス電流は,バイポーラ差動対のベース電流であり,CMOSの場合は流れません.図1のOPアンプは,入力オフセット電圧となる電圧源,入力バイアス電流となる2つの電流源,増幅段として電圧制御電圧源を用いたマクロモデルです.今回はこのOPアンプをサブサーキットで登録し,シミュレーションで使います.

●反転加算回路について

反転加算回路は,複数ある入力電圧を,抵抗比で決まるゲインで増幅し,それらを加算して出力する回路です.図1は,2入力ですが,R1とR2を並列に配置し入力を増やすことができます.図2は,反転加算回路の伝達特性を計算するための回路です.これを使い,入出力の伝達特性を計算します.

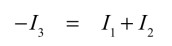

OPアンプの反転端子(-)は,バーチャル・グラウンドであり,キルヒホッフの電流則(KCL)より,図2のOPアンプ反転端子(-)のサミング・ポイントに流れる電流の総和はゼロです.よって,式7が成り立ちます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

また,I1,I2,I3の電流は式8となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

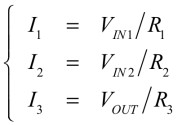

式7と式8を用いると,反転加算回路の入出力の伝達特性は,式9となります.VIN1は「R3/R1」のゲインで増幅します.また,VIN2は「R3/R2」のゲインで増幅し,VIN1とVIN2の2つを加算した電圧が出力電圧(VOUT)となります.図1の回路定数では,VIN1が10倍のゲインで増幅,VIN2が1倍のゲインで増幅後,2つを加算した結果が出力となります.

・・・・・・・・・・・・・・・・・・・・(9)

・・・・・・・・・・・・・・・・・・・・(9)

●反転加算回路の入力オフセット電圧

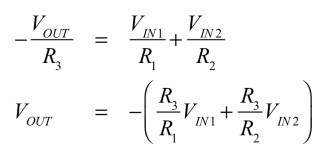

図3を使って,OPアンプに入力オフセット電圧(VOS)と2つの入力バイアス電流(IB1,IB2)があるときの反転加算回路の入力オフセット電圧について解説します.入力オフセット電圧は,出力オフセット電圧より求めます.

出力オフセット電圧は,無信号のときの出力電圧を考えるので,R1とR2の入力はグラウンドへ接続しRPとします.図3の出力オフセット電圧(VO_offset)は,式10となります.

・・・・・・・・・・・・・・・・(10)

・・・・・・・・・・・・・・・・(10)

ここでNGは,ノイズ・ゲインで,負帰還の帰還率をβとすれば,式11となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(11)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(11)

入力オフセット電圧は,式11をノイズ・ゲイン(NG)で除算したものなので式12となります.

・・・・・・・・・・・・・・・・・・・・・(12)

・・・・・・・・・・・・・・・・・・・・・(12)

●誤差が1%未満になる最小入力電圧

図1の反転加算回路のオフセット電圧を考慮した伝達特性は,式9と式10より,式13となります.出力誤差は,ゲインにも現れます.そこで,ここでは,オフセットによるゲインの誤差が1%未満になるVIN1の最少入力電圧として求めてみます.

・・・・・(13)

・・・・・(13)

VIN1の誤差を計算するため,式13から一定の電圧となる「(R3/R2)VIN2=5V」を取り除き,式14のVIN1からVOUT’までのゲインで考えます.

・・・・・・・・・(14)

・・・・・・・・・(14)

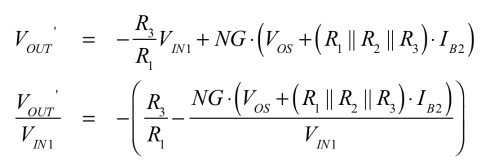

式14より,VIN1からVOUT’までのゲイン「VOUT’/VIN1」は,オフセット電圧に関わる項があるため,ゲイン誤差が生じます.抵抗比で設定したVIN1のゲインは「R3/R1=10」ですから,ゲイン誤差を1%とすれば式15となります.

・・・・・・・・・・・・・・・・(15)

・・・・・・・・・・・・・・・・(15)

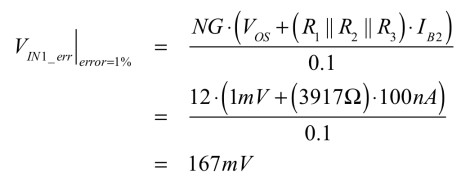

したがって,ゲイン誤差が1%未満となる最少入力電圧(VIN1_err)は式16となり,解答の(c)となります.

・・・・・・・・・・(16)

・・・・・・・・・・(16)

また,VIN2でも同様の計算ができ「R3/R2=1」ですから,ゲイン誤差が1%未満となる最少入力電圧(VIN2_err)は式17となります.図1のVIN2は5Vですので,最少入力電圧より大きな印加条件です.

・・・・・・・・・・(17)

・・・・・・・・・・(17)

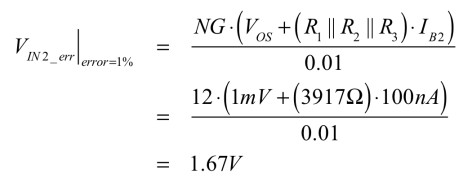

●反転加算回路をLTspiceで確認する

図4(a)は,図1のシミュレーション回路です.図4(b)は,比較のため,OPアンプの入力オフセット電圧(VOS)と2つの入力バイアス電流(IB1,IB2)が無い回路を用意しました.図4(a)と図4(b)のそれぞれの入力端子は,IN1に0~500mVをスイープし,IN2に直流電圧-5Vを印加します.

(a)は図1の回路で,(b)は比較のため,OPアンプの入力オフセット電圧と入力バイアス電流が無い回路.

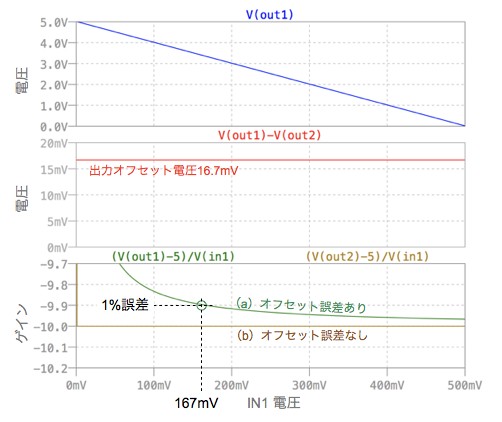

図5は,図4のシミュレーション結果です.グラフの上段はIN1を変化させたときの出力電圧です.IN2へ-5Vを印加しているので,OUT1の出力電圧は,「5V+出力オフセット電圧」を起点として負の傾きを持った出力電圧となります.中段は反転加算回路の出力オフセット電圧です.図4(a)と(b)の出力電圧差をプロットしました.これより,出力オフセット電圧は,16.7mVであることがわかります.下段は(a)と(b)の出力から直流5Vを減算し,IN1端子からOUT1,OUT2端子までのゲインを計算したプロットです.(a)はオフセット誤差があり,ゲイン誤差が1%未満になる最少入力電圧は167mVであり,解答の(c)と同じ電圧です.(b)はオフセット誤差がないため,ゲインは-10倍で一定です.

上段は,VIN1を変化させたときの出力電圧.

中段は,反転加算回路の入力オフセット電圧.

下段は,VIN1からVOUTのゲイン.

以上、解説したように,直流応答が重要な回路ではOPアンプの入力オフセット電圧,入力バイアス電流,また,今回は示しませんでしたが,2つの入力バイアス電流の僅かな差となる入力オフセット電流等が回路に与える影響について考慮しなければなりません.入力バイアス電流による誤差を少なくするためには,図1の非反転端子(+)にR1,R2,R3の並列抵抗を接続すれば,改善することができます.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice4_015.zip

●データ・ファイル内容

ldeal_OP_1.asc:図4のOP1の回路

ldeal_OP_1.asy:図4のOP1のシンボル

ldeal_OP_2.asc:図4のOP2の回路

ldeal_OP_2.asy:図4のOP2のシンボル

Summing_Amplifier_offset_error.asc:図4の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs