LDOレギュレータのライン・レギュレーション

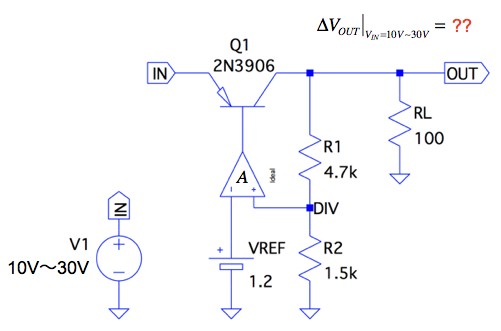

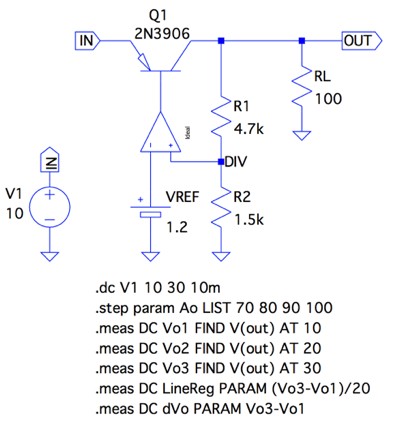

図1は,出力パス・トランジスタにPNPトランジスタ(Q1)を用いたLDO(Low Drop Out)レギュレータです.この回路で,IN端子の電圧が10V~30Vまで変化したとき,ライン・レギュレーション(ΔVOUT)が10mV以内となるのは,OPアンプの直流オープン・ループ・ゲイン(A)が(a)~(d)のどの場合でしょうか.

ここで,PNPトランジスタ(Q1)のアーリー電圧は「VA=100V」で,熱電圧が「VT=26mV」です.また,計算を簡単にするため,OPアンプは,直流オープン・ループ・ゲイン(A)のみが変化する理想OPアンプとし,入力インピーダンスが無限大,出力インピーダンスをゼロとします.

今回は,LDOレギュレータのライン・レギュレーションについて解説します.ライン・レギュレーションとは,入力電圧が変化した場合の,出力電圧の変動幅です.図1のLDOレギュレータは,出力パス・トランジスタ(Q1),抵抗(R1,R2),OPアンプで負帰還回路を構成し,VREFの電圧をR1とR2の比で増幅します.IN端子の変化は負帰還回路により抑えられますが,OPアンプは有限の直流オープン・ループ・ゲインであるため,わずかに出力電圧が変化します.図1のPNPトランジスタを等価回路(ここではπ型等価回路)で表し,IN端子の変化が,負帰還回路により,出力に伝達されるかを計算することにより求められます.

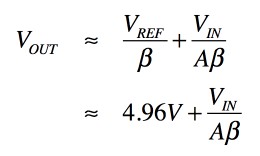

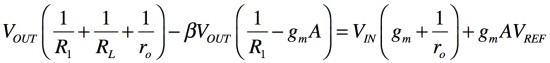

図1のOUT端子の出力電圧(VOUT)は式1となります.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

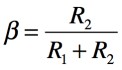

ここで,βは負帰還の帰還率であり式2となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

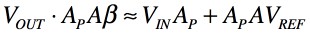

式1の右辺第一項は,VREFの電圧をR1とR2の抵抗比で増幅した出力電圧なので,図1の出力電圧は4.96Vとなります.また,右辺第二項は,IN端子の電圧によるOUT端子の誤差であり,OUT端子にはIN端子の電圧を負帰還のループ・ゲイン(Aβ)で除算した電圧が現れます.

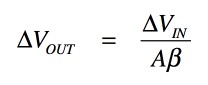

式1の右辺第二項より,IN端子の電圧の変化をΔVINとすれば,OUT端子の電圧誤差であるΔVOUTが式3となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

式3より,(a)~(d)のOPアンプの直流オープン・ループ・ゲインと式2の帰還率を使って計算すると次のようになり,OUT端子の出力電圧が10mV以内となるのは(b)の80dB以上となります.

| (a)70dB | ΔVOUT=26.1mV |

| (d)80dB | ΔVOUT=8.3mV |

| (c)90dB | ΔVOUT=2.6mV |

| (d)100dB | ΔVOUT=0.8mV |

●LDOレギュレータの概要

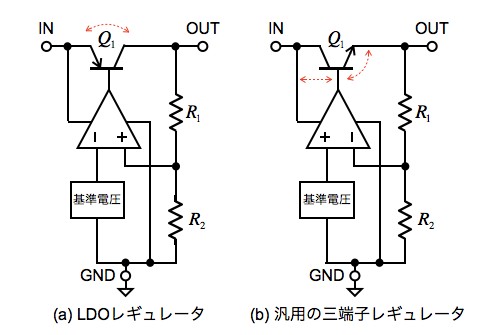

まず,LDOレギュレータの概要から解説します.図2(a)は,出力パス・トランジスタにPNPトランジスタを用いたLDOレギュレータのブロック図です.図2(b)は出力パス・トランジスタにNPNトランジスタを用いた,古くからある三端子レギュレータのブロック図です.図2(a)と(b)とも基準電圧をR1とR2の抵抗比により増幅し,定電圧出力となります.2つの回路の違いは,出力パス・トランジスタがPNPかNPNの差です.負帰還とするために,OPアンプの2つの入力端子が入れ替わっています.

LDOレギュレータの特徴は,出力パス・トランジスタにPNPトランジスタ(または,PMOS)を用いることにより,IN端子とOUT端子の入出力間電位差を小さくでき,低ドロップ・アウトのリニア・レギュレータとなります.入出力間電位差が何ボルトならLDOレギュレータと呼ぶというような決め事はありません.しかし,出力パス・トランジスタがPNPかPMOSを使い,入出力間電位差が0.2V~0.3V以下のリニア・レギュレータをLDOレギュレータと呼ぶことが多いと思います.

図2(a)と(b)の入出力間電位差を比較すると,図2(a)の入出力間電位差の最小値は,PNPトランジスタの飽和電圧で決まり,その値を小さくできます.一方,図2(b)の古くからある三端子レギュレータの入出力間電位差は,IN端子とOPアンプ最大出力電圧の差電圧と,NPNトランジスタのベース・エミッタ間電圧(VBE)を加えた電圧であり,図2(a)のように小さくできません.これらは,図2(a)と(b)に赤の破線で示しました.

以上はIN端子の電圧が低電圧のことであり,IN端子が低い電圧から高い電圧へ推移したときの出力電圧変動は,今回のように,ライン・レギュレーションについて注意しなければなりません.

●LDOレギュレータの等価回路

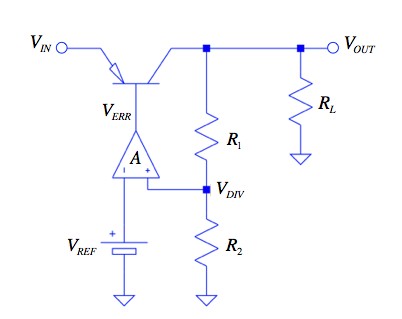

図3は,図1を等価回路で表すため,回路の各ノード(回路の節点)に電圧の記号を付けました.図3のOPアンプは,入力インピーダンスが無限大,出力抵抗がゼロの理想OPアンプとします.

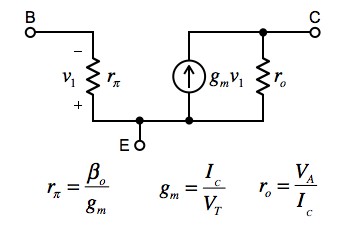

図4は,PNPトランジスタのπ型等価回路です.π型等価回路は,アナログ回路の計算でよく使われます.図4のrπはトランジスタの入力抵抗,gmはトランスコンダクタンス,roは出力抵抗です.図4ではベース・エミッタ間の入力抵抗に印加される電圧v1により,エミッタからコレクタへgmv1の電流が流れることになります.rπ,gm,roは図4中の式で表されます.ここで,βoは電流増幅率,VTは熱温度,VAはアーリー電圧,ICはコレクタ電流です.

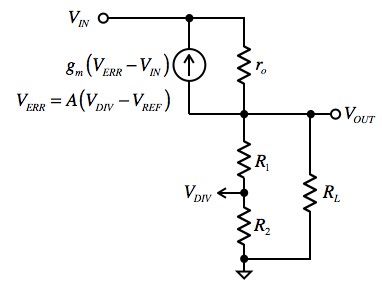

図5は,図3の等価回路で,図4を使って計算しやすく書き直したものです.図5に図4のrπがありませんが,これはOPアンプの出力抵抗をゼロとしたためです.

●等価回路を用いて計算する

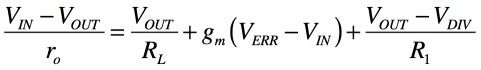

次に図5の等価回路を用い,VINの電圧がVOUTにどのように伝わるかを計算します.まず,キルヒホッフの電流則(KCL)より,VOUTのノードに流れ込む電流の総和をゼロとすると式4になります.

・・・・・・・・・・(4)

・・・・・・・・・・(4)

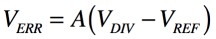

VERRは図5より式5です.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

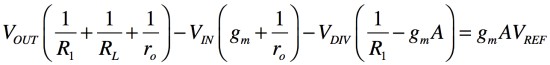

式4と式5を整理すると式6となります.

・・・・・(6)

・・・・・(6)

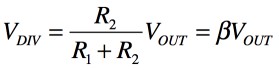

また,R1とR2の分圧回路の電圧VDIVは式7となります.ここでβは式(2)となります.

・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・(7)

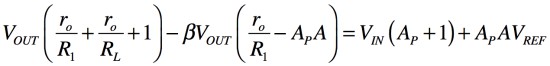

式6と式7整理すると式8となります.

・・・・・(8)

・・・・・(8)

式8の意味を分かりやすくするため,PNPトランジスタ単体のゲインをAPとし「AP=gmro」となるように両辺にroを乗じると式9となります.

・・・・・(9)

・・・・・(9)

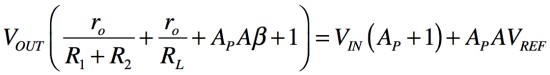

式9をVOUTについて解き整理すると,式10となります.

・・・・・(10)

・・・・・(10)

式10を使い,両辺のどの項が支配的かを評価します.式10の左辺のroは,PNPトランジスタの出力抵抗であり,図4に記載した「ro=VA/IC」の関係とコレクタ電流(IC)は,負荷電流が支配的とすれば「IC=4.96V/100Ω=49.6mA」なので,「VA=100V」より「ro=2kΩ」と近似できます.また,PNPトランジスタのゲイン(AP=gmro)は「gm=IC/VT=49.6mA/26mV=1.9 [A/V]」なので「AP=(1.9A/V)*(2kΩ)=3.8」となります.OPアンプのオープン・ループ・ゲインは,最低でも70dB(=3162)ですので,式10の左辺はAPAβが支配的であることがわかります.

次に右辺が「(AP+1)=AP」と近似すれば,式10の近似式は式11となります.

・・・・・・・・・・・・・・・・・・・・・(11)

・・・・・・・・・・・・・・・・・・・・・(11)

以上より,式11を用いると,VINとVOUTの関係は,解答の式1となります.

●LDOレギュレータをLTspiceで確認する

図6は,図1をシミュレーションする回路です.「.dcコマンド」でIN端子の電圧となるV1の電圧源を10V~30Vにスイープします.また,OPアンプの直流オープン・ループ・ゲインは「.stepコマンド」で4種類変化させました.シミュレーション値は直読できるように「.measコマンド」でV1が10V,20V,30Vのときの値をVo1,Vo2,Vo3の変数へ,10V~30V変化したときの傾きは LineRegの変数へ,10V~30Vの変化に対する出力電圧の変化をdVoの変数へ格納します.

OPアンプの直流オープン・ループ・ゲインを70dB,80dB,90dB,100dBとし,IN端子の電圧が10V~30Vに変化したときの出力電圧をシミュレーションする.

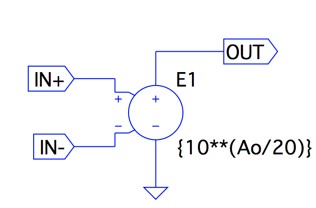

理想OPアンプのサブサーキットは,図7とし「.stepコマンド」のデシベルで与えた数値を,倍率へ変換して与えています.

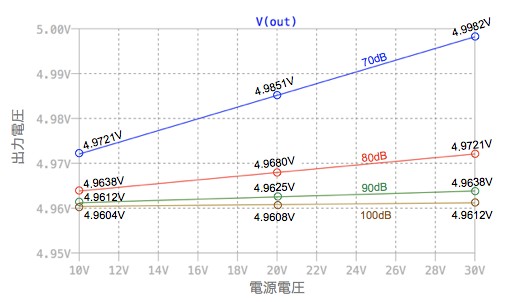

図8は図7のシミュレーション結果です.「.measコマンド」で得られた電圧値をプロットへ加えました.また,IN端子の電圧が10V~30V変化したときのOUT端子の電圧変化は,「.measコマンド」より下記となります.step1は70dB,step2は80dB,step3は90dB,step4は100dBのOPアンプの直流オープン.ループ・ゲインです.このシミュレーション値は,解答で計算した値と一致しています.

| step | vo3-vo1 |

| 1 | 0.0261493 |

| 2 | 0.00826883 |

| 3 | 0.00261497 |

| 4 | 0.000826836 |

「.measコマンド」で得た電圧値をプロットしている.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice3_046.zip

●データ・ファイル内容

LDO_Line_Reg_DC.asc:図6の回路

Ideal_OP.asc:図7の回路

Ideal_OP.asy:図7のシンボル

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs

(6) LTspice電源&アナログ回路入門・アーカイブs