降圧スイッチング電源の位相補償回路

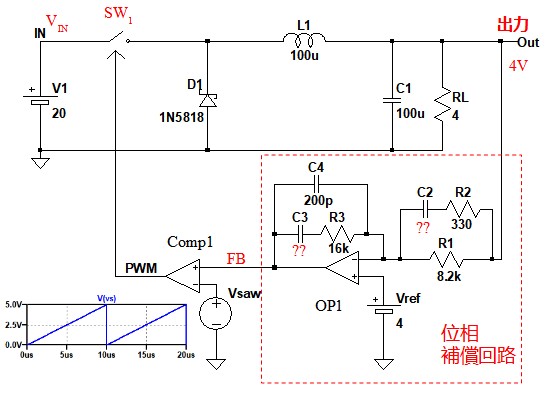

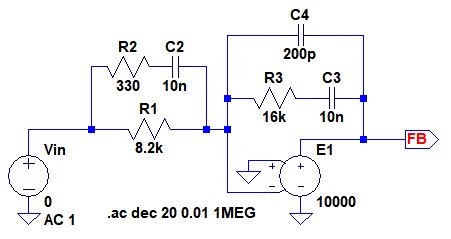

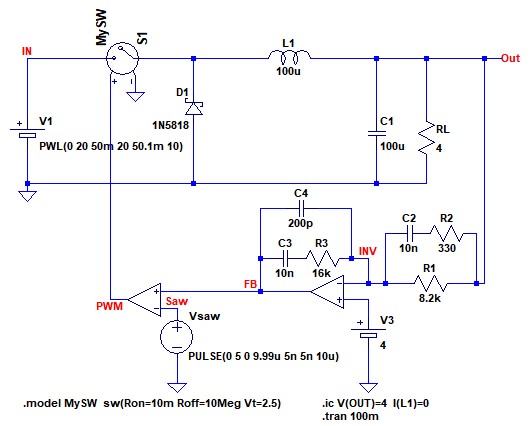

図1は,入力電圧が20V,出力電圧が4Vの降圧スイッチング電源のブロック図です.SW1は,コンパレータ(Comp1)の出力(PWM)がハイレベルのときにONするようになっています.また,Comp1の-入力(Vsaw)には,PWM基準信号として,振幅5Vで100kHzののこぎり波が加えられています.さらに,出力電圧は位相補償回路を介して,Comp1の+入力端子に加えられ,帰還ループを構成しています.図1の降圧スイッチング電源が安定に動作する,位相補償回路のC2およびC3の定数として最も適切なのは(A)~(D)のどれでしょう?

位相補償回路のC2およびC3の定数として最も適切なのは?

図1の位相補償回路は,LCフィルタによって位相が180度回るのを,伝達関数のゼロを利用して補償しています.そのゼロの周波数はC2およびC3の値によって変化します.LCフィルタのカットオフ周波数と,C2およびC3の各定数でのゼロの周波数を比較すると,どれが妥当な値かがわかります.

図1のLCフィルタのカットオフ周波数は約1.6kHzです.一方,図1の位相補償回路のゼロの周波数はfZ1=1/(2πR1・C2)およびfZ2=1/(2πR3・C3)で計算できます.fZ1の周波数はAが1.94MHz,Bが194kHz,Cが19.4kHzでDが1.94kHzです.(A)~(C)の定数でのゼロの周波数は,LCフィルタのカットオフ周波数に比べて高すぎるので,位相補償としての効果が期待できません.そのため正解は(D)ということになります.

●降圧スイッチング電源の位相補償回路に望まれる特性

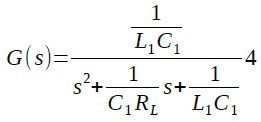

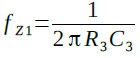

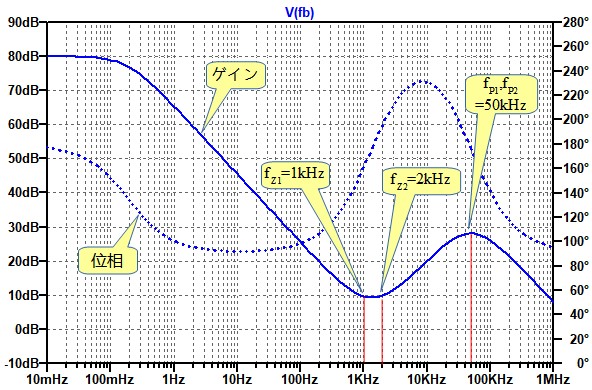

「LTspice電源&アナログ回路入門 040 ―降圧スイッチング電源のゲインと周波数の特性」で解説したように,図1のような降圧スイッチング電源のComp1入力から電源出力端子までのゲイン・周波数特性は図2のようになっています.図1のPWM基準信号の振幅は5Vで入力電圧が20Vなので,Comp1から出力までの直流ゲインは4倍(12dB)です.そしてカットオフ周波数で急激に位相が変化し,180度まで位相が回ります.その伝達関数は式1で表せます.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

カットオフ周波数で急激に位相が変化し,180度まで位相が回る.

図2のような特性を持った電源回路に,発振しないように負帰還をかけるためには,位相補償回路が必要になります.その位相補償回路には次のような特性が望まれます.

1.直流ゲインが十分に高いこと

2.ループゲインが0dB以上のときに位相が180度回転しないこと

3.なるべく高い周波数までループゲインが0dB以上であること

特に2と3は相反する要求になりますが,図1のような位相補償回路を使用することで実現することができます.

●位相補償回路の伝達関数と特性

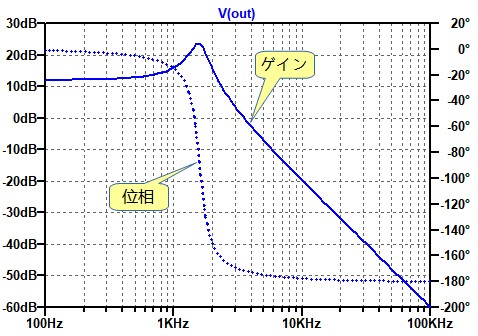

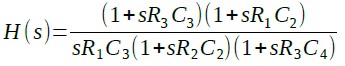

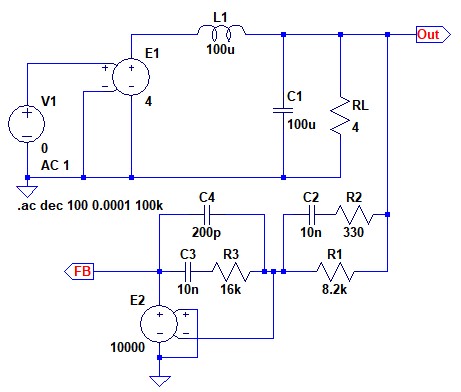

図3は,図1の位相補償回路の部分だけを取り出して,シミュレーション用に書き換えたものです.この回路でR1≫R2,C2≫C4とし,E1のゲインを十分大きいものとすると,伝達関数は式2で近似することができます.

積分回路として動作し,さらに2つのポールと2つのゼロを持っている.

・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・(2)

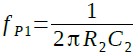

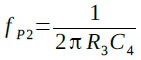

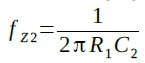

この回路は積分回路として動作し,さらに2つのポールと2つのゼロを持った特性になります.それぞれのポールとゼロの周波数は式3~6で表すことができます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

このポールとゼロの周波数を調整することで,位相補償回路として望ましい特性に近づけていきます.この回路の周波数特性は図4のようになります.6dB/octで減衰してきた特性がフラットになる周波数がfZ1で,上昇に転じる周波数がfZ2です.さらにその後6dB/oct上昇してきた特性がフラットになる周波数がfP1で,再び6dB/octで減衰を始める周波数がfP2です.図3ではfP1=fP2となっています.このようにゼロのある回路を使用することで,ループゲインが下がらないようにするとともに,位相が180度回転してしまうことを防ぎます.

ポールとゼロの周波数を調整し,望ましい特性とする.

●位相補償回路の定数設定例

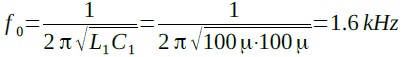

図1のような位相補償回路の定数の設定の方法には,いろいろな考え方がありますが,ここではその一例を紹介します.まず,式7のように図1の回路のL1とC1によるローパスフィルタのカットオフ周波数(f0)を計算します.

・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・(7)

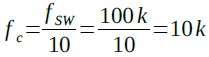

次に帰還ループを構成したときに,ループゲインが0dBとなる周波数(fc)を決めます(式8).fcの周波数は高いほど電源の応答性能が良くなりますが,ここではスイッチング周波数(fsw)の1/10に選びます.ただし,fcはf0の10倍を超えないように設定します.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

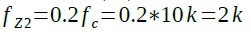

ゼロ周波数(fZ2)は,式9のようにfcの2割で式9のように計算します.

・・・・・・・・・・・・・・・・・・・・・・・・・(9)

・・・・・・・・・・・・・・・・・・・・・・・・・(9)

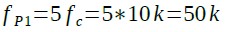

ポール周波数(fP1)は,fcの5倍として式10のように計算します.

・・・・・・・・・・・・・・・・・・・・・・・・・・(10)

・・・・・・・・・・・・・・・・・・・・・・・・・・(10)

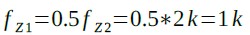

ゼロ周波数(fZ1)は,fZ2の半分に設定し,式11のように計算します.

・・・・・・・・・・・・・・・・・・・・・・・・・(11)

・・・・・・・・・・・・・・・・・・・・・・・・・(11)

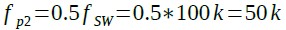

ポール周波数(fP2)は,スイッチング周波数(fsw)の半分に設定し,式12のように計算します.

・・・・・・・・・・・・・・・・・・・・・・(12)

・・・・・・・・・・・・・・・・・・・・・・(12)

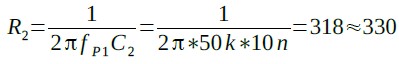

各周波数が決まったら素子の定数を決めていきます.まずC2を10nFに決めます.そして,式3を変形して式13のようにR2を計算します.

・・・・・・・・・・・・・・・(13)

・・・・・・・・・・・・・・・(13)

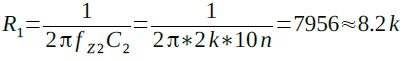

次に式6を変形して式14のようにR1を計算します.

・・・・・・・・・・・・・・・(14)

・・・・・・・・・・・・・・・(14)

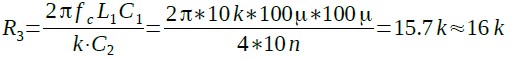

周波数がfcのときにループゲインが0dBとなるように,式15を使ってR3の値を求めます.ここでkはPWMコンパレータのゲインです.

・・・・・・・(15)

・・・・・・・(15)

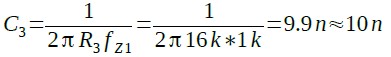

次に,式5を変形して式16のようにC3を計算します.

・・・・・・・・・・・・・・・(16)

・・・・・・・・・・・・・・・(16)

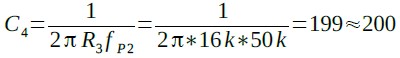

最後に式4を変形して式17のようにC4を計算します.

・・・・・・・・・・・・・・・(17)

・・・・・・・・・・・・・・・(17)

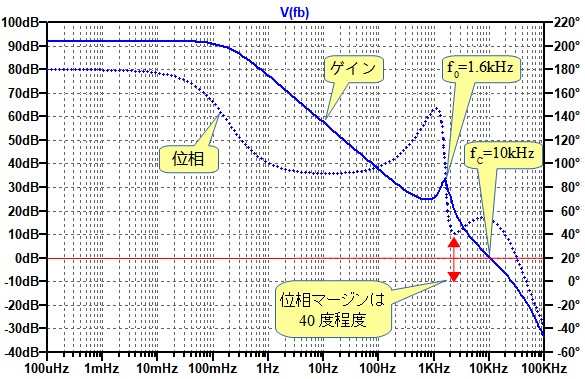

●ループ全体の周波数特性

図5は,ループ全体の周波数特性をシミュレーションするための等価回路です.

ループ全体の周波数特性をシミュレーションする.

図6は図5の周波数特性のシミュレーション結果です.ゲインが0dBとなる周波数(fc)は目標値とした10kHzとなっていることがわかります.また,ゲインが0dBよりも大きい状態で,最も位相が遅れている周波数は2.5kHzで,そのときの位相マージンは40度程度となっています.一般的には位相マージンは45度以上を目標としますので,それよりは若干小さめになっています.

fcは10kHzで位相マージンは40度程度となっている.

●単純な積分回路位相補償で入力電圧が変化したときの出力電圧

電源回路では,入力電圧や出力電流が変化したとき,出力電圧がどのように応答するかという特性が重要です.そこで,単純な積分回路による位相補償回路と,図1の位相補償回路の特性がどのように違うか,シミュレーションで確認します.

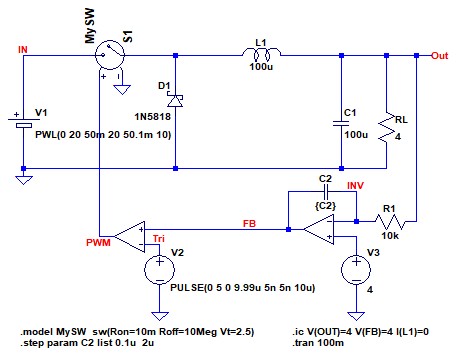

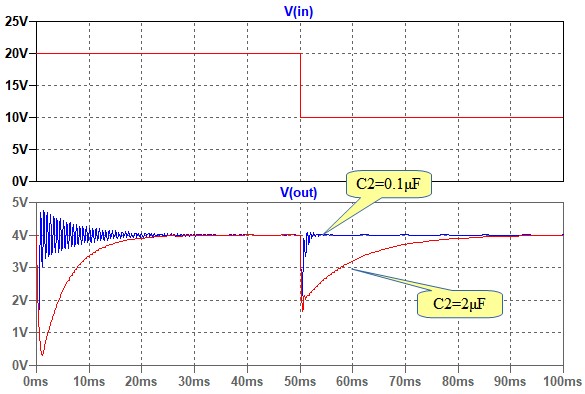

図7は,比較用に用意した,単純な積分回路による位相補償回路を使用した降圧スイッチング電源です.初期入力電圧を20Vとし,50msec後に10Vに低下させたときの出力電圧の応答をシミュレーションします.なお,積分時定数を決めるC2の値は0.1μFと2μFの2種類を「.stepコマンド」で切り替えます.

C2の値は0.1μFと2μFの2種類を「.stepコマンド」で切り替える.

図8は,図7のシミュレーション結果です.C2が0.1μFのときは電圧切り替えときにリンギングが発生して不安定となり,2μFのときは,出力電圧が安定するまで20msec以上の時間がかかっています.

C1が小さいと出力が不安定となり,大きいと応答が遅くなる.

●伝達関数のゼロを利用した位相補償で入力電圧が変化したときの出力電圧

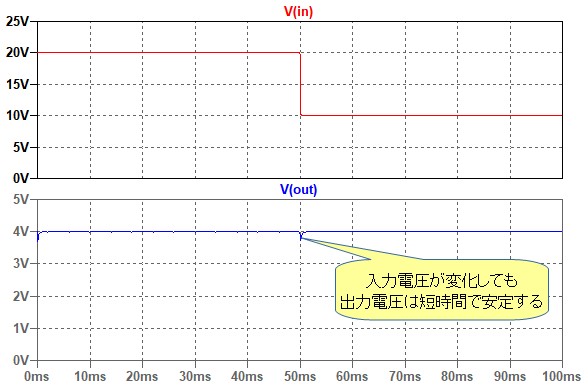

図9は,図1の位相補償回路の定数を,式13~17で計算した値とした,シミュレーション用の回路図です.図7同様,入力電圧を20Vから10Vに変化させたシミュレーションを行います.

入力電圧を20Vから10Vに変化させたシミュレーションを行う.

図10は,図9のシミュレーション結果です.図8と比べると,入力電圧が変化した直後の電圧の落ち込みが小さく,すぐに安定した電圧となっていることがわかります.

以上,降圧スイッチング電源の位相補償回路に関して解説しました.ここでは省略しましたが,出力コンデンサ(C1)の直列抵抗成分はループの安定性に大きな影響があります.また,スイッチング周波数が高くなるとPWMコンパレータの応答速度なども,ループ特性に影響をあたえますので,実際の回路では,それらを含めた位相補償回路の定数調整が必要になります.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice3_042.zip

●データ・ファイル内容

PID.asc:図3の回路

LC_LPF_PIDNF.asc:図5の回路

Step_down_PWM_INT_Step.asc:図7の回路

Step_down_PWM_PID.asc:図9の回路

LimitAmp.asy:図7,図9の回路で使用しているコンパレータのシンボル

LimitAMP.asc:図7,図9の回路で使用しているコンパレータの内部回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs