ツェナー・ダイオードを使ったシャント・レギュレータの温度補償

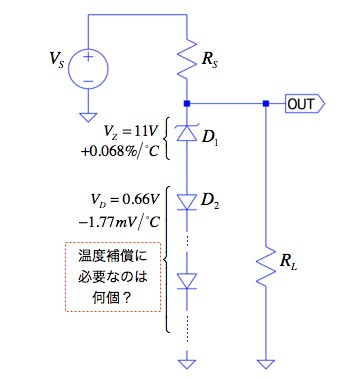

図1は,ツェナー・ダイオード(D1)を利用した簡単なシャント・レギュレータです.今回使用するD1の性能は,テスト電流(IZT)が5mAのとき,電圧(VZ)が11V,微分温度係数(TC)が+0.068%/℃です.

図1には,温度補償の目的でD1からGND間に,ダイオード(D2)を直列に接続します.D2は,-1.77mV/℃の温度係数であり,D1の正の温度係数を打ち消すのが狙いです.

この回路においてD1の微分温度係数を打ち消すため,直列に接続するD2の最適な個数は(a)~(d)のどでれでしょうか.

D1正の温度係数をD2の負の温度係数で補償する.

今回は,ツェナー・ダイオードを使ったシャント・レギュレータの温度補償について解説します.まず,図1の回路において,ツェナー・ダイオードの微分温度係数を1℃あたりの電圧の変化へ換算します.その値をダイオードの温度係数で打ち消すために,何個必要かを計算します.

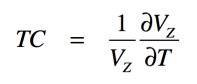

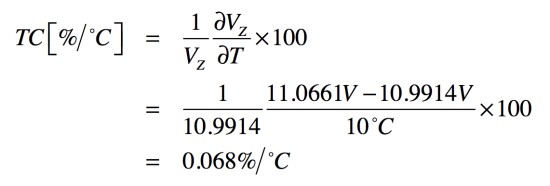

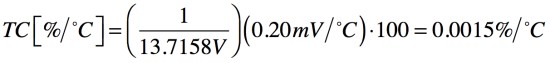

ツェナー・ダイオードの温度係数は,微分温度係数を百分率に直した単位(%/℃)を使うのが一般的です.微分温度係数(TC)は式1となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

図1のツェナー・ダイオード(D1)の微分温度係数(TC)は,+0.068%/℃ですので「TC=+0.00068/℃」です.また,ツェナー・ダイオードの電圧(VZ)は,11Vなので式1より1℃あたりの電圧の変化を求めると,式2となります.

・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・(2)

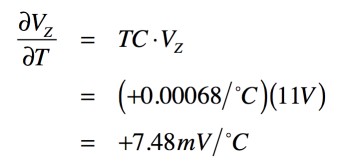

温度補償に使うダイオード(D2)の1℃あたりの変化は「-1.77mV/℃」の負の温度係数ですのでD2を直列に接続して,式2の「+7.48mV/℃」を打ち消す最適な個数は,式3のように4個となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

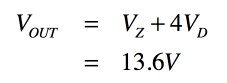

このときの出力電圧(VOUT)は,式4となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

●ツェナー・ダイオードの温度特性

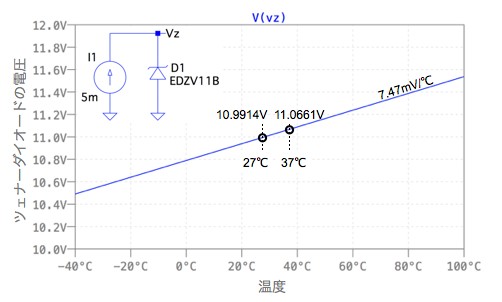

今回は,EDZV11Bのツェナー・ダイオードを用いて解説します.EDZV11Bは,テスト電流(IZT)が5mAのとき,電圧(VZ)が11Vとなるツェナー・ダイオードで+0.068%/℃の正の温度係数を持ちます.図2へEDZV11Bの温度特性を示します.

テスト電流(IZT)は5mA,電圧(VZ)は11V,温度係数(TC)は+0.068%/℃となっている.

図2の27℃と37℃のツェナー・ダイオードの電圧より,1℃あたりの電圧変化は7.47mV/℃です.この温度変化を,百分率に直した微分温度係数で表せば,式5の0.068%/℃となります.解答では式5の逆の計算をおこない,1℃あたりの電圧変化を求めています.

・・・・・(5)

・・・・・(5)

●温度補償した効果をLTspiceで確かめる

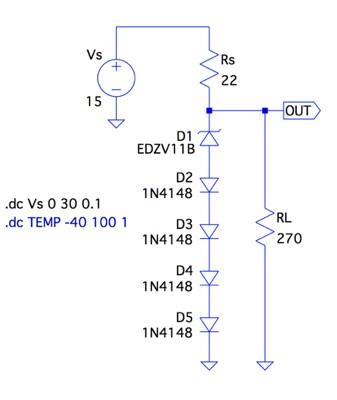

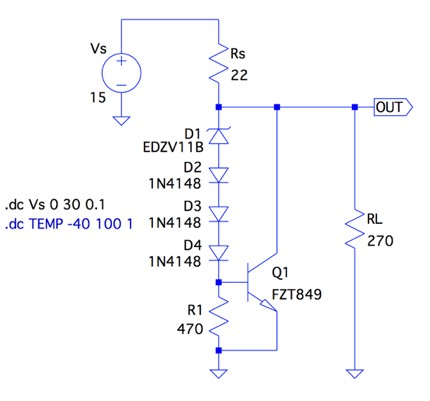

図3は,図1シミュレーションする回路です.解答で求めた4つのダイオード(D2,D3,D4,D5)を直列に接続しました.電源電圧(VS)は15V,抵抗(RS)は22Ω,負荷抵抗(RL)は270Ωとし,負荷電流が約50mAとなります.また,ツェナー・ダイオード(D1)の許容損失(PD)は150mWです.また,ダイオード(D2,D3,D4,D5)は,汎用スイッチング・ダイオード(1N4148)で許容損失(PD)が500mWです.

D2,D3,D4,D5の4つのダイオードを直列に接続した.

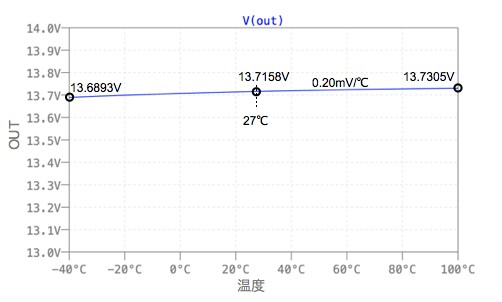

図4は,図3で温度を-40℃~100℃間をスイープし,出力電圧の変化を調べた結果です.このときのシミュレーションは,図3中の「.dc TEMP -40 100 1」を用いています.ツェナー・ダイオード(D1)は,図2で調べたように温度係数(TC)が0.068%/℃で,1℃あたりの変化(∂VZ/∂T)に直すと7.47mV/℃です.この温度係数を,直列に接続したダイオード(D2,D3,D4,D5)の負の温度係数により打ち消し合って,0.2mV/℃の低い温度変化となり改善しています.百分率で表した微分温度係数は,式6となります.

・・・・・(6)

・・・・・(6)

温度 対 出力電圧(OUT)をプロット.

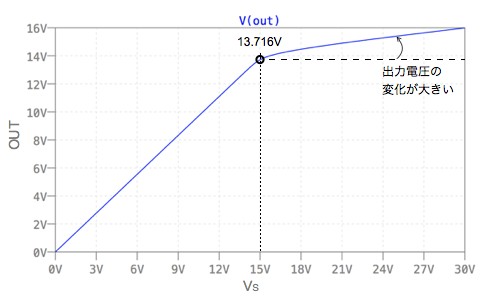

次に,図3の弱点について考えます.図5は,電源電圧(VS)の変化による出力電圧(OUT)の変化です.図5のシミュレーションは,図3中の「.dc Vs 0 30 0.1」を用いています.図5では,電源電圧(VS)が15Vから高くなると,ツェナー・ダイオード(D1)からダイオード(D2,D3,D4,D5)へ流れる電流が多くなり,ダイオードの順方向電圧が大きくなることから,出力電圧の変化が大きくなる弱点があります.

電源電圧(VS)対 出力電圧(OUT)をプロット.

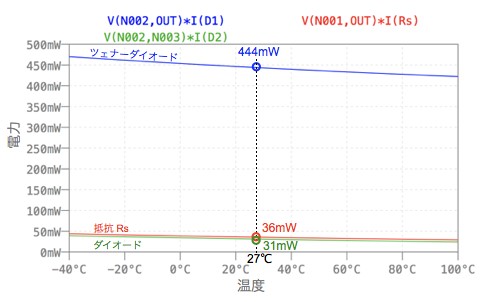

図6は負荷抵抗(RL)を削除し,ツェナー・ダイオード(D1)側に多くの電流が流れたときの消費電力の温度特性を示しました.図6では,ツェナー・ダイオード(EDZV11B)の電力が大きくなり,許容損失の150mWを超えてしまいます.

負荷抵抗を外したときの各素子の消費電力.

●トランジスタを使い電流パス経路を設ける

図3の弱点を対策した回路が図7となります.変更箇所は,ダイオード(D5)を削除し,許容損失(PD)1.6WのNPNトランジスタ(FZT849)と抵抗(R1)を追加しました.D5の負の温度係数は,NPNトランジスタ(Q1)のベース・エミッタの負の温度係数で代替します.また,コレクタは出力(OUT)に接続し,新たに電流のパス経路を設けました.この変更により,ツェナー・ダイオード(D1)とダイオード(D2,D3,D4)に流れる電流は少なくなるので,図5と図6の弱点が対策できます.

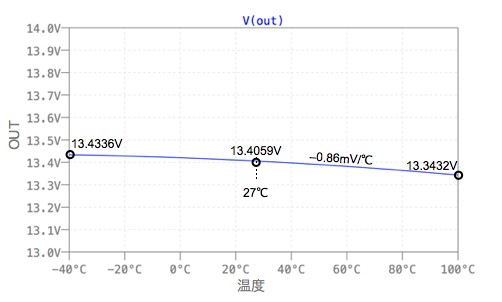

図8は,温度の変化による出力電圧の変化です.D1の正の温度係数を,D2,D3,D4とQ1のベース・エミッタの負の温度係数で打ち消し-0.86mV/℃となります.これは式6と同様の計算をすると-0.0064%/℃です.

温度 対 出力電圧(OUT)をプロット.

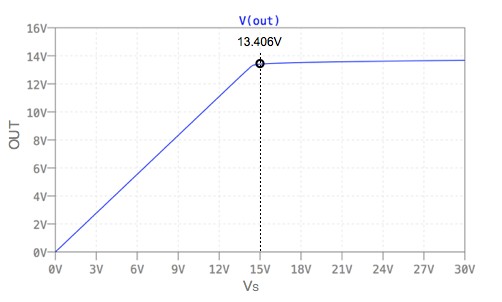

図9は,電源電圧(VS)の変化による出力電圧(OUT)の変化です.図9は,図5の特性を改善した結果で電源電圧が15Vから高くなっても出力電圧の変化は小さくなります.

電源電圧(VS)対 出力電圧(OUT)をプロット.

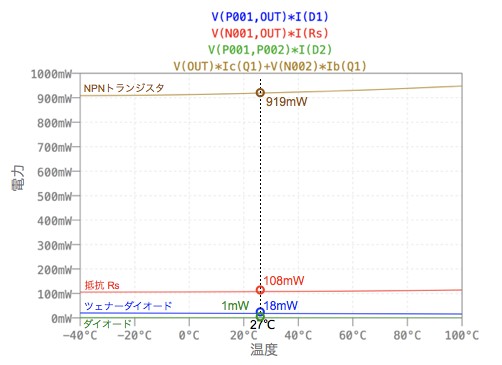

図10は,負荷抵抗(RL)が無いときの温度変化による消費電力の変化を示します.図10は,図7のD1の消費電力を150mW以内に入るように対策した結果です.Q1の新たな電流経路により,ツェナー・ダイオード(D1)に流れる電流が少なくなるので18mWとなります.代わりにQ1の消費電力は919mWとなりますが,FZT849の許容損失は1.8W以内になります.

負荷抵抗を外したときの各素子の消費電力.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice3_027.zip

●データ・ファイル内容

Zenner_Shunt_Ref_Temp_compensation_1.asc:図3の回路

Zenner_Shunt_Ref_Temp_compensation_2.asc:図7の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs