ブロコウ・セル 基準電圧源の温度補償

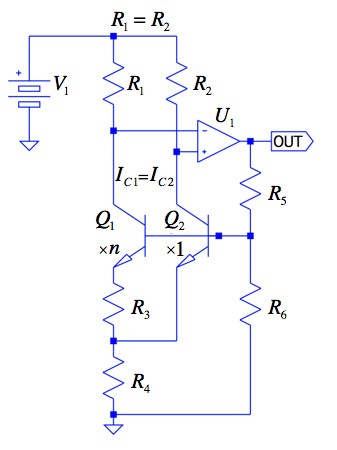

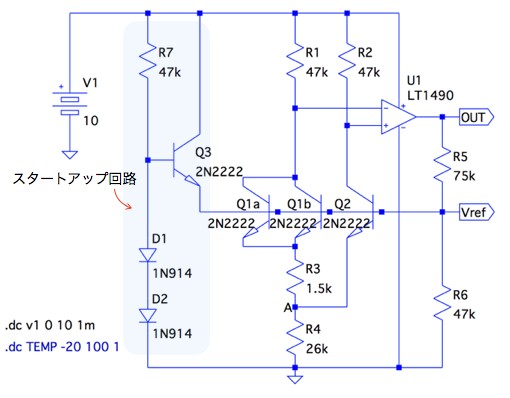

図1は,OUT端子が出力となるブロコウ・セルと呼ばれる基準電圧源(バンドギャップ・リファレンス)です.回路の条件として,Q1とQ2のトランジスタの比はn:1としました.また,抵抗(R1,R2)の値を同じとすると,OPアンプ(U1)を使った帰還ループにより,Q1とQ2のコレクタ電流が等しくなるように制御しています.

図1のブロコウ・セルは,抵抗比を調整することにより温度補償できます.温度補償ができる抵抗比は(a)~(d)のどれでしょうか.ここで計算を簡単にするため,Q1とQ2のベース電流は無視します.

今回は,ブロコウ・セルと呼ばれる基準電圧源について解説します.ブロコウ・セルは,n:1の2つのトランジスタQ1とQ2に同じ電流を流し,そのベース・エミッタ電圧差(ΔVBE)がR3の両端に加わります.ΔVBEは正の温度係数を持ち,Q2のベース・エミッタ電圧(VBE2)の負の温度係数を打ち消して温度補償をします.この回路動作をヒントに,OUT端子の電圧式を導くことにより,どの抵抗比が温度補償に関係しているか分かります.

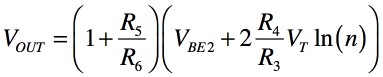

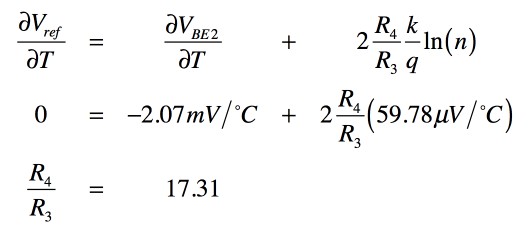

詳細は解説で説明しますが,ブロコウ・セルのOUT端子の電圧は式1となります.

・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・(1)

式1の右辺より温度によって変化するのは,負の温度係数を持つQ2のベース・エミッタ電圧VBE2と熱電圧VTに関係する項です.熱電圧(VT)は「VT=kT/q(Tは絶対温度,kはボルツマン定数,qは電子電荷)」ですから,正の温度係数となります.この正の温度係数を2(R4/R3)ln(n)倍し,VBE2の温度係数の符号を正にした値に近づけることにより,互いに打ち消しあって温度補償ができます.よって,ブロコウ・セルの温度補償は,R4:R3の比を適切に選ぶことになります.出力電圧VOUTの絶対値は,(1+R5/R6)のゲインで調整します.抵抗の温度係数が等しければ,温度による抵抗比の変化はありません.

●ブロコウ・セルの出力電圧ついて

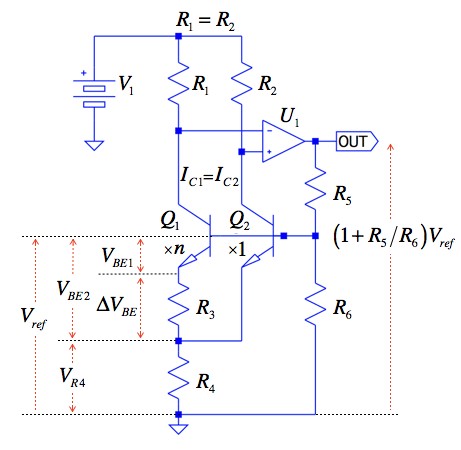

図2は,図1のブロコウ・セル内の電圧を示しました.この図を使い,出力電圧VOUTを調べます.

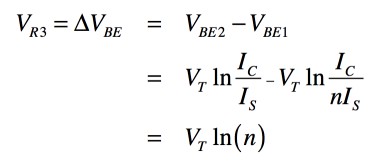

ブロコウ・セルは「R1=R2」とすると,OPアンプ(U1)の帰還ループにより,Q1とQ2のコレクタ電流が等しくなります.よって,コレクタ電流は「IC=IC1=IC2」の関係があり,Q1の逆方向飽和電流がnIS,Q2がISとなります.Q1とQ2のトランジスタ比はn:1であるため,異なる電流密度で動作します.すると,式2のようにVBE1とVBE2の差であるΔVBEがR3の両端の電圧となります.

・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・(2)

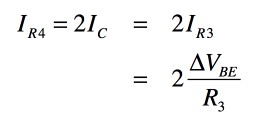

式2のΔVBEを使い,R4に流れる電流を表すと式3となります.

・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・(3)

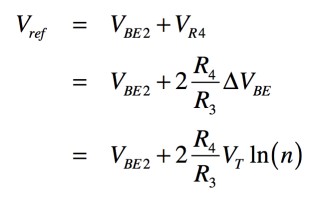

式2と式3を使い,Q1とQ2のベース電圧をVrefとし「VR4=IR4R4」より,式4となります.

・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・(4)

出力電圧VOUTは,式4のVrefの電圧を(1+R5/R6)のゲインで増幅した値となり,式5となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

以上より,式4と式5を使って出力電圧を表すと,式1となります.

●ブロコウ・セルの温度補償ついて

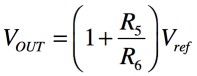

次に式4を使い,ブロコウ・セルの温度補償について考えます.式4の右辺はQ2ベース・エミッタ間電圧VBE2の負の温度係数の項と熱電圧VTを2(R4/R3)ln(n)倍した正の温度係数の項となります.温度補償をするには,正と負の温度係数で打ち消せば,Vrefの電圧は温度に対して変化が小さくなります.

ここで,具体的なR4:R3の比を計算で求めます.式4の温度変化は,温度Tで微分すれば求められ,その計算結果に,具体的な数値として,次の値を入れた計算が式6となります.

∂VBE2/∂T=-2.07[mV/℃]:VBE2の負の温度係数(あらかじめ調べた値)

n=2:Q1:Q2=2:1

k=1.38×10-23[J/K]:ボルツマン定数

q=1.6×10-19[C]:電子電荷

・・・・・・・(6)

・・・・・・・(6)

図1のシミュレーションをするため,他の抵抗値の具体例を計算すると次のようになります.

・式6の比より,R3が1.5kΩのとき,R4は26kΩとなります

・OPアンプは入力がレール・ツー・レールを用い,同相入力電圧範囲から余裕をみて,R1とR2の電圧降下が0.56Vとする抵抗値より「R1=R2=47kΩ」となります

・VBE2が540mVとすると,式4よりVrefは1.16Vとなります.出力端子の電圧を約3Vを目標にすると,式5より「R5/R6=1.59」となりR6を47kΩとすれば,R5は75kΩとなります

●スタートアップ回路について

先に求めたR4:R3の比と,その他の抵抗値を入れた回路が図3となります.「Q1:Q2=2:1」とするため,Q1はQ1aとQ1bの2つのトランジスタで表しました.OPアンプは入出力がレール・ツー・レールのLT1490を用いています.

スタートアップ回路を追加している.

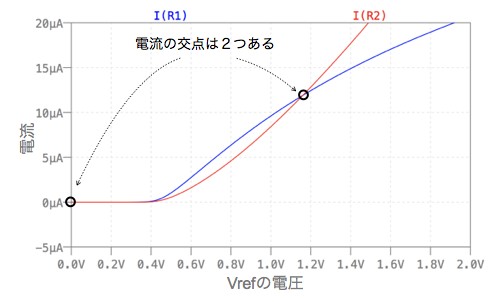

ブロコウ・セルは,OPアンプの帰還ループにより,Q1とQ2のコレクタ電流が等しくなり,R1とR2に流れる電流が等しいところで安定します.しかし,図4に示すように,流れる電流の交点は2つあり,どちらに落ち着くかは不定となる回路です.左側の交点で落ち着くと電流は流れず,ブロコウ・セルは動きません.よって,右側の交点で落ち着かせるには,ブロコウ・セルを起動する回路が必要となり,図3には新たにスタートアップ回路を加えました.

このスタートアップ回路は,Vrefの電圧が約1.2Vより十分低いとき,Q3からQ1とQ2のベースへ電流を流します.起動するとVrefの電圧は約1.2Vになり,Q3のベース・エミッタ間の電圧が小さくなって停止します.

2つの電流が交わる交点は2つあり,どちらかに落ち着く.

●ブロコウ・セルの特性をシミュレーションで確かめる

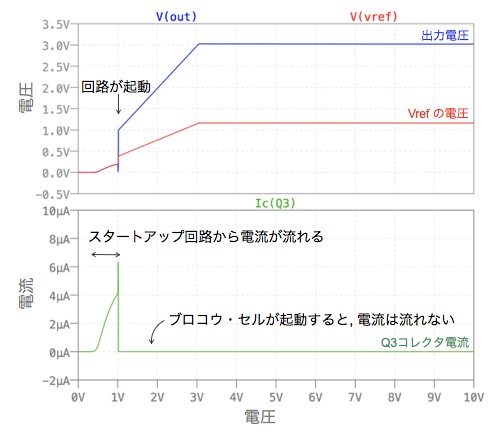

図5は,図3の回路でV1を0Vから10VまでスイープしたときのVrefとVOUTの電圧およびQ3の電流をプロットしました.V1が約1Vより低いときは,Q3からブロコウ・セルへ電流が流れ,回路が起動すると停止する様子が分かります.また,VrefやVOUTの電圧は,V1の電圧が約3V以上で定電圧になることが分かります.

約1V以下はスタートアップ回路が動作し,ブロコウ・セルを起動している.

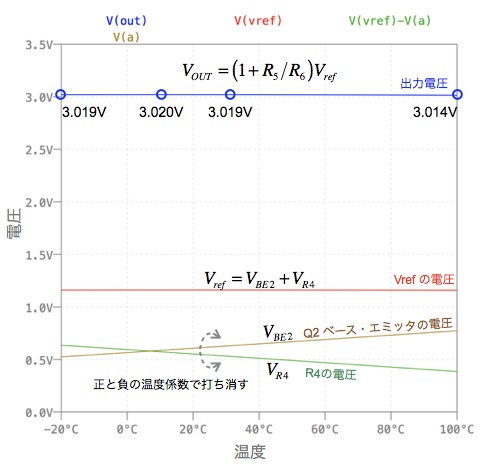

図6は,図3の回路で,温度を-20℃から100℃間でスイープしたときのVBE2,VR4,Vref,VOUTの電圧をプロットしました.Vrefの温度係数は,VBE2の負の温度係数とVR4の正の温度係数で打ち消しているので,温度による変化は小さく,VOUTはVrefを(1+R5/R6)のゲインで増幅していることがわかります.また,温度が変化してもVOUTの電圧変化が小さい電圧源として動作しているのも分かります.

温度変化による出力電圧の変化は小さい.

図3では説明のため,Q1とQ2の比を2:1としましたが,集積回路ではもう少し大きな比(例えば8:1,10:1など)としています.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice3_021.zip

●データ・ファイル内容

Brokaw_Cell.asc:図3の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs