NチャネルJFET電流源の出力電流と温度補償

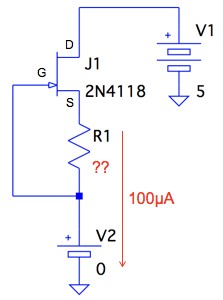

図1は,J1(2N4118)のNチャネルJFETを用いた電流源です.J1のゲート・ソース電圧は,抵抗R1の電圧降下により自己バイアスし,赤矢印で示した電流を調整できます.

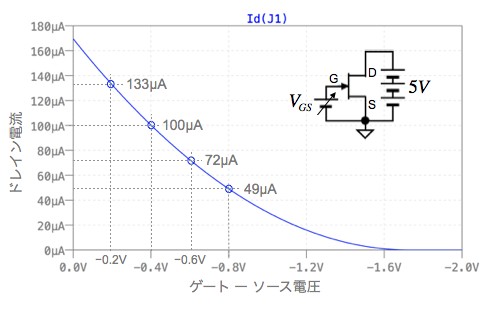

図2は,図1で使用している2N4118のVGS-ID特性を示しました.この場合,赤矢印で示した電流を100μAにするにはR1の抵抗値を(a)~(d)のどれにすれば良いでしょうか. なお,計算を簡単にするため,J1の出力抵抗は無限大,V2は0Vとします.

J1のソースからR1を通りV2へ電流が流れる.

縦軸がドレイン電流(ID)で,横軸がゲート・ソース電圧(VGS).ゲート・ソース電圧が-0.2V,-0.4V,-0.6V,-0.8Vのときのドレイン電流(133μA,100μA,72μA,49μA)を表記している.

2N4118の特性として,ゲートとソースを短絡(0V)したときの最大のドレイン電流が160μAで,0Aの場合[VGS(OFF)]が-2Vとなる.

今回は,NチャネルJFETを用いた電流源について解説します.NチャネルJFETの特徴は,ゲート・ソース電圧(VGS)が0Vのとき,最大の電流となります.また,ゲート・ソース電圧を負にすることで,ドレイン電流が減るデプレッション型となります.図1のJ1のゲート・ソース電圧は,ソースから流れ出る電流と抵抗R1の電圧降下によって負帰還となり,適切にバイアスされます.これを自己バイアスと呼びます.ソース電流は,ドレイン電流と等しいことから図2を使って目的の電流値に必要な自己バイアス電圧を求め,ソース電流と抵抗R1の電圧降下の関係より求めることができます.

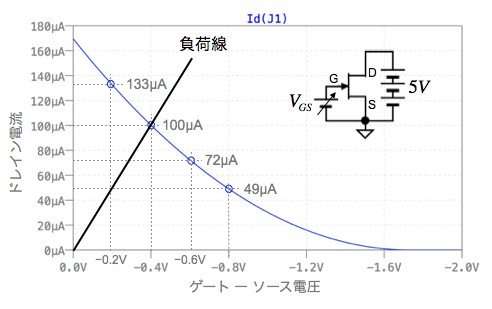

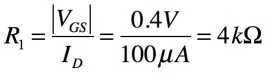

図3は,図2のVGS-ID特性に,ドレイン電流(ID)が100μAとなる負荷線をひきました.負荷線との交点より,NチャネルJFETのゲート・ソース電圧(VGS)が-0.4Vのとき,ドレイン電流(ID)が100μAとなることが分かります.よって,図1の回路では,抵抗R1とソース電流による電圧降下を0.4Vとすれば,ドレイン電流(ID)が100μAとなります.以上より,式1を使って「R1=4kΩ」と求まります.よって,(b)3.9kΩとなります.

・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・(1)

●NチャネルJFETの特性

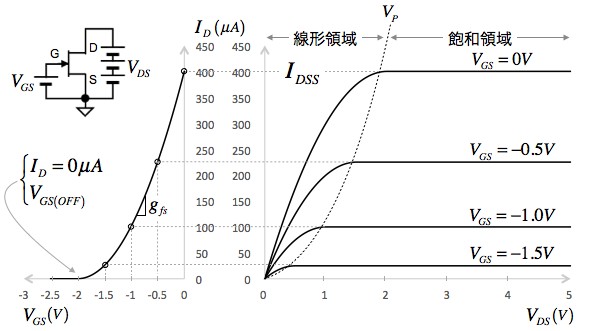

今回は,JFETの特性が鍵となります.そこで,まずNチャネルJFETについて解説します.図4は,図中左上の回路で測定した結果で,NチャネルJFETのVGS-ID特性とVDS-ID特性をプロットしています.JFETは,LTspiceのNチャネルJFETを選ぶと,デフォルトのデバイスは「NJF」です.

NチャネルJFETはゲート・ソース電圧を負にすることでドレイン電流が減ります.図4左のVGS-ID特性より,ドレイン電流(ID)がゼロになる電圧をVGS(OFF)で表します.ゲート・ソース電圧のわずかな変化に対するドレイン電流の変化(dID/dVGS)は,コモンソースにおけるフォワード・トランスコンダクタンスであり,gfsの記号で表します.

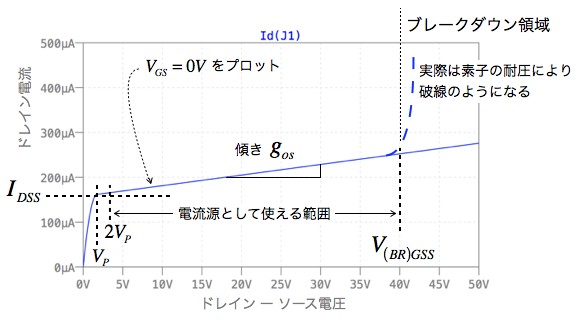

図5は図1で使用したNチャネルJFETの2N4118を使用し,VGSが0VのVDS-ID特性を0~50Vのドレイン・ソース電圧でプロットしました.

JFETにはドレイン・ソース電圧(VDS)で分類すると,大きく分けて3つの動作領域があり,1つ目は図4に示す線形領域,2つ目は飽和領域,3つ目は図5のブレークダウン領域です.図4の線形領域と飽和領域の境目をピンチオフ電圧(VP)と呼びます.線形領域は電圧制御抵抗として使われる領域で,AGCアンプのゲイン調整などに使われます.ピンチオフ電圧(VP)より右側の飽和領域は,増幅や電流源などに使われます.

また,図5のPN接合の耐圧以上となるブレークダウン領域は,デバイスが正常に動かない領域であり使用できません.LTspice(他のSPICEも同じ)は,PN接合の耐圧に関するパラメータが無いので,シミュレーション上にブレークダウン領域がありません.しかし,実際は図5のドレイン・ソース電圧が40V以上で示した破線のように,ドレイン電流が急激に増加する領域となります.

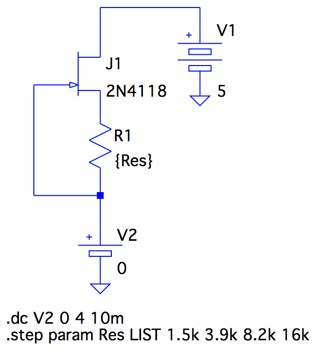

●NチャネルJFET電流源をLTspiceで確かめる

図6は,図1をシミュレーションする回路です.電流源の出力電流はV2に流れる電流で測定します.R1の抵抗値は「.stepコマンド」で1.5kΩ,3.9kΩ,8.2kΩ,16kΩと変化させました.このR1の4つの抵抗値は,図2で示した電圧と電流から求めた抵抗値(入手しやすい抵抗値)となっています.具体的な計算は「0.2V/133μA=1.5kΩ」,「0.4V/100μA=4kΩ」,「0.6V/72μA=8.3kΩ」,「0.8V/49μA=16.3kΩ」となります.

出力電流はV2に流れる電流で測定.また,R1の抵抗値を 1.5kΩ,3.9kΩ,8.2kΩ,16kΩと変化させている.

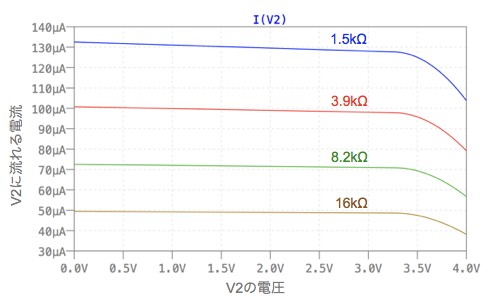

図7は,図6のシミュレーション結果です.電流源の出力電流が100μAに近いのは,R1が3.9kΩであることが分かります.またV2が変化しても100μAの出力電流は大きく変化せず,電圧の変化に対し電流の変化が少ない電流源になっているのが分かります.

また,他の抵抗値(1.5kΩ,8.2kΩ,16kΩ)も,図2の電流値(133μA,72μA,49μA)に近い値なので,R1を可変抵抗にすれば,電流値の調整ができるということが分かりました.このようにNチャネルJFETと抵抗のわずか2素子で電流源回路が構成できます.

R1が3.9kΩの場合,出力電流が100μAに近いことが分かる.

●NチャネルJFET電流源の温度補償

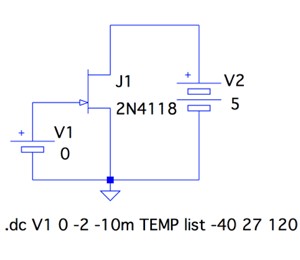

NチャネルJFETのVGS-ID特性の温度を調べると,ドレイン電流が,温度変化に影響を受けない値(温度係数ゼロ)があります.これを調べる回路が図8です.今回は広い範囲で測定するために,-40℃,+27℃,+120℃の温度で,VGS-ID特性をシミュレーションします.

-40℃,+27℃,+120℃の3つの温度で調べる.

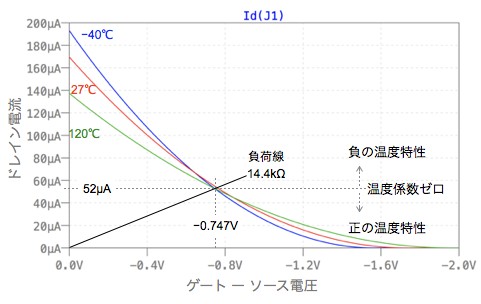

図9は,図8のシミュレーション結果です.シミュレーション結果で,3つの温度のVGS-ID特性がほぼ交差するところが温度係数ゼロとなります.温度係数ゼロのゲート・ソース電圧(VGS)が0.747V,ドレイン電流(ID)が52μAとなるので,この場合の負荷線は14.4kΩ(0.747V/52μA)となります.したがって,図1のNチャネルJFETを用いた電流源回路のR1を14.4kΩに近い値にすれば,温度補償が可能です.

負荷線が14.4kΩで3つの曲線が近くなり,温度係数がゼロとなる.

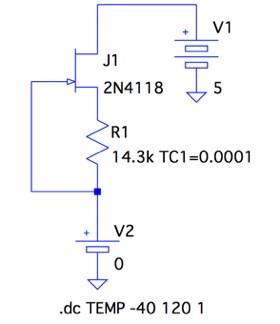

図10は,R1を図9で求めた負荷線の14.4kΩより,入手しやすい14.3kΩとして,NチャネルJFETを用いた電流源回路です.R1の温度係数は+100ppm/℃としました.出力電流の温度特性を調べるため,-40℃~120℃間を1℃ステップでシミュレーションします.

出力電流はV2に流れる電流を測定.

図11は,図10のシミュレーション結果です.27℃付近で出力電流の温度特性がピークになり,52μA~53μAの間で温度補償されているのが分かります.

27℃付近で温度特性がピークになり,温度補償されているのが分かる.

●NチャネルJFET電流源の出力電流の変化を抑える

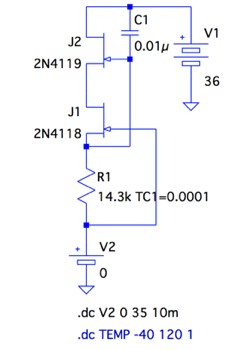

図12は,V2の電圧変化に対し出力電流の変化を抑えるため,図10の回路に,もう1つNチャネルJFET[J2(2N4119)]をカスコード接続で追加しました.図10の回路に,NチャネルJFETを追加することで,電流源の出力抵抗が上がり,V2の電圧変化に対し出力電流の変化を抑えます.

カスコード接続するJ2は,J1より大きなVGS(OFF)が必要で,また,IDSSも大きい必要があります.そこで,VGS(OFF)が-4V,IDSSが400μAの2N4119を使いました.C1は安定動作させるためのコンデンサです.

シミュレーションは,V1を36Vとし,V2が0Vから35Vの間で変化したときの電流源の出力電流変化を調べます.また,「.dcコマンド」を「.dc TEMP -40 120 1」と変更し,V1が36V,V2が0Vのとき-40℃~120℃間の出力電流温度特性をシミュレーションします.図12には温度解析の「.dcコマンド」をコメントで入れましたので,変更するときの参考にしてください.

出力抵抗を大きくし,V2の電圧変化に対し出力電流の変化を抑えるのが狙い

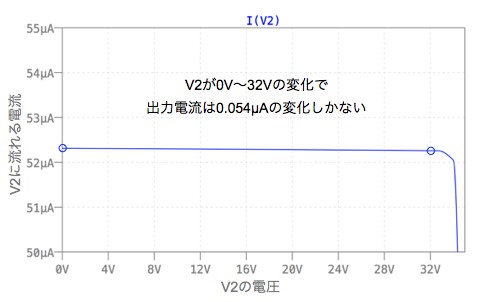

図13は,V2が0V~35V変化したときの出力電流変化です.このときの出力電流はV2が0V~32Vの変化に対し0.054μAしか変化しません.

出力抵抗が大きくなり,出力電流は0V~32V間で0.054μAしか変化しない.

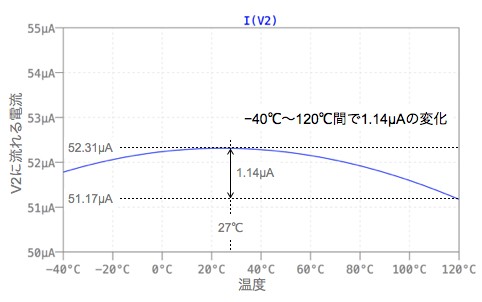

また,図14は温度特性で図11の結果と同じように,27℃付近を中心に温度補償ができています.このように4素子で電源電圧変動や温度変化に対し出力電流の変化が少ない,高耐圧の電流源を作ることができます.NチャネルJFETを用いた電流源はデバイスの特性が鍵ですので,シミュレーションだけでなく,実際の回路で検証することを忘れないでください.

27℃付近をピークに温度補償されている.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice3_013.zip

●データ・ファイル内容

JFET_Current_Source.asc:図6の回路

Transfer_Characteristics_ZeroTC.asc:図8の回路

JFET_Current_Source_Temp_Compensation.asc:図10の回路

JFET_Current_Source_Cascode.asc:図12の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs