正しく動くブートストラップ型スイッチング電源は?

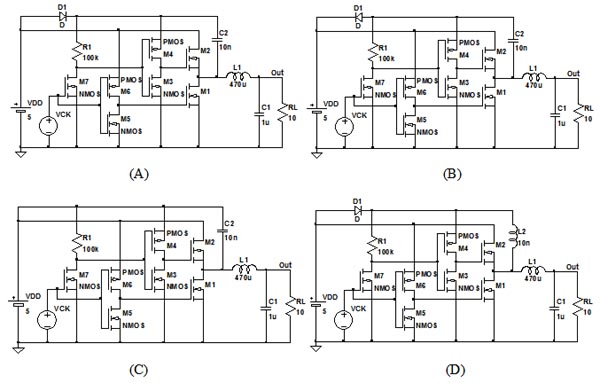

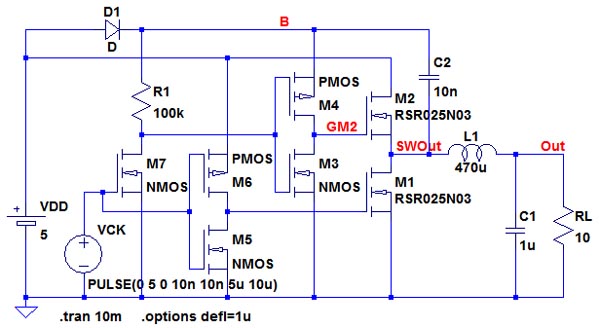

図1の(A)~(D)は,ブートストラップを使用したスイッチング電源の回路図です.出力MOSFETのM1とM2はともに4V駆動タイプのNchパワーMOSFETです.バッファーとして使用しているM3~M7のCMOSは10V以上の耐圧があるものとします.

スイッチング用の信号源は,VCKで,周波数100kHz,デューティ比50%の矩形波信号です.負荷として10Ωの抵抗が接続されています.電源電圧は5Vなので,正しく動作した場合,出力電圧は約2.5Vになります.そこで,(A)~(D)の中で出力電圧が約2.5Vになるのはどれでしょうか.

正しく動作して,出力電圧が約2.5Vになるのはどれ?

一般的にNchパワーMOSFETのほうが,同じ性能(オン抵抗)のPchパワーMOSFETより低価格で入手できます.そのため,スイッチング電源の出力MOSFETをすべてNchパワーMOSFETで構成する場合があります.ただし,スイッチング電源の出力MOSFETの上側(ハイサイド)に,NchパワーMOSFETを使用する場合,ゲート電圧が電源電圧よりも高くなるようにする必要があります.図1の(A)~(D)は,スイッチング出力信号を利用してM2のゲート電圧を高くする目的で,C2またはL2がスイッチング出力に接続されています.しかし,(A)~(D)の中で,正しく動作するのは一つだけです.M4ソースの電圧を,電源電圧よりも高くできるのはどれかを考えれば答えが分かります.

図1の(B)は,ダイオードの向きが左向きなため,M4ソースに電圧が供給されません.(C)は,M4のソースが電源に接続されているため,電源電圧よりも高くなることはできません.(D)は,電源電圧がD1およびL2を経由して直接出力に加わってしまいます.一方,(A)は,M1がONしたときにC2が充電され,M2がONしたとき,M4のソース電圧を引き上げます.するとM2のゲート電圧も電源電圧よりも高くなり,M2のソース電圧は,ほぼ電源電圧と同じになります.そのためスイッチング出力信号は5Vの振幅でデューティ比が50%となるので,Out端子の電圧は約2.5Vになります.つまり正解は(A)ということになります.

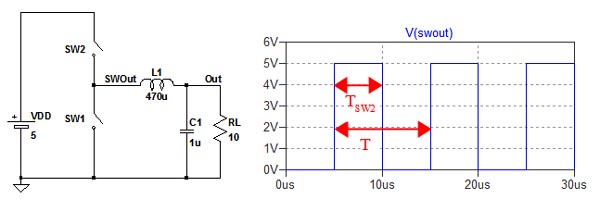

●降圧型スイッチング電源の動作

まず最初に,降圧型スイッチング電源の動作を簡単に解説します.図2が降圧型スイッチング電源の原理図です.SW1とSW2が交互にONすることで,SWOutの電圧は電源電圧と同じ振幅の矩形波になります.この信号をL1とC1のフィルタで平滑したものがOut端子の電圧になります.

Out端子の電圧はデューティ比に比例する.

SWOutの信号周期をTとし,SW2がONしている時間をTSW2とします.さらにデューティ比(D)を式1のように定義します.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

このとき,電源電圧をVDDとするとOut端子の電圧(VOut)は式2で表すことができます.

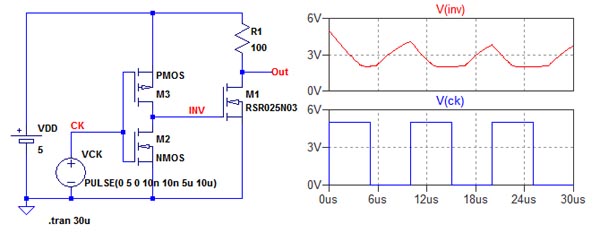

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

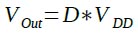

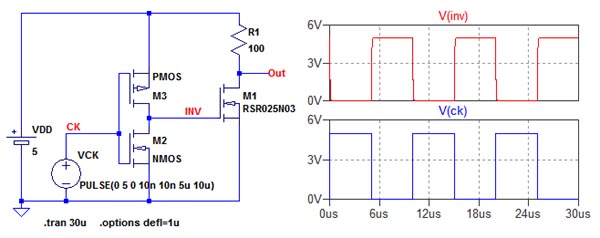

●デフォルトCMOSインバータの能力を確認する

MOSFETを使用した降圧型スイッチング電源のシミュレーションを行う前に,LTspiceで,MOSFETのデフォルト値の性能を確認します.図3の左は,4V駆動タイプのNchパワーMOSFET(M1:PSR025N03)をCMOSインバータを介して駆動する様子をシミュレーションするための回路です.M2がNch MOSFETで,M3がPch MOSFETです.モデルパラメータはLTspiceのデフォルト値となっています.VCKは100kHzで5Vの矩形波信号です.

図3の右がそのシミュレーション結果です.VCKの出力電圧(V(ck))とM1のゲート電圧(V(inv))をプロットしています.V(inv)は本来,V(ck)と逆位相の矩形波になるはずですが,かなりなまった波形となっています.これはインバータを構成しているM2とM3の電流駆動能力が足りず,M1のゲート容量をきちんと駆動できないためです.

M2とM3の駆動能力が足りず,ゲート電圧波形がなまっている.

●MOSFETの電流駆動能力を上げる

MOSFETの飽和特性領域のドレイン電流(ID)は式3で表されます.

・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・(3)

チャネル幅(W)およびチャネル長(L)は,MOSFETの大きさに関係する数値です.式3より,IDを大きくするにはWを大きくするか,Lを小さくすればよいことが分かります.LTspiceでは,LとWのデフォルト値は,共に100μmとなっています.そこで,図3の回路でLの値を1μmに変更し,電流駆動能力を100倍にしてシミュレーションしてみます.

図4の左が,そのシミュレーションをする回路で,Lのデフォルト値を1μmに変更するために「.options defl=1u」というコマンドを追加しています.図4の右がシミュレーション結果で,V(inv)はきちんとした矩形波になったことが分かります.なお,個々のMOSFETのLの値を設定するときは,モデル名の後ろに「L=xx」を書き足し,「NMOS L=1u」のようにします.

V(inv)はきちんとした矩形波になっている.

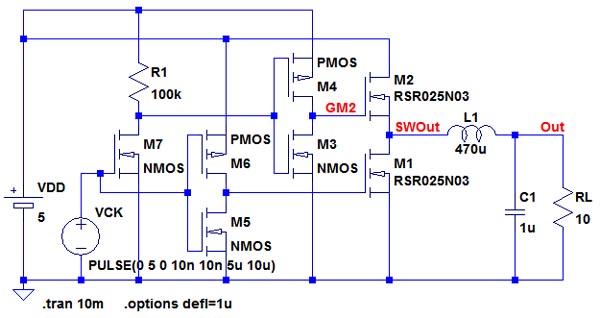

●NchパワーMOSFETを使用した降圧型スイッチング電源のシミュレーション

まず,図5のように,上側出力にNchパワーMOSFETを使用しブートストラップを使用しない回路のシミュレーションを行います.

上側出力にNchパワーMOSFETを使用しているがブートストラップは無い.

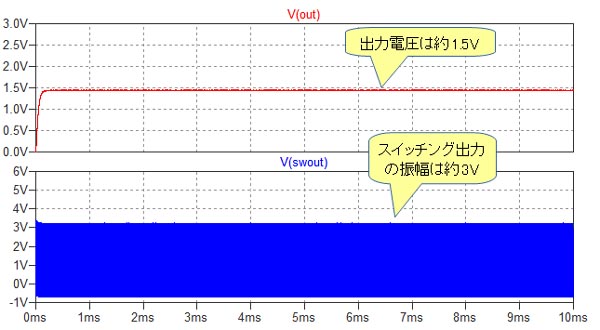

図6がその出力結果です.M2がソース・ホロアとして動作するため,SWOutの電圧振幅は3V程度しかありません.そのため,それを平滑したOUT端子の電圧は約1.5Vとなります.

スイッチング出力の振幅が小さく,出力電圧は約1.5V.

●ブートストラップを使用した降圧型スイッチング電源のシミュレーション

図7は,図5の回路にブートストラップを追加したものです.C2がブートストラップ・コンデンサと呼ばれ,B点の電圧を電源電圧よりも高くする働きをします.

C2がB点の電圧を電源電圧よりも高くする.

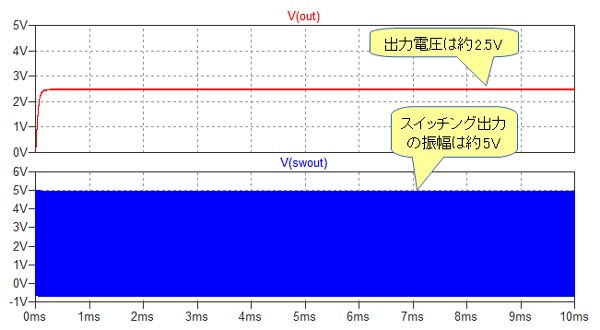

図8がそのシミュレーション結果です.スイッチング出力は,電源電圧とほぼ同じ約5Vとなっています.そのため,それを平滑したOut端子の電圧は約2.5Vとなっています.

スイッチング出力の振幅は5Vで,出力電圧は約2.5V.

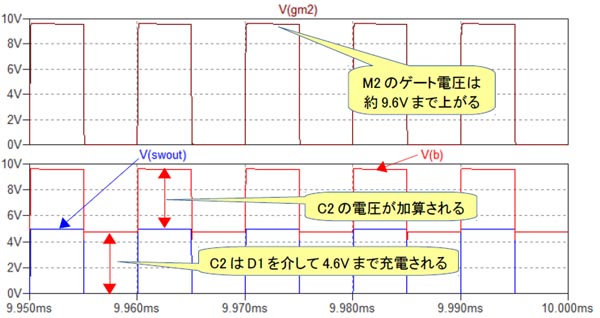

図9は,図8の時間軸を拡大して9.95msec~10mSsecとし,B点の電圧とM2のゲート電圧(V(GM2))をプロットしたものです.下段にV(SWOut)とB点の電圧(V(b))をプロットしています.

B点の電圧はSWOutの電圧にC2の電圧を加算したものになる.

M1がONして,V(SWOut)がGNDレベルのとき,C2はD1を介して充電されます.そのため,C2の両端電圧は,電源電圧からダイオードD1の順方向電圧を引いた値になります.

次に,M2がONしてV(SWOut)がハイレベルになると,B点の電圧はV(SWOut)の電圧にC2の両端電圧を加算したものになり,約9.6Vまで上昇します.B点にはPch MOSFETのM4のソースが接続されています.そのため,M4がONすると,M4のドレイン電圧はB点と同じ電圧になります.M4のドレインでM2のゲートを駆動しているため,M2のゲート電圧(V(GM2))もB点と同じ電圧になります.

図9の上段が,M2のゲート電圧V(GM2)をプロットしたものですが,ハイレベルは約9.6Vになっていることが分かります.M2のゲート電圧が電源電圧よりも高い9.6Vになるため,M2のソース電圧はほぼ電源電圧と同じ5Vとなります.そのため,V(SWOut)の振幅は約5Vとなり,出力電圧を2.5Vとすることができます.V(SWOut)の出力を利用して,V(SWOut)自身の電圧振幅を大きくしていることから,このような動作をブートストラップと呼びます.

このように,ブートストラップを使用するとNchパワーMOSFETだけを使用してスイッチング電源を構成することができます.参考までに,上手く動作しない図1の(B),(C),(D)の回路図ファイルも用意しましたので,皆さんでシミュレーションして見てください.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice2_047.zip

●データ・ファイル内容

CMOS_INV1.asc:図3の回路

CMOS_INV2.asc:図4の回路

NchSWreg.asc:図5の回路

bootSWreg_A.asc:図7の回路

bootSWreg_B.asc:図1(B)の回路

bootSWreg_C.asc:図1(C)の回路

bootSWreg_D.asc:図1(D)の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs