サンプル・ホールド回路で正しいスイッチの組み合わせはどれ?

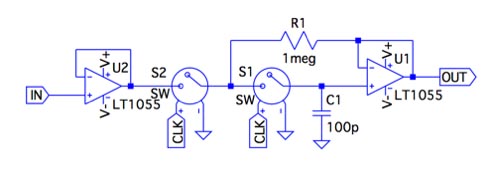

図1は,OPアンプを使ったサンプル・ホールド回路です.図1のスイッチ(S1,S2)のON/OFFにより,出力が入力に追随するトラック・モードと,C1で保持した入力電圧を出力するホールド・モードがあります.スイッチ(S1,S2)のON/OFFの組み合わせは,(a)~(d)の4種類となります.(a)~(d)の組み合わせの中で,ホールド・モードで,スイッチの漏れ電流の誤差が最小となる正しい組み合わせはどれでしょうか?

ホールド・モードで,スイッチの漏れ電流の誤差が最小となるスイッチ(S1,S2)の組み合わせは?

(b)S1がONでS2がOFF

(c)S1がOFFでS2がON

(d)S1がOFFでS2がOFF

図1のOPアンプのU1を使ったボルテージ・フォロワ回路は,非反転端子の電圧をゲイン1倍で出力します.U1の非反転端子には,C1のコンデンサがあり,S1のON/OFFにより,S1の左側の電圧を出力するときと,S1の右側にあるC1の電圧を出力する二つの状態があります.また,S2は,OPアンプのU2を使ったボルテージ・フォロワ回路の出力を,S1の左側に伝達するか否かの役割となります.R1の役割は,ホールド・モードのときOUT端子の出力電圧をS1の左側に印加することで,S1とS2の漏れ電流を抑える働きがあります.

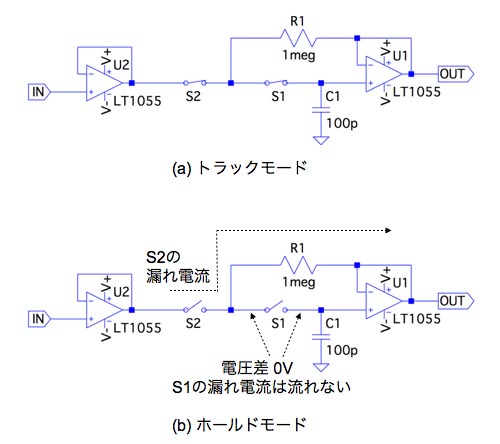

図1において,S2は入力信号をU2のボルテージ・フォロワ回路を介してS1へ伝達する働きです.なので,トラック・モードのとき,S2はONとなり,ホールド・モードのとき,S2はOFFとなります.S1はONのときにS2を通過した信号をU1のボルテージ・フォロワ回路へ伝達してトラック・モードとなり,OFFのとき,C1の電圧を出力するホールド・モードとなります.これらを図示したのが図2です.(a)がトラック・モード,(b)がホールド・モードのスイッチの状態です.

次にR1はホールド・モードのとき,OUT端子の出力電圧をS1の左側へ印加することにより,S1の両端の電圧が同じとなって,S1の漏れ電流が流れないようにします.またS2の漏れ電流は,R1を介してOPアンプU1の出力端子に流れるため,ホールド・モードの出力電圧に影響しません.以上より,図1の回路でスイッチの漏れ電流による誤差が最小となるホールド・モードは(d)となります.

(a)がトラック・モード,(b)がホールド・モードのスイッチの状態を示した.

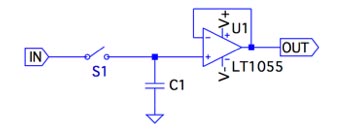

●サンプル・ホールド回路の基本形

図3は,スイッチS1,コンデンサC1,OPアンプU1のボルテージ・フォロワ回路を使った基本のサンプル・ホールド回路です.この回路の動作は,S1がONのときトラック・モードとなり,出力電圧は入力電圧に追随します.また,S1がOFFのときホールド・モードとなり,C1で保持した電圧を出力します.スイッチはアナログ・スイッチやJFET,MOSFETなどを用いて回路を構成します.

S1がONのときトラック・モード,S1がOFFのときホールド・モードとなる.

図3のサンプル・ホールド回路のトラック・モードとホールド・モードの誤差は次のようになります.

トラック・モードの誤差

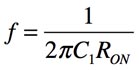

トラック・モードは,スイッチのオン抵抗をRONとすれば,RONとC1で決まる帯域幅は式1となり,信号の周波数成分が式1の帯域幅より高いものが含まれると,出力の追随誤差が大きくなります.また,ボルテージ・フォロワ回路はOPアンプのスルーレート以上の時間応答に追随できません.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

ホールド・モードの誤差

ホールド・モードは,C1で保持した電圧を,ボルテージ・フォロワ回路を介して出力します.このとき,C1の放電電流による電圧の時間変化「ΔVOUT/Δt」が誤差となり,これをドループ・レート(Droop Rate)と呼びます.コンデンサの放電電流は,OPアンプの入力バイアス電流やC1の漏れ電流,S1の漏れ電流です.OPアンプの入力バイアス電流は,JFET入力やCMOS OPアンプを用いることで少なくできます.C1の漏れ電流を小さくするには,絶縁抵抗が大きいコンデンサを選びます.S1の漏れ電流を小さくするには,スイッチの両端の電圧差をゼロにする回路の工夫で対策できます.

●サンプル・ホールド回路基本形のシミュレーション

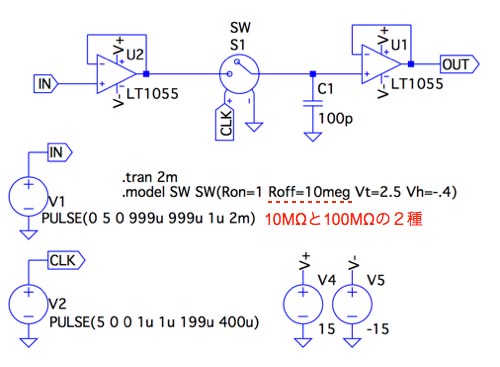

図4は,図3をシミュレーションする回路です.OPアンプはJFET入力のLT1055を使用し,C1を100pFとしました.図3との違いは,入力端子とスイッチの間にゲイン1倍のバッファとなるU2のボルテージ・フォロワ回路を入れました.スイッチはV2のクロック信号でON/OFFし,スレッショルド電圧が2.5V,オン抵抗が1Ωとしました.また,オフ抵抗は,10MΩと100MΩになるよう回路図のスイッチのモデルを編集して2回実行します.

スイッチはV2のクロック信号でON/OFFする.

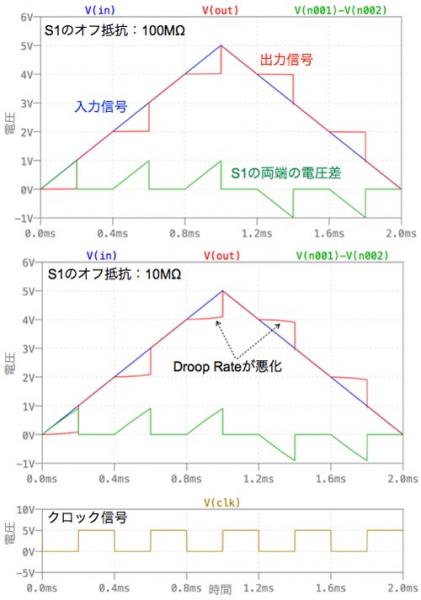

図5は,図4のシミュレーション結果です.S1のオフ抵抗が100MΩ,10MΩのときの結果を比べると,10MΩのときはホールド・モードのドループ・レートが悪化しています.原因は二つあります.一つ目は,S1の右側がC1で保持した電圧だからです.二つ目は,左側がU2のボルテージ・フォロワ回路で入力信号の電圧が印加されます.それで,S1の二つの端子に電圧差が生まれ,S1の漏れ電流がC1の放電電流となるからです.このため,C1の保持電圧が変化し,出力端子の電圧も変化します.

S1のオン抵抗は100MΩと10MΩの2種.

●スイッチの漏れ電流の影響を少なくするサンプル・ホールド回路

図4の基本のサンプル・ホールド回路は,図5のシミュレーション結果からも分かるとおり,スイッチの漏れ電流によるドループ・レートが大きくなることが欠点です.この対策として,図1のようにS2とR1を追加して回路を変更します.

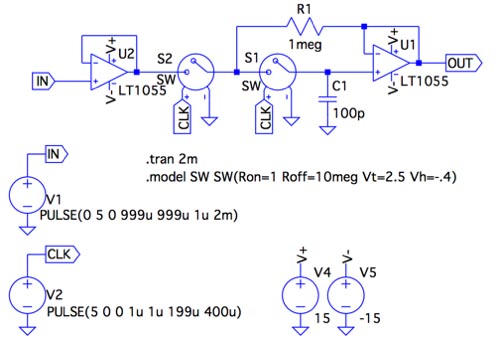

図1をシミュレーションする回路が図6です.S1,S2の二つのスイッチは図4の基本形と同じで,オフ抵抗は図5のシミュレーション結果でドループ・レートが悪化する10MΩとしました.

図1をシミュレーションする回路.

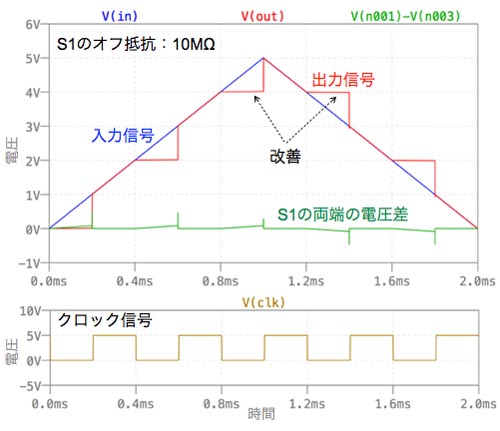

図7は,図6のシミュレーション結果です.S1の両端子の電圧差がゼロなので,漏れ電流が小さくなり,ドループ・レートが改善されているのがわかります.

S1のオン抵抗が10MΩのとき,ドループ・レートは改善している.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice2_046.zip

●データ・ファイル内容

SampleHold1.asc:図4の回路

SampleHold2.asc:図5の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs