CMOS論理回路の機能,正しいのはどれ?

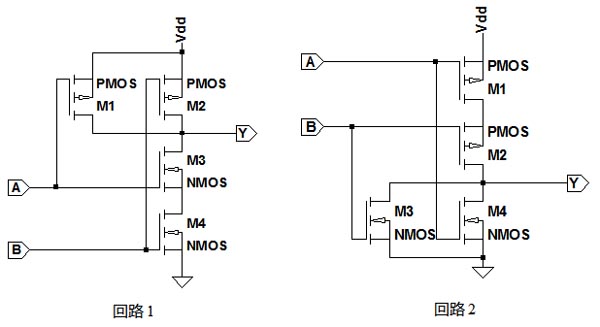

現在,さまざまところにデジタル技術が使われています.デジタル回路は1と0の組み合わせで演算を行います.その演算を行うのはトランジスタを組み合わせた論理回路です.図1の回路1と回路2は,MOSトランジスタを使用したCMOS基本論理回路です.電源電圧は5Vで,入力あるいは出力が5Vの状態が二進数の1に相当し,0Vの状態は0に相当します.回路1と回路2共に,入力(A)と(B)の二つの入力の論理演算結果が(Y)に出力されます.回路1と回路2の機能の説明として正しいのは,次の(A)~(D)のどれでしょう?

(C) 回路1がNAND回路,回路2がNOR回路 (D) 回路1がNOR回路,回路2がNAND回路

機能の説明として正しいのは?

図1において,NMOSはゲートに5Vが加わったときにONするスイッチとして働きます.一方PMOSはゲートがGNDレベルになったときにONするスイッチとして働きます.また,AND回路,NAND回路,OR回路,NOR回路の違いは次のようになります.

NAND回路:入力(A)と(B)共に1のときだけ出力(Y)が0になる[AND回路にNOT回路(反転)を組み合わせた回路]

OR回路:入力(A)か(B)のいずれかが1であれば出力(Y)が1になる

NOR回路:入力(A)か(B)のいずれかが1であれば出力(Y)が0になる[OR回路にNOT回路(反転)を組み合わせた回路]

これらを踏まえて動作を考えれば答えが分かります.

回路1は,M3とM4が直列に接続されているので,入力(A)と(B)が共に5V(1)になったとき,出力(Y)が0V(0)になります.それ以外では,出力(Y)は5V(1)になるため,回路1はNAND回路です.また,回路2はM3とM4が並列に接続されているため,入力(A)か(B)のいずれかが5V(1)になると出力(Y)が0V(0)になります.M1とM2が直列に接続されているため,出力(Y)が5V(1)になるのは,入力(A)と(B)が共に0V(0)のときだけです.これらの動作から回路2はNOR回路です.まとめると,回路1がNAND回路,回路2がNOR回路となります.つまり,正解は(C)ということになります.

●論理回路の基本要素

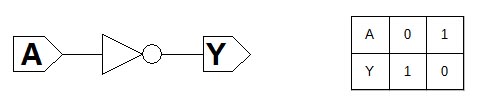

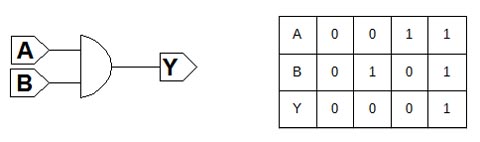

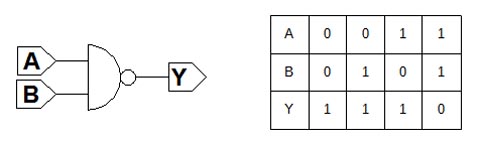

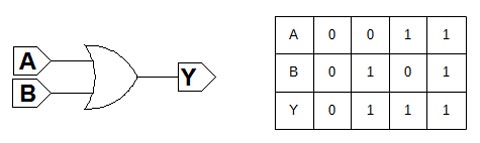

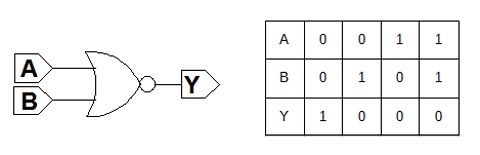

論理回路の基本要素はNOT回路,AND回路,OR回路の三つです.この三つの回路の組み合わせでさまざまな論理回路を構成することができます.MOS論理回路ではAND回路とOR回路の出力を反転したほうが回路構成が簡単になります.そのため,AND回路の出力を反転したNAND回路と,OR回路の出力を反転したNOR回路が主に使用されます.論理回路の入力と出力の関係を一覧表にまとめたものを真理値表と呼びます.図2にNOT回路,図3にAND回路,図4にNAND回路,図5にOR回路,図6にNOR回路の記号と真理値表を示します.

入力(A)を反転したものが出力(Y)となる.

入力(A)と(B)が共に1のとき,出力(Y)は1となる.

入力(A)と(B)が共に1のとき,出力(Y)は0となる.

入力(A)と(B)のどちらかが1であれば,出力(Y)は1となる.

入力(A)と(B)のどちらかが1であれば,出力(Y)は0となる.

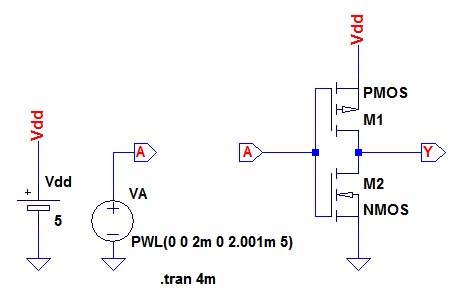

●CMOS NOT回路をLTspiceで確認する

図7は,CMOS NOT回路(インバータ)です.PMOSとNMOSのゲートを接続したものが入力(A)です.また,PMOSとNMOSのドレインが接続されたものが出力(Y)になります.入力(A)が0V(0)のときはM1のみがONし,M2はOFFします.そのため,出力(Y)は5V(1)になります.逆に入力(A)が5V(1)のときはM2のみがONし,M1はOFFします.そのため,出力(Y)は0V(0)になります.

この回路は,非常に消費電流が小さいという特徴があります.入力が1のときも0のときも,必ずどちらかのMOSFETがOFFしているため,電流が流れないからです.この回路がCMOS論理回路の基本になります.この回路をベースにAND回路やOR回路を作ることになります.ただし,NOT回路を基本とするため,AND回路やOR回路の出力論理が反転した,NAND回路やNOR回路として構築するほうが自然で,素子数も少なくなります.

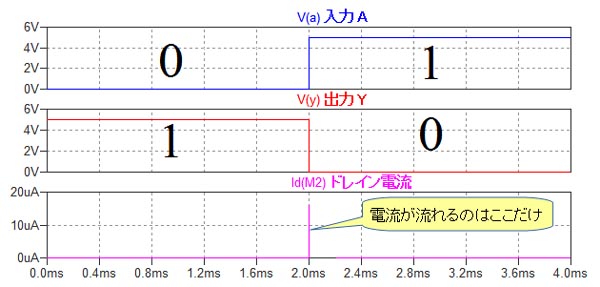

0Vから5Vに変化する信号を入力し,トランジェント解析を行う

図8が,図7のシミュレーション結果です.0Vのときに0で,5Vのときは1という論理を書き加えてあります.入力(A)の電圧(論理)に対して,出力(Y)の電圧(論理)は,反転した結果となっており,図2の真理値表と同じ結果となっていることが分かります.また,M2のドレイン電流が流れているのは,入力信号が遷移するときだけです.

図2の真理値表と同じ結果.電流が流れるのは遷移時のみ.

●CMOS NAND回路をLTspiceで確認する

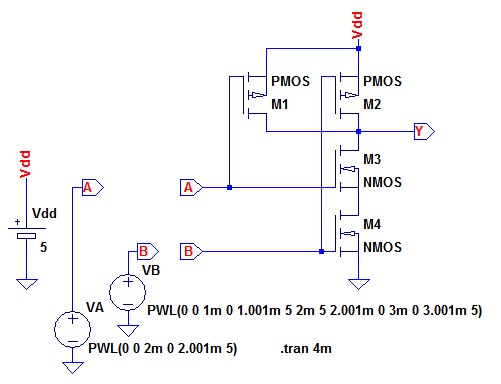

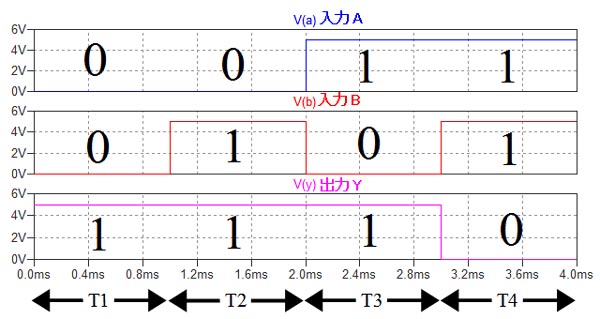

図9は,図1の回路1(CMOS NAND回路)をシミュレーションする回路図です.VAとVBが入力信号です.PWLを使用して,図4のNAND回路の真理値表の入力(A)と(B)に同様な信号を作っています.

PWLで2つの入力信号を作っていいる.

図10が図9のシュミレーション結果です.T1の期間はM1,M2が共にONし,M3,M4がOFFしているため,出力(Y)は5V(1)になります.T2の期間はM1がONで,M2がOFFしています.そして,M4がONしますが,直列接続されているM3がOFFしているため,やはり出力(Y)は,5V(1)になります.T3の期間はM1がOFFし,M2がONします.そして,M3がONしますが,直列接続されているM4がOFFしているため,出力(Y)は5V(1)になります.T4の期間はM1,M2がOFFします.そして,M3,M4共にONするため,出力(Y)は,0V(0)になります.

図10では,分かりやすいように,それぞれの出力に0と1を書き加えてありますが,この結果は,図4の真理値表と一致しており,この回路がNAND回路として動作していることが分かります.

図4の真理値表と同じ結果になっている.

●CMOS NOR回路をLTspiceで確認する

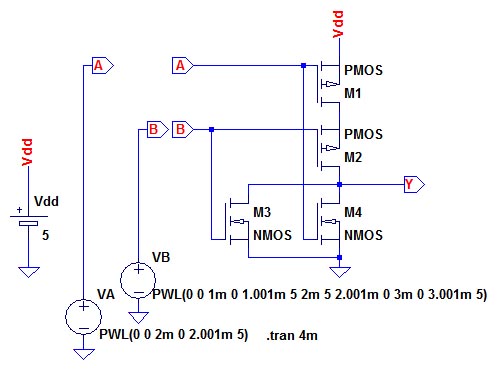

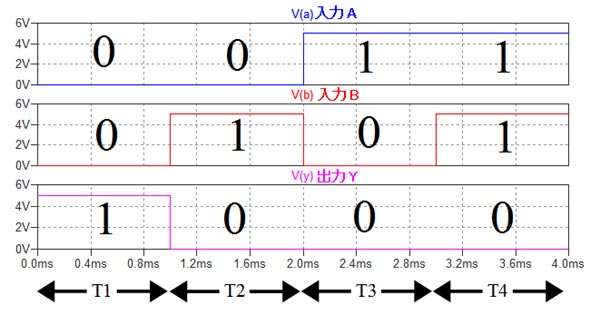

図11は,図1の回路2(CMOS NOR回路)をシミュレーションする回路図です.図9と同様にPWLで入力信号を作っています.

PWLで2つの入力信号を作っていいる.

図12が図11のシミュレーション結果です.T1の期間はM1,M2が共にONし,M3,M4がOFFしているため,出力(Y)は,5V(1)になります.T2の期間はM1がONで,M2がOFFしています.そして,M4はOFFですが,M3がONしているため,出力(Y)は,0V(0)になります.T3の期間はM2はONしますが,直列に接続されているM1はOFFしています.そして,M3はOFFですが,M4がONしているため,出力(Y)は,0V(0)になります.T4の期間はM1,M2がOFFします.そして,M3,M4共にONするため,出力(Y)は,0V(0)になります.

図12にも,それぞれの出力に0と1を書き加えてありますが,この結果は図6のNOR回路の真理値表と一致しており,この回路がNOR回路として動作していることが分かります.

図6の真理値表と同じ結果になっている.

●LTspiceで使えるデジタル素子

LTspiceでデジタル回路のシミュレーションを行う場合,図9~図11のような回路を組み合わせたデジタル回路を組んで行うこともできますが,規模が大きくなるとシミュレーション時間が大幅に長くなってしまいます.幸い,LTspiceにはデジタル回路のシミュレーションを高速に行うためのデジタル素子が用意されています.若干使い方にコツがありますので,最後にそのデジタル素子を使ったシミュレーションを紹介します.

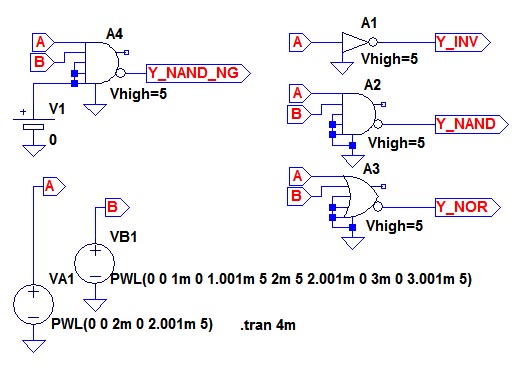

図13がデジタル素子を使ったシミュレーション用の回路図です.A1がNOT(インバータ)回路,A2がAND回路,A3がOR回路です.AND回路とOR回路は出力が二つあり,丸印がついた出力を使用した場合,NAND回路とNOR回路として使用できます.また,A4はA2の間違いやすい例として記載しています.A4は未使用入力端子をGNDでは無く0Vの電源に接続してあります.このようにGND以外に接続すると,未使用入力とは判断されず,0が入力されたものとしてシミュレーションされます.そのため,A2とA4のシミュレーション結果は異なったものとなりますので気を付けてください.

また,LTspiceのデジタル素子のデフォルトの論理振幅は1Vです.素子を右クリックして表れたウィンドウの中のValueの中に「Vhigh=5」と記入することで論理振幅を5Vとすることができます.

未使用入力端子はGNDに接続する.

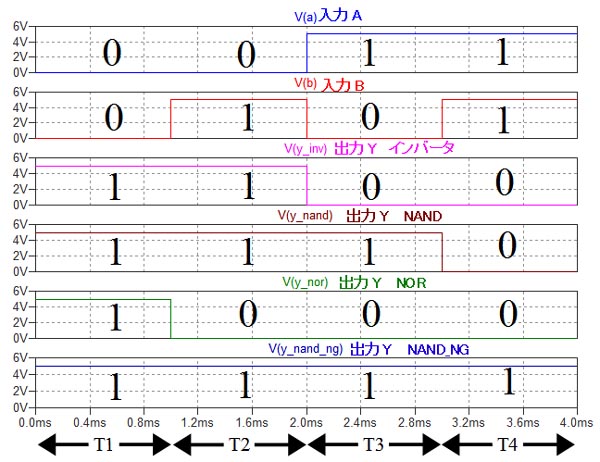

図14が図13のシミュレーション結果で,1段目が入力(A),2段目が入力(B),3段目がA1のNOT回路,4段目がA2のNAND回路,5段目がA3のNOR回路,6段目がA4のNAND回路の出力となります.A1,A2,A3の出力は,図8,図10,図12の出力と同じ結果になっています.

6段目(NAND_NG)の出力は全てのタイミングで1となっています.これは,図13のA4の入力(A)と入力(B)以外の未使用入力端子を0Vに接続したためです.NANDはすべての入力端子が1のときのみ出力が0になります.しかし,A4は,入力(A)と入力(B)以外の端子に0V(0)が入力されているため,出力は1のままとなります.

A2では,未使用入力端子がGNDに接続されています.この場合は未使用入力端子は存在しないものとして扱われるため,図9の2入力NAND回路と同じ正しいシミュレーション結果になります.

LTspiceのデジタル素子は,他にもDフリップ・フロップやエクスクルーシブORなどがあります.Componentウィンドウの中の[Digtal]フォルダの中に入っていますので,色々と試してみてください.

A1,A2,A3の出力は,図8,図10,図12の出力と同じ.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice2_043.zip

●データ・ファイル内容

NOT.asc:図7の回路

NAND.asc:図9の回路

NOR.asc:図11の回路

Digtal.asc:図13の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs